Manufacturing method of semiconductor assembly part capable of improving lattice defectin silicon build up crystal layer

A manufacturing method and technology of lattice defects, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as lattice defects, leakage current of shallow junction components, and reliability of component characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

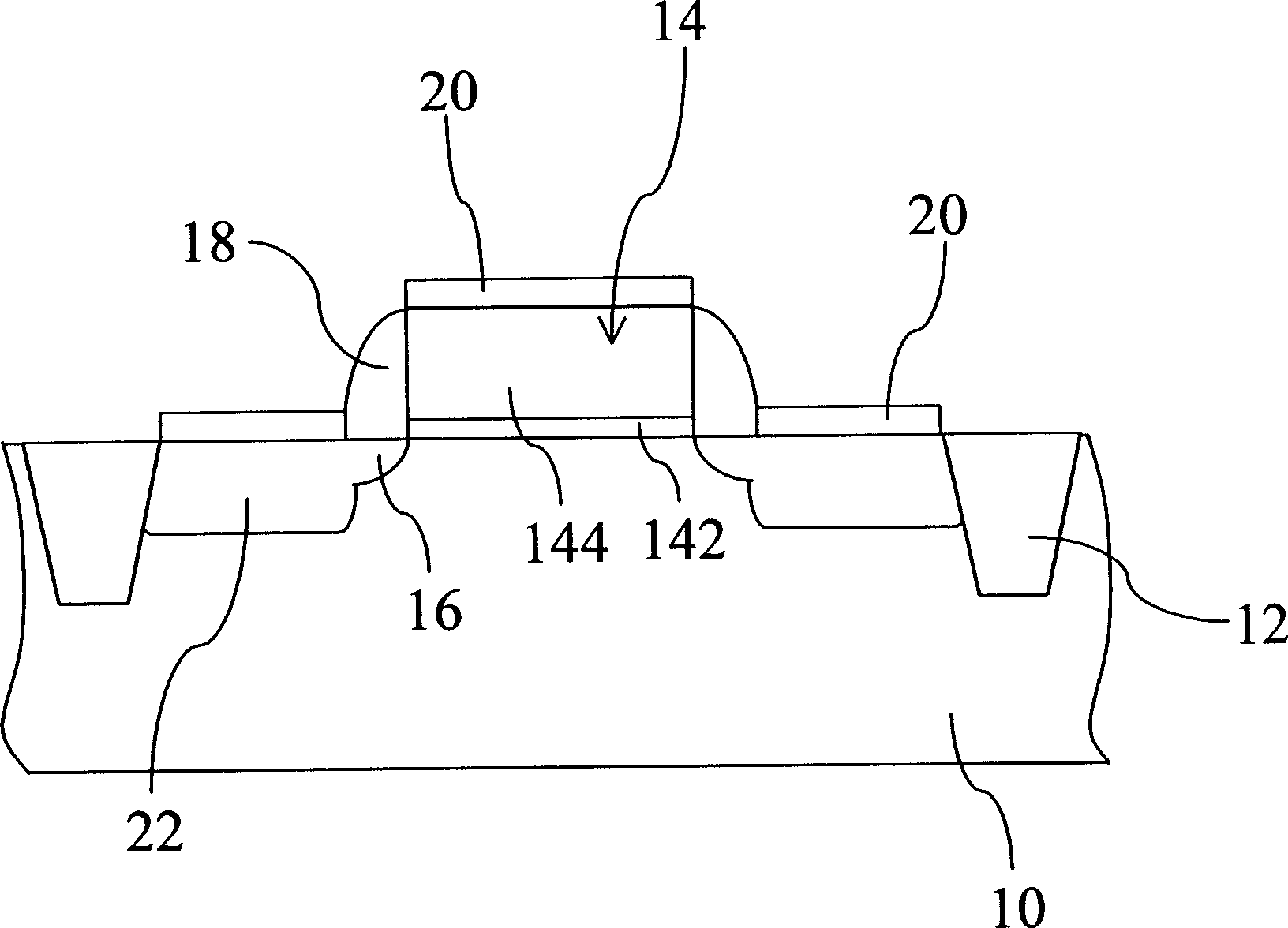

[0016] When the known technology grows a silicon epitaxial layer on the source / drain to form a raised source / drain structure, it is very easy to have lattice defects in the silicon epitaxial layer; and the semiconductor proposed by the present invention The component manufacturing method can solve the crystal lattice defects in the silicon epitaxy layer, so as to avoid the leakage current phenomenon of the silicon epitaxy layer at the shallow junction.

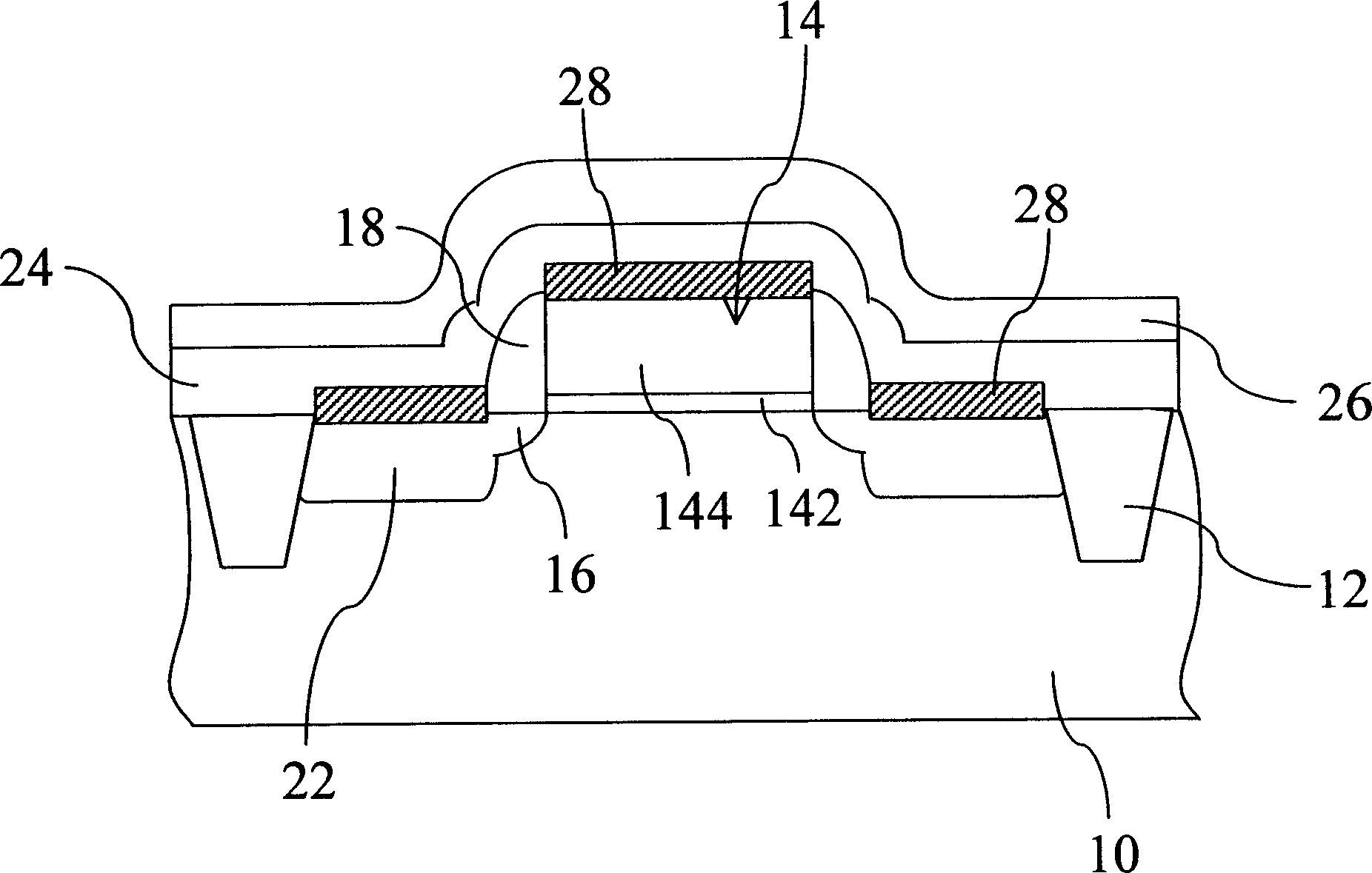

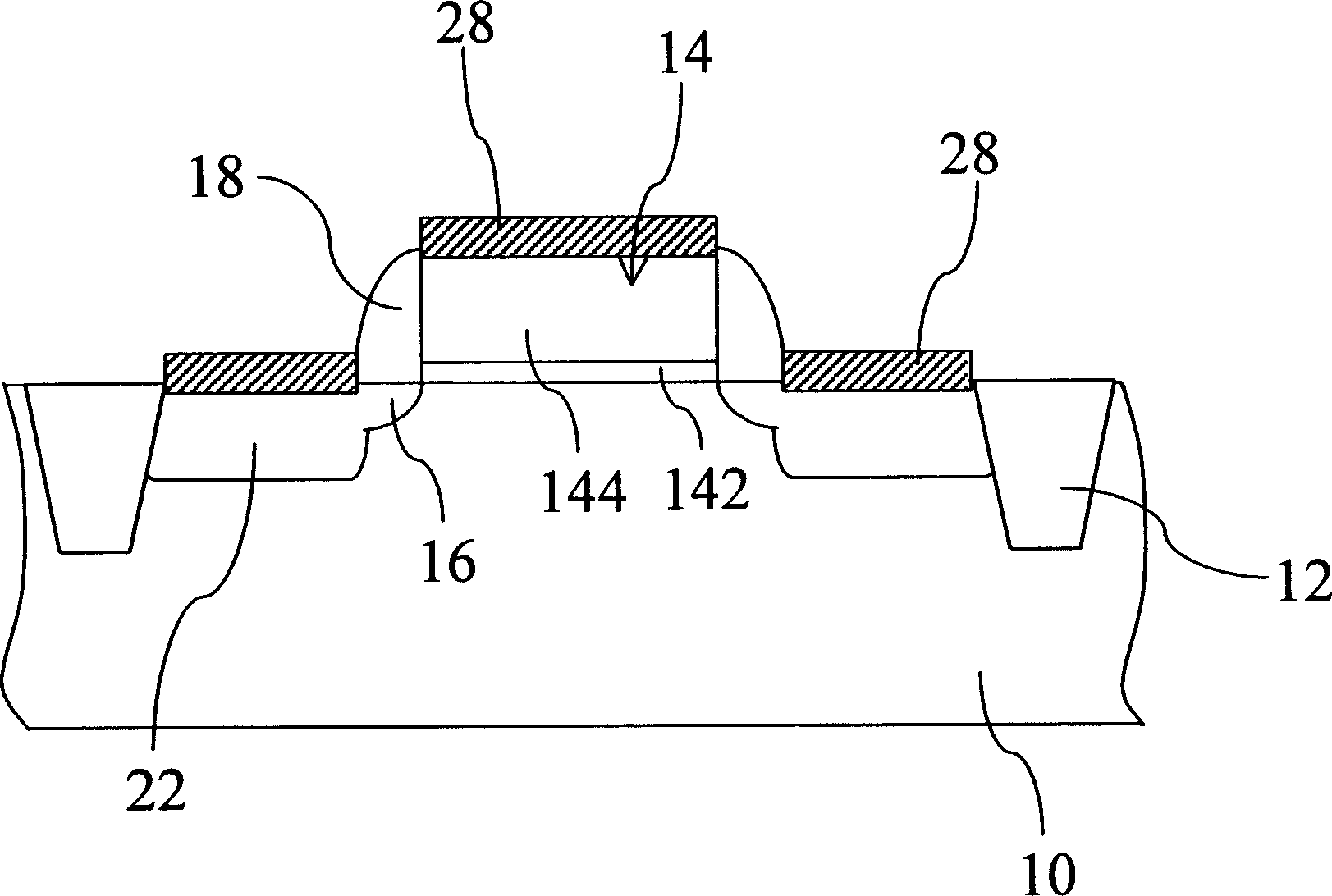

[0017] Figure 2(a) to Figure 2(f) For a preferred embodiment of the present invention, it is a cross-sectional view of each step of making a semiconductor assembly; as shown in the figure, the main manufacturing method of the present invention includes the following steps: first, as shown in Figure 2 (a), a semiconductor substrate 30 is provided , forming a shallow trench isolation region (shallow trench isolation, STI) 32 in the semiconductor substrate 30 to isolate active components and passive components in the semiconduct...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More