Method for reducing e-SiGe lattice imperfections in PMOS manufacturing process

A technology of lattice defect and manufacturing process, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as lattice defect and rework, so as to improve yield rate, reduce rework, shorten production cycle and production cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

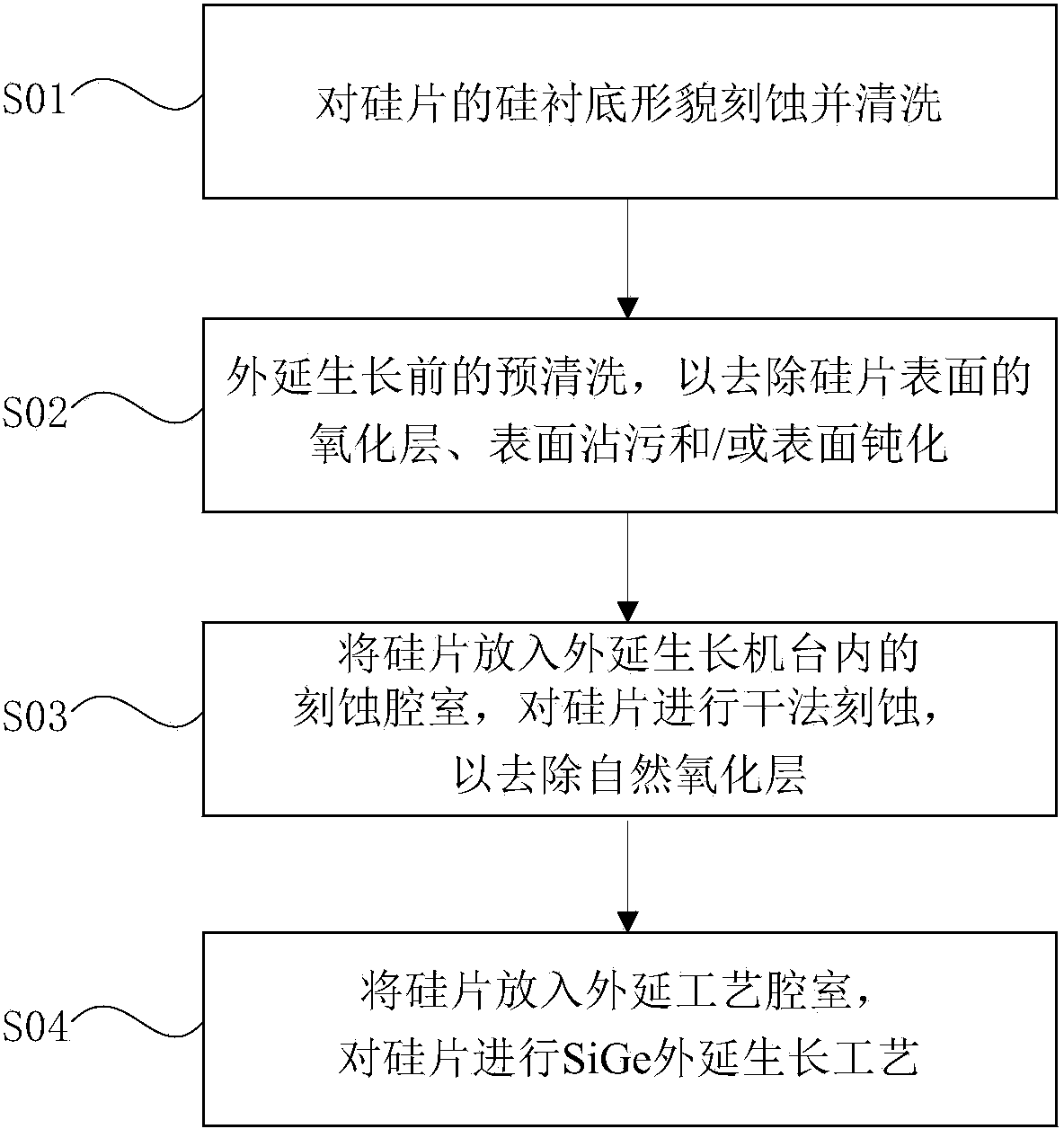

[0031] see figure 1 , the method for reducing e-SiGe lattice defects in the PMOS manufacturing process of this embodiment includes the following steps:

[0032] Step S01, etching and cleaning the topography of the silicon substrate of the silicon wafer. Among them, this step is completed on the etching machine, etching the silicon substrate to provide subsequent epitaxial growth of SiGe, cleaning is to remove the material remaining on the surface of the silicon wafer after etching, the cleaning medium can be deionized water, etc., this step It can be done by conventional means.

[0033] Step S02 , pre-cleaning before epitaxial growth, to remove the oxide layer, surface contamination and / or surface passivation on the surface of the silicon wafer. Among them, this step is completed on the cleaning machine, and the cleaning medium can be selected from DI-O 3 (Ozone-containing deionized water), SC-1 (Standard No. 1 solution, a mixed solution of ammonia, hydrogen peroxide and de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More