Patents

Literature

135 results about "In situ etching" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

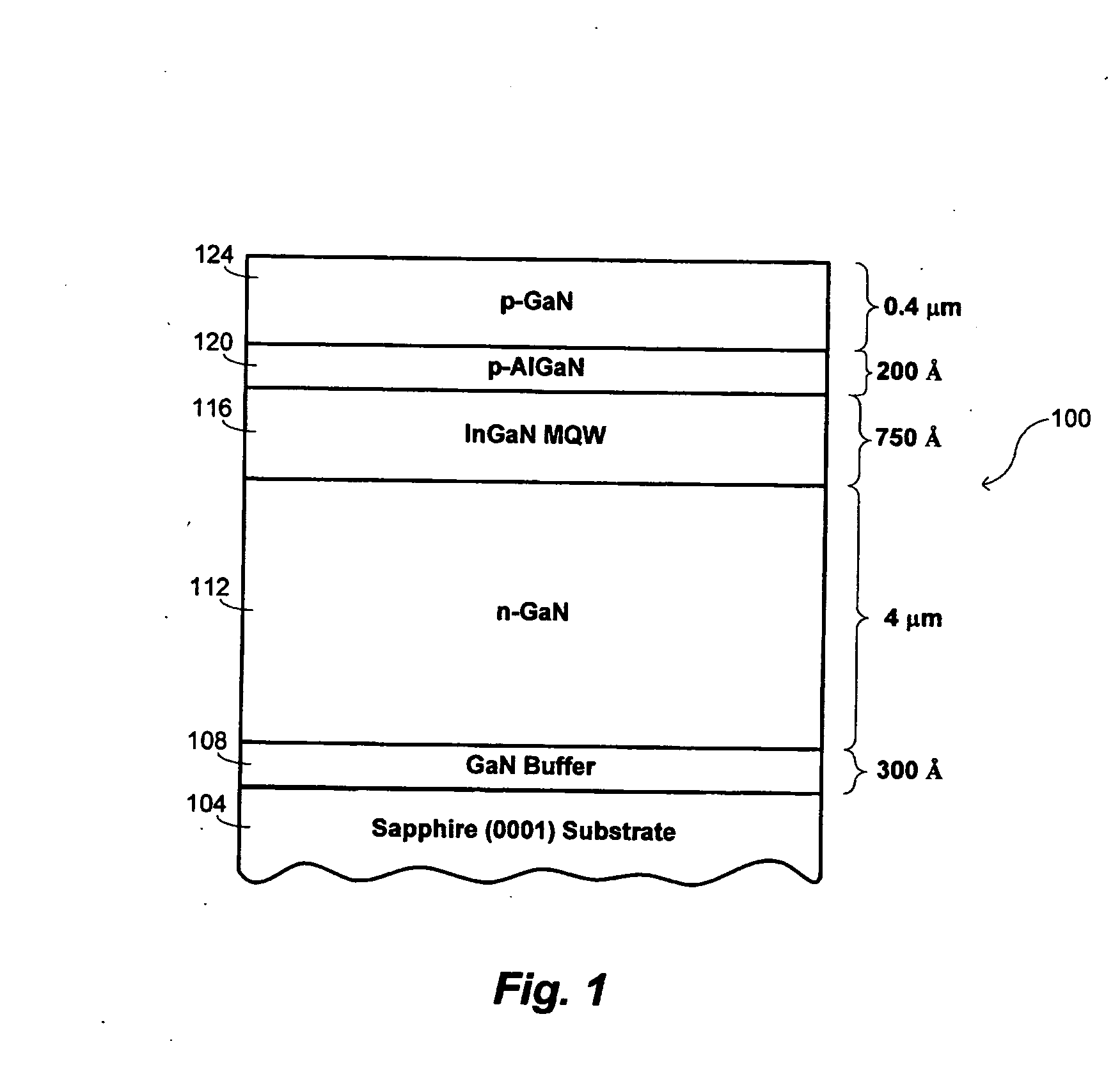

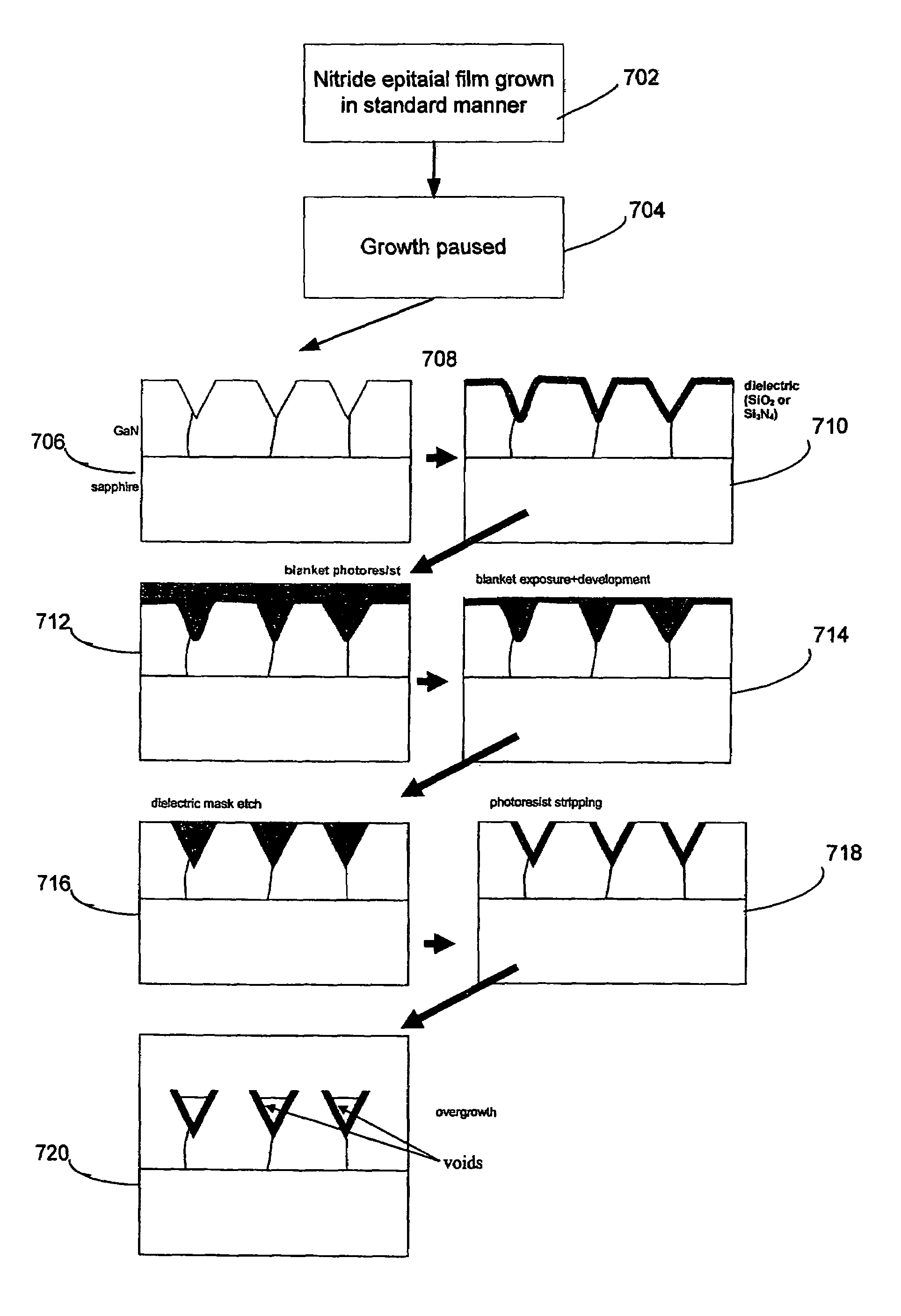

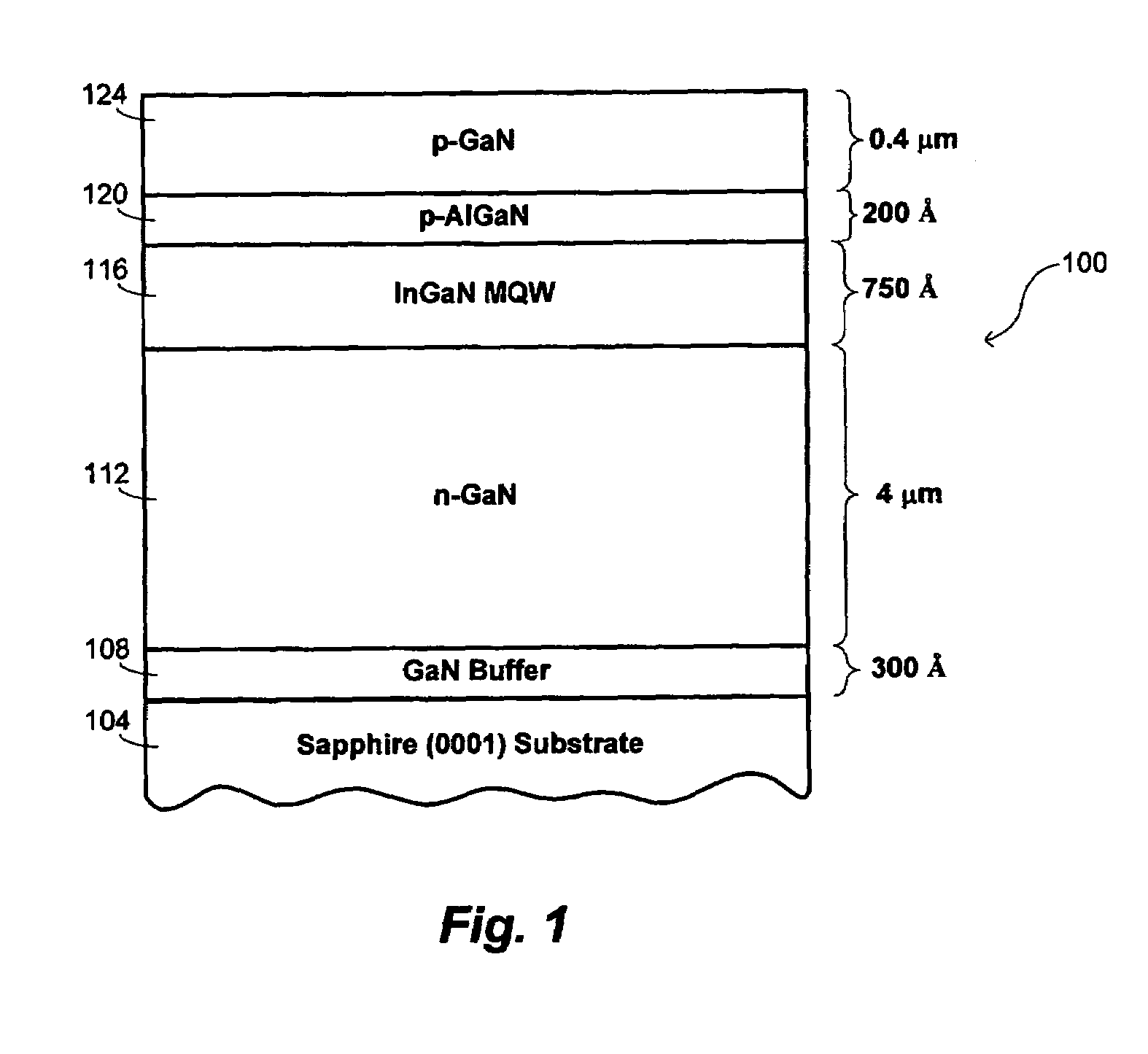

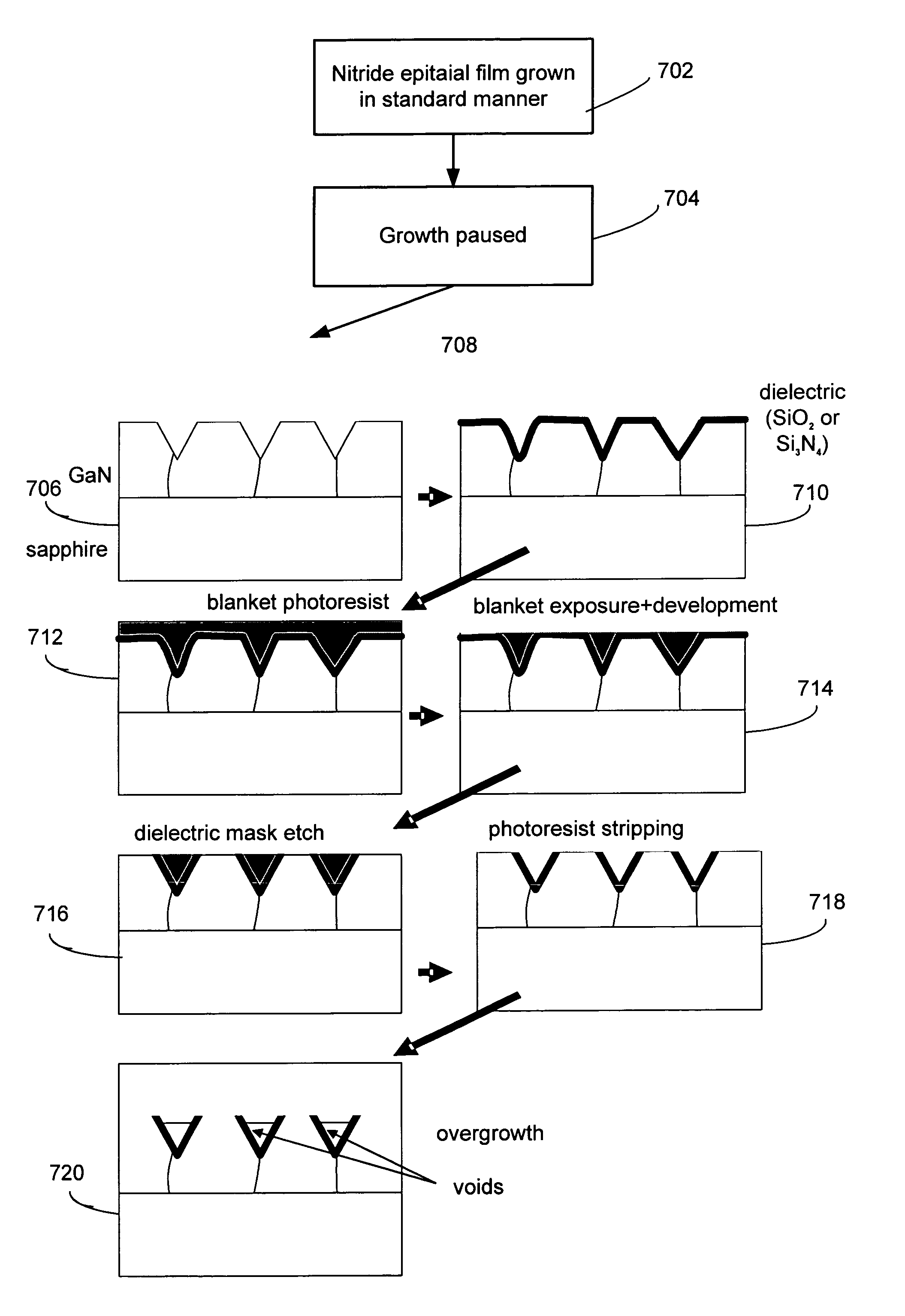

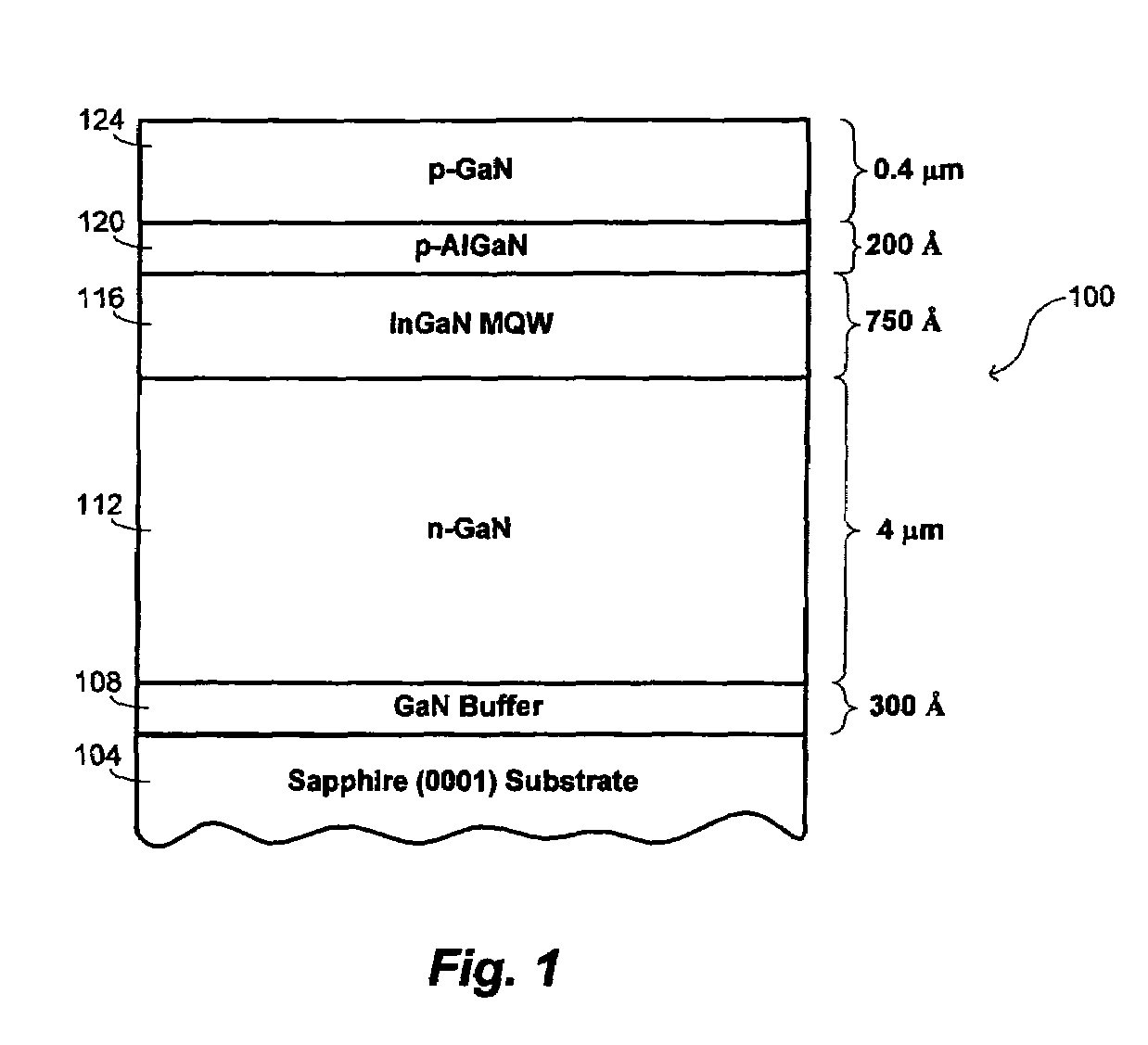

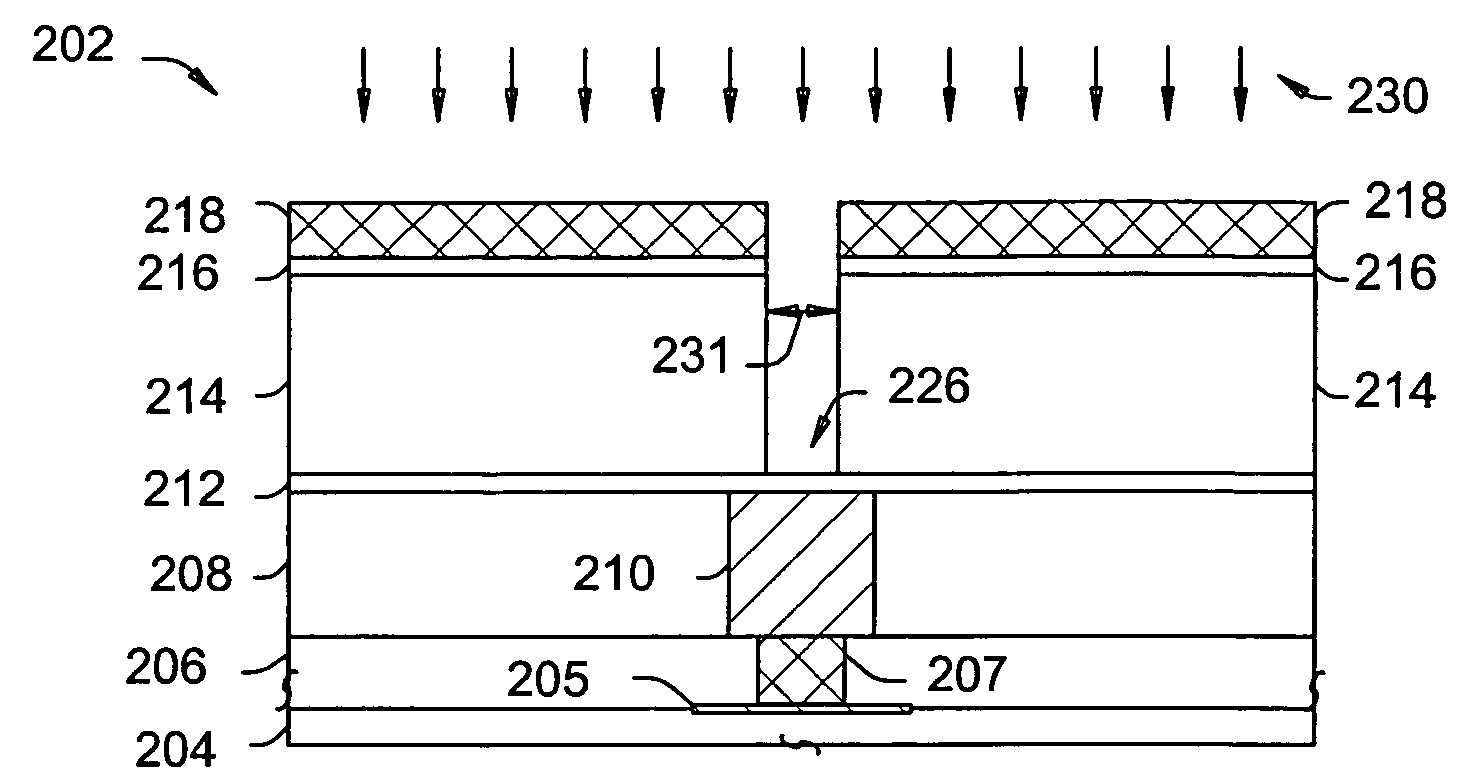

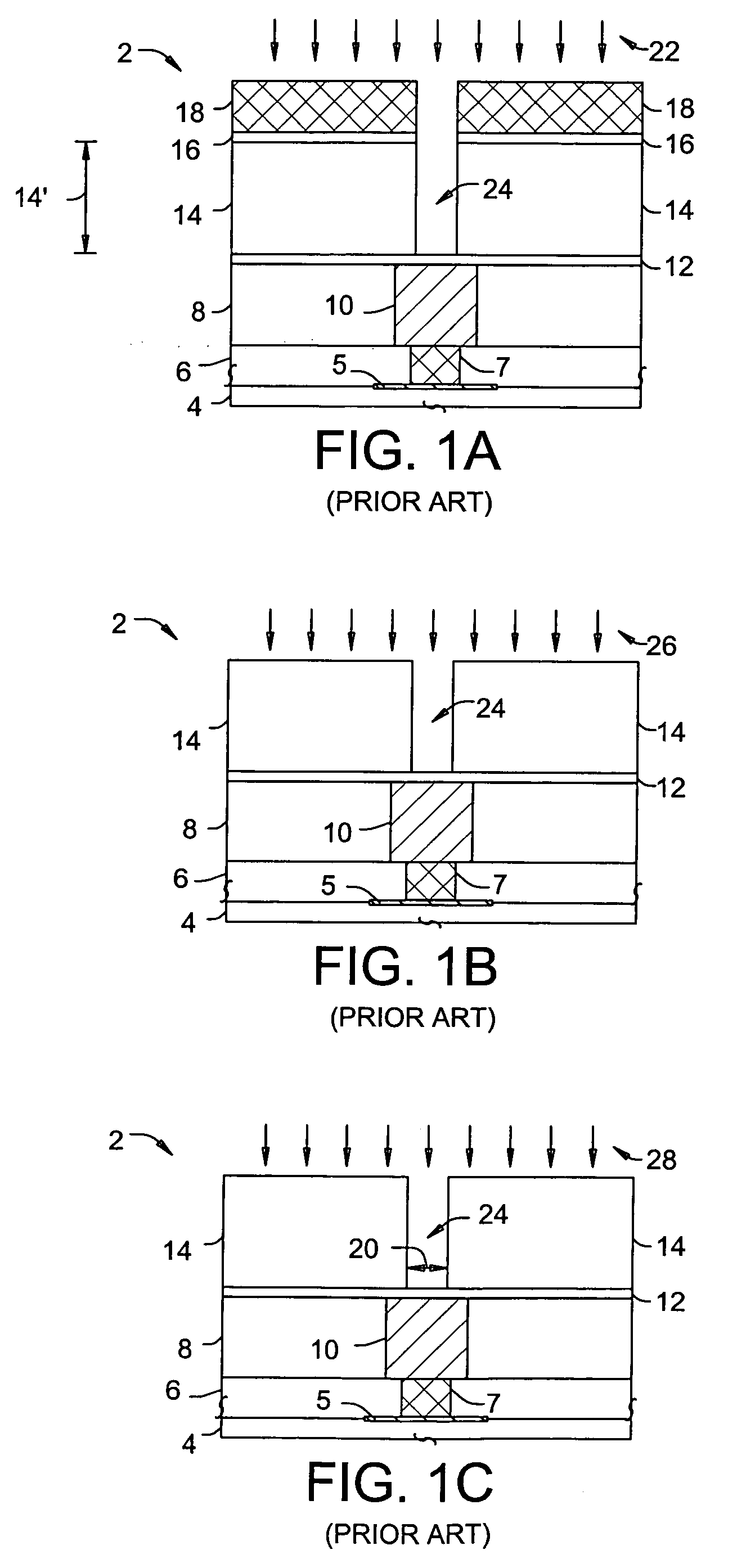

Dislocation-specific dielectric mask deposition and lateral epitaxial overgrowth to reduce dislocation density of nitride films

InactiveUS20070259464A1Inhibit threading of the lattice mismatchSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEtching

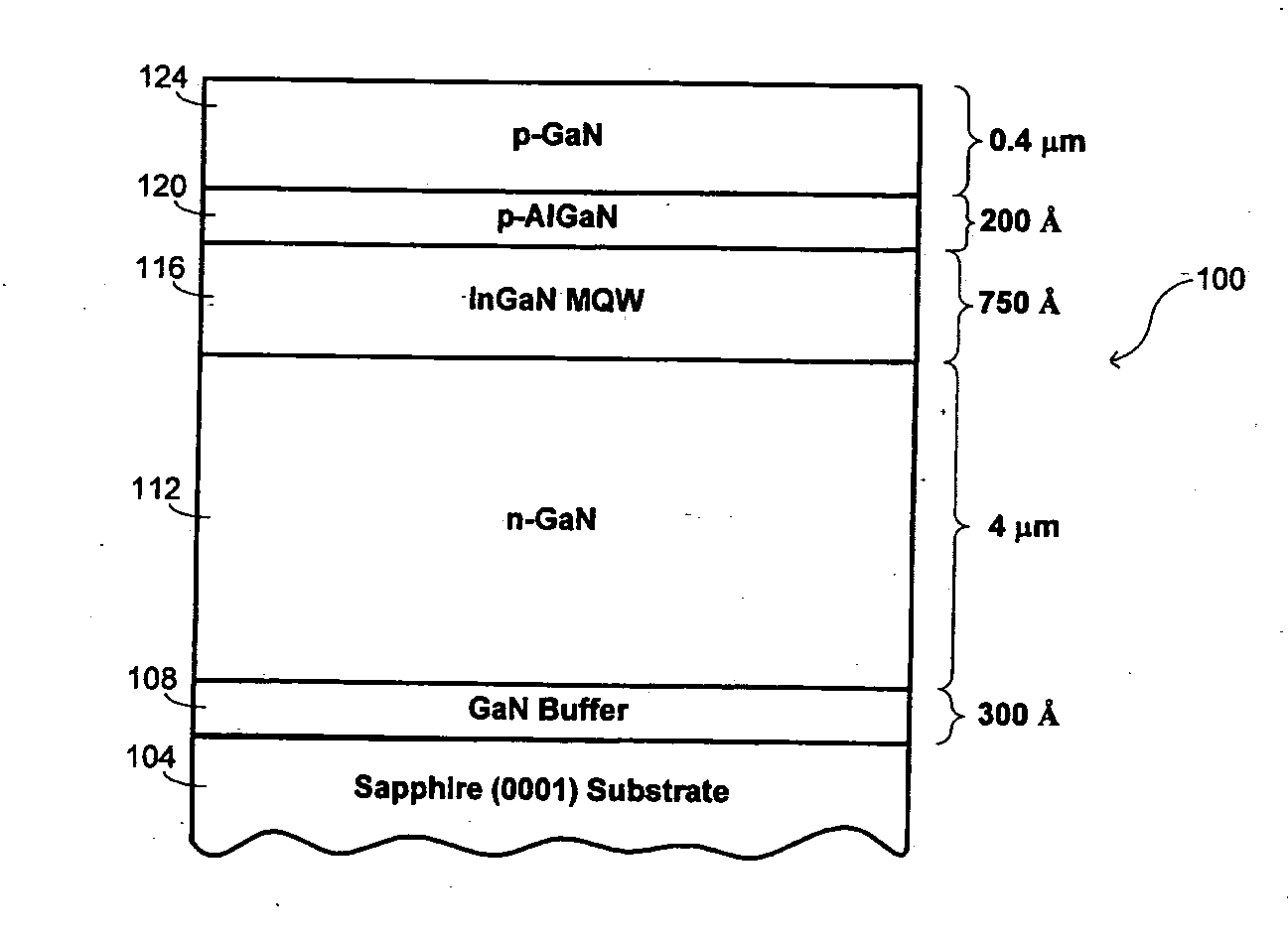

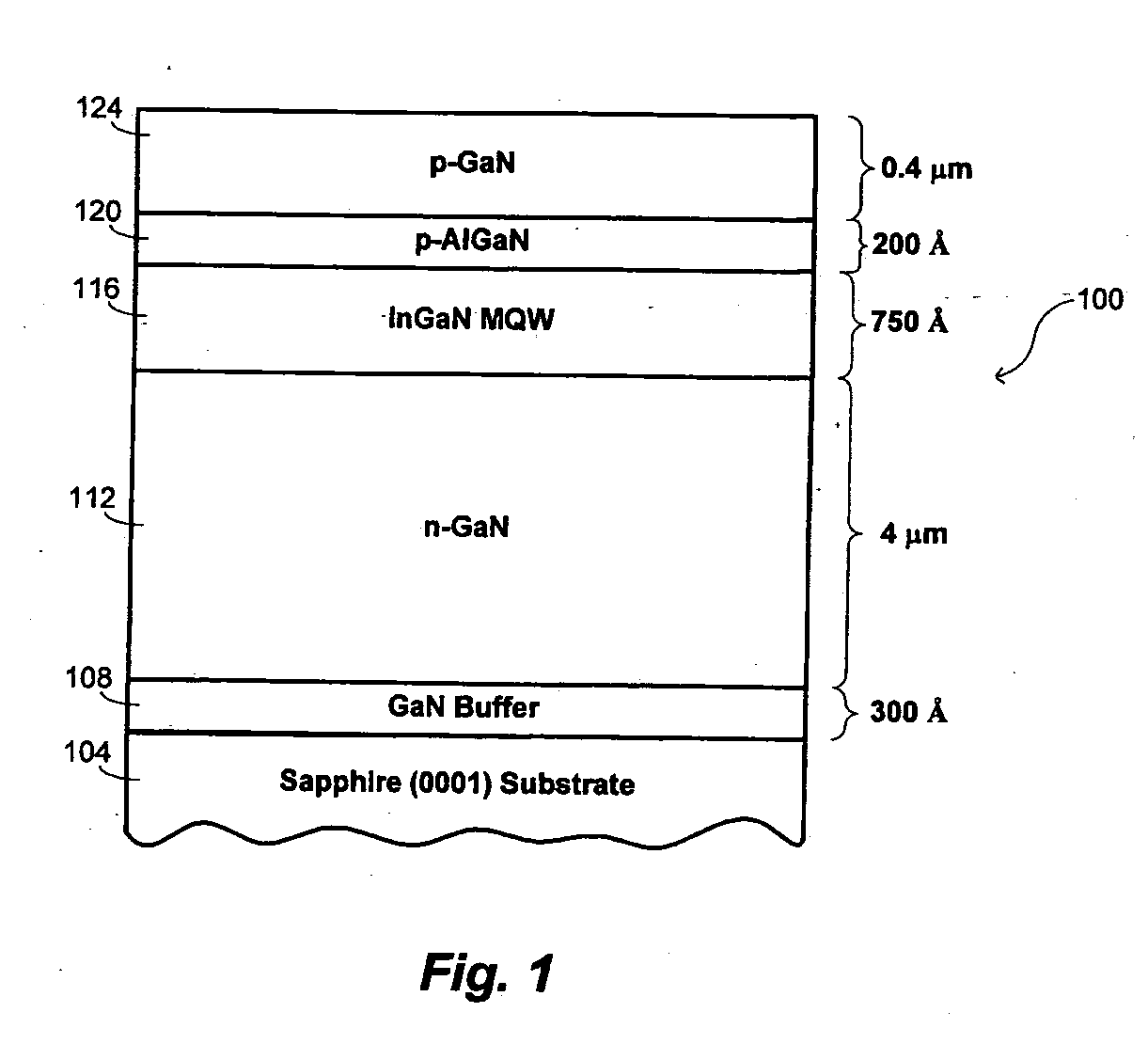

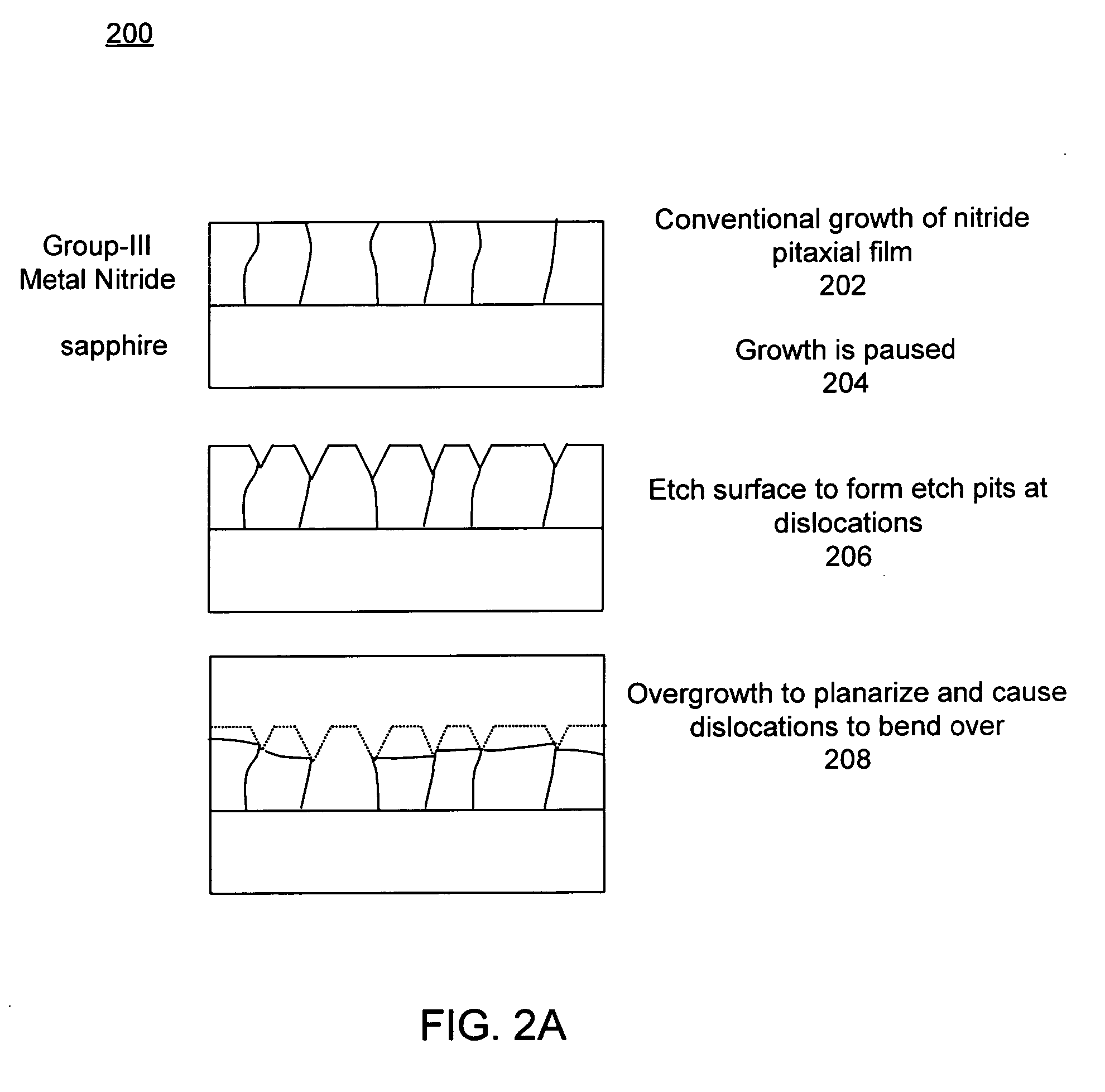

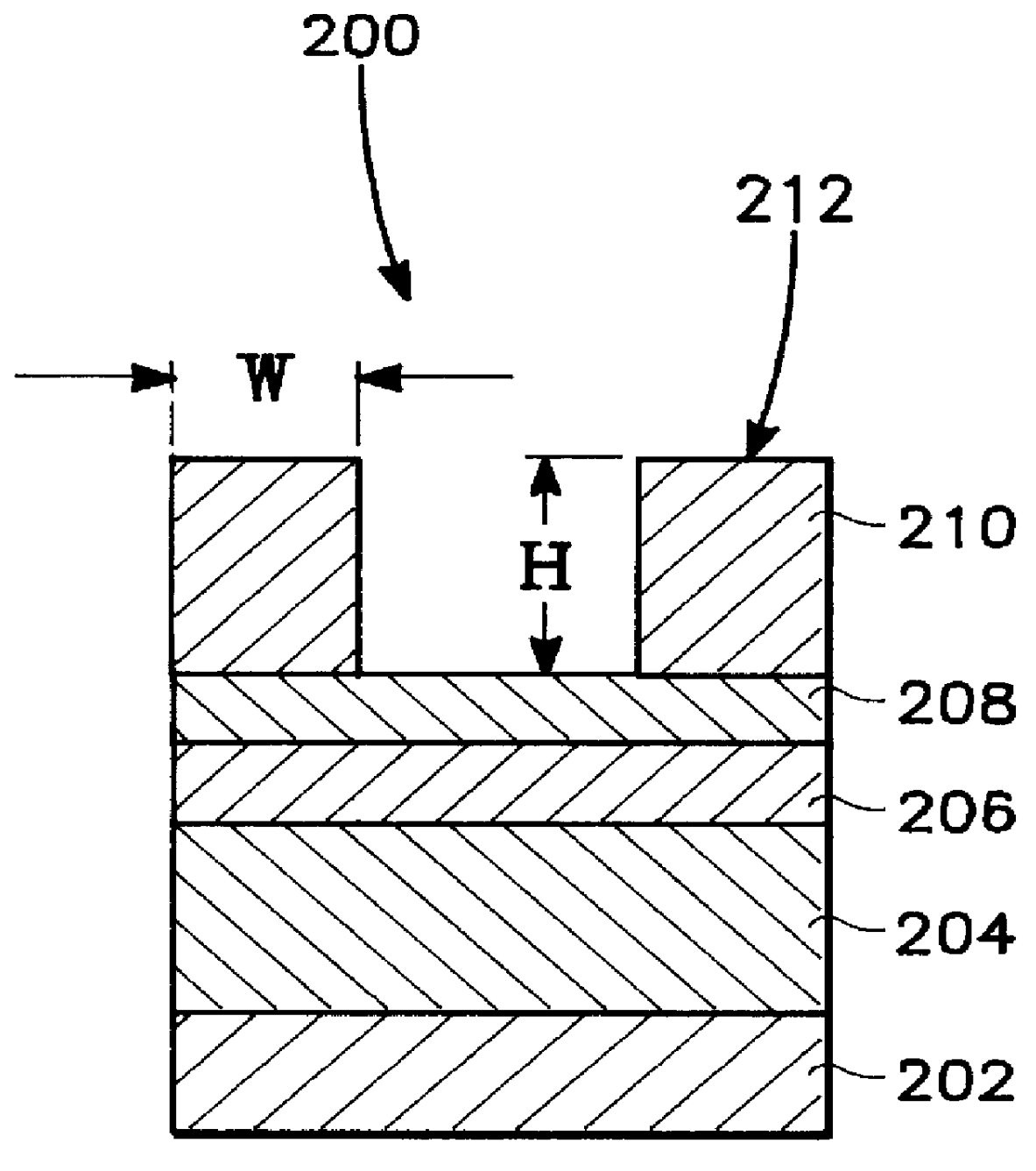

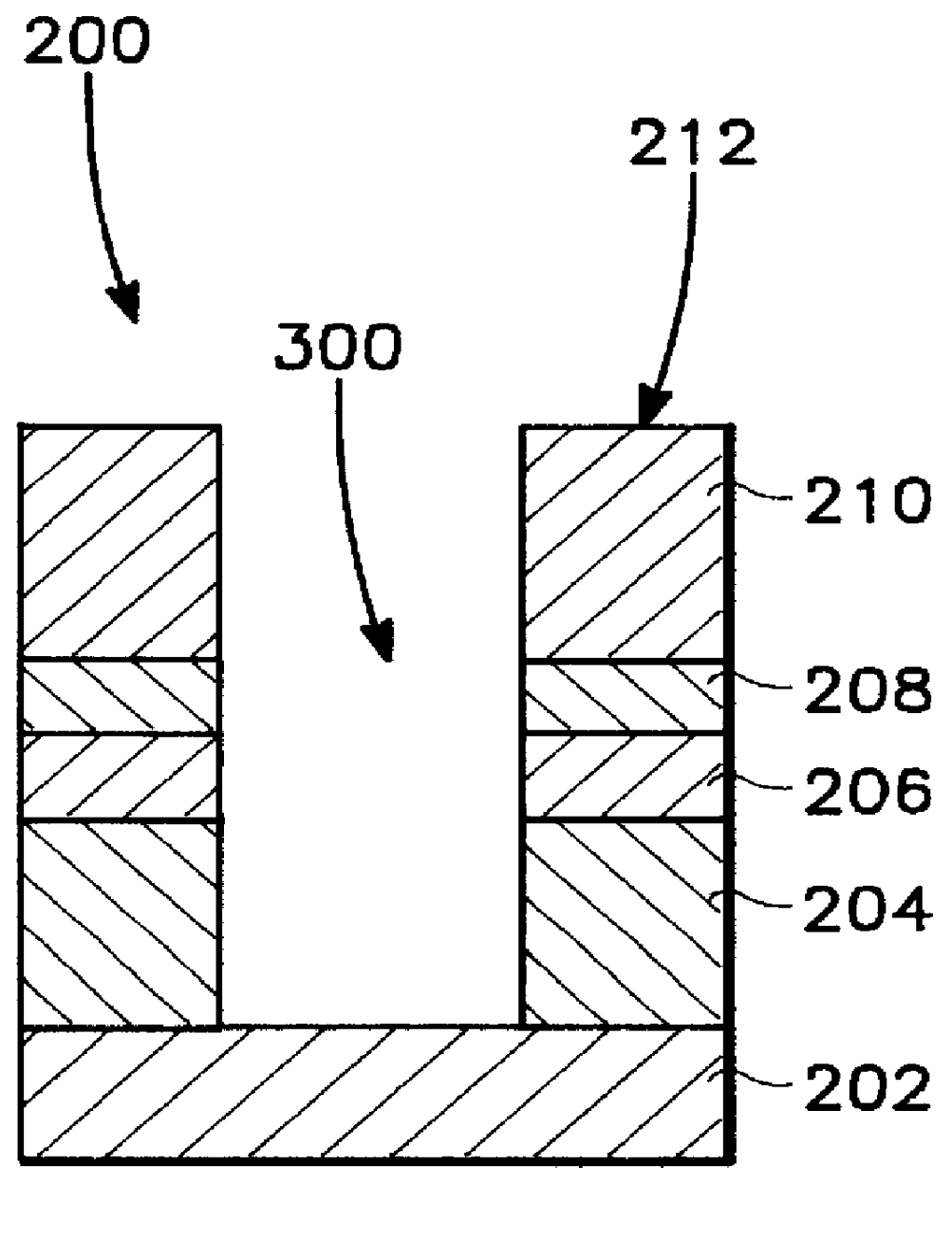

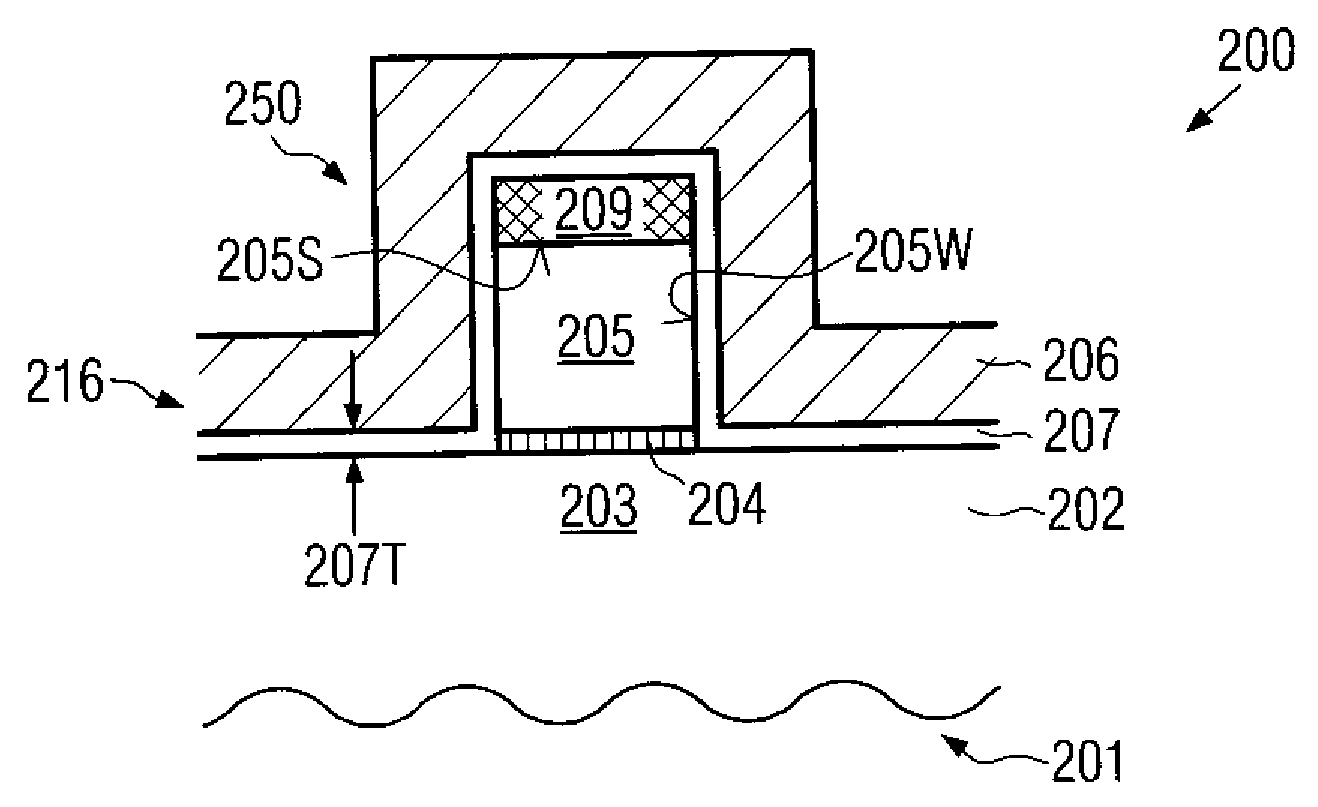

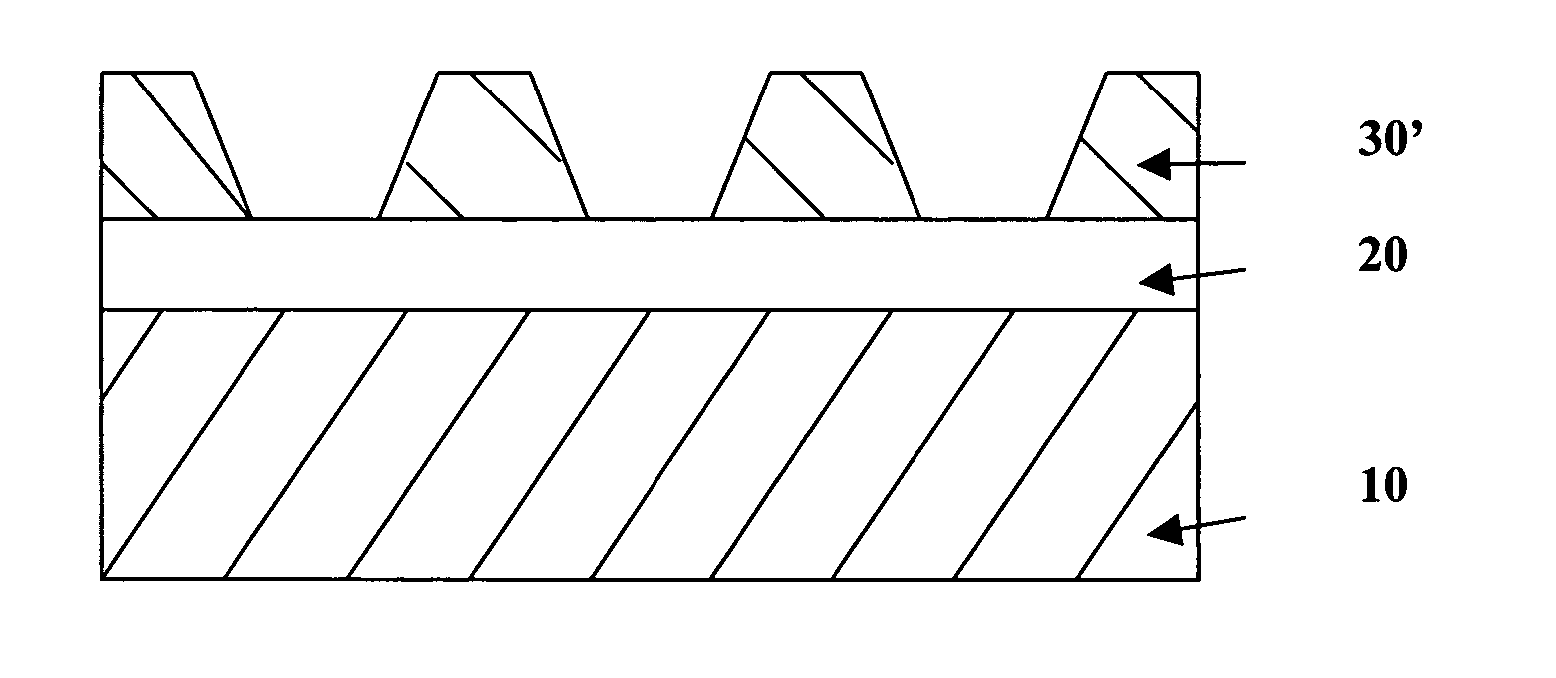

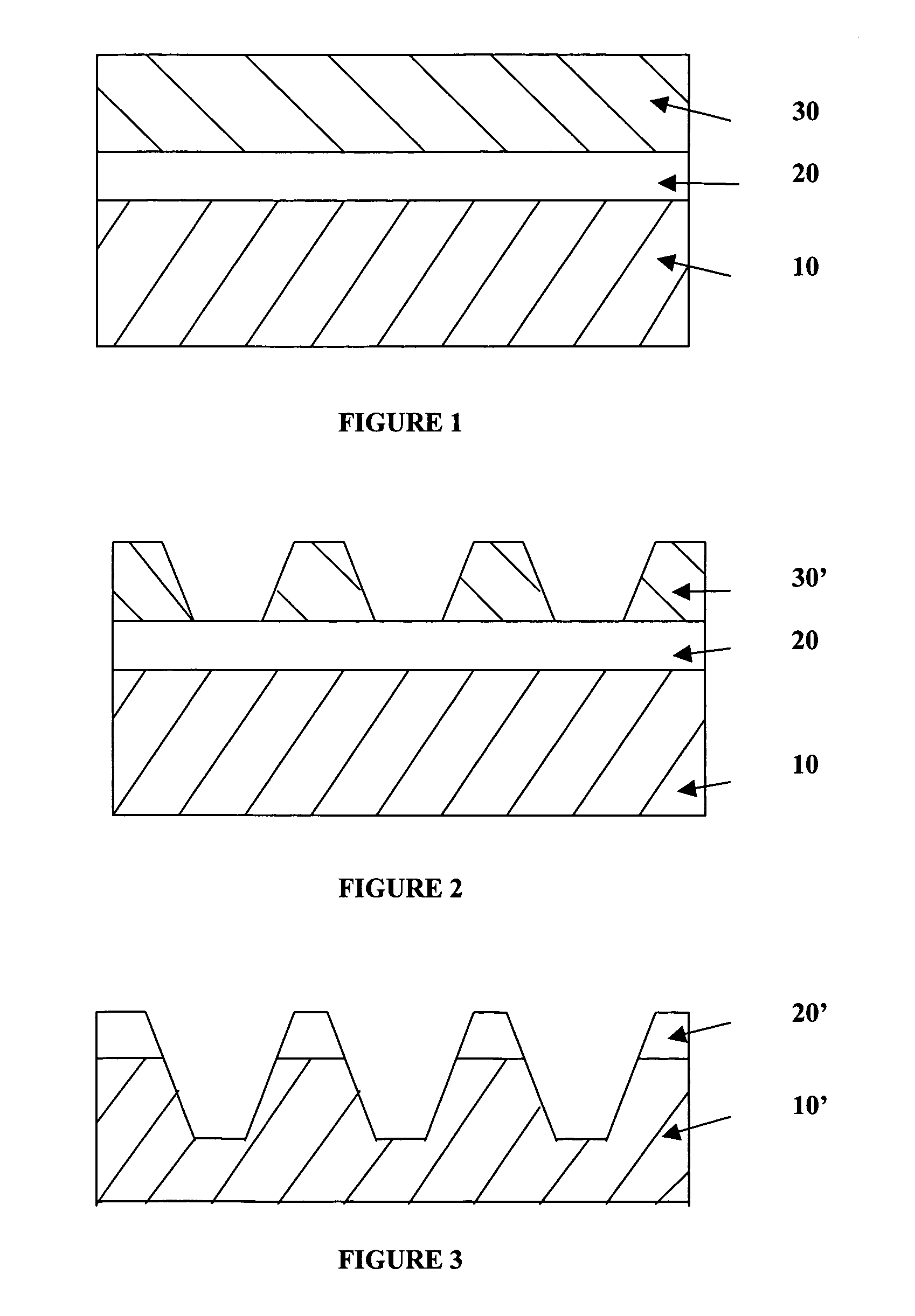

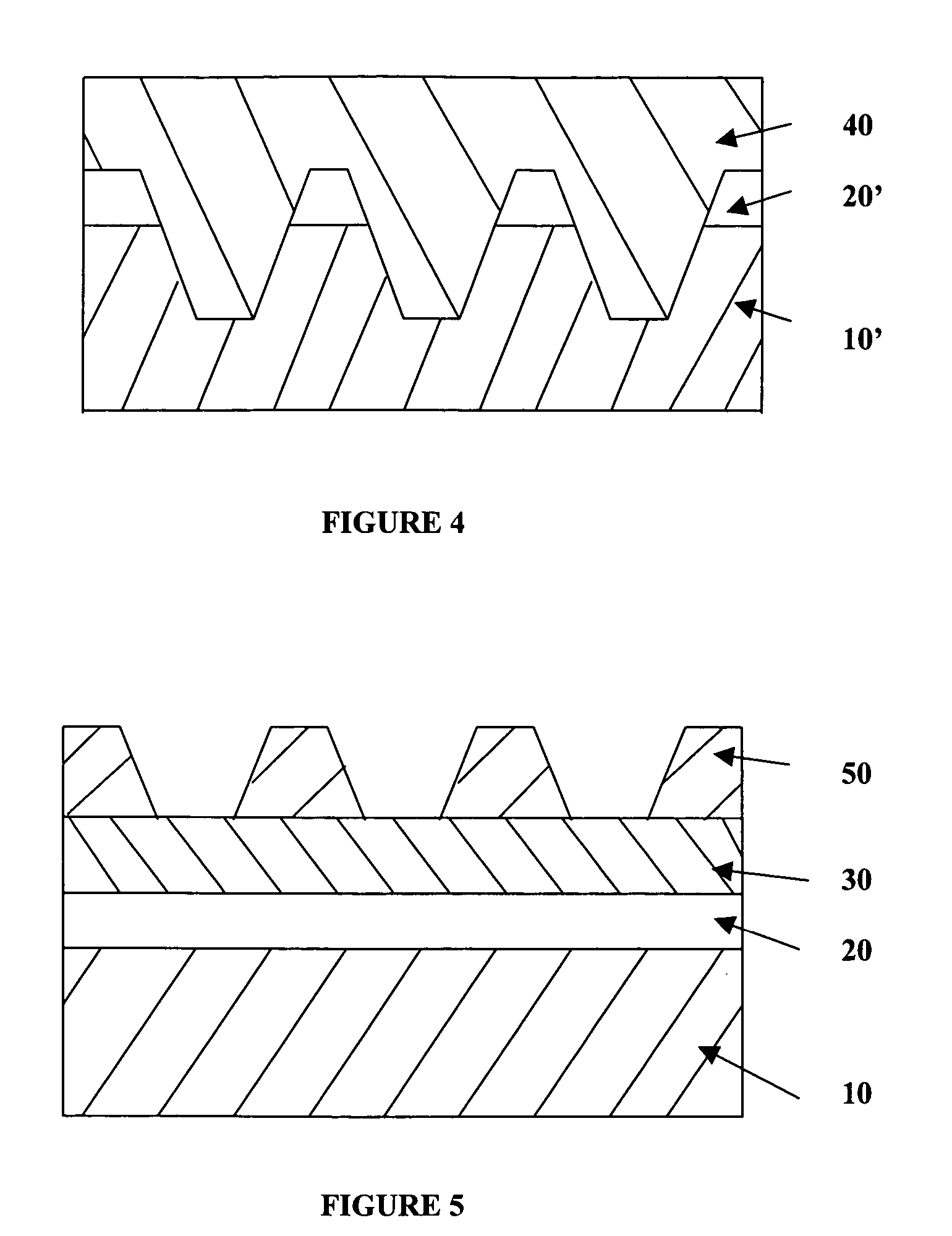

In accordance with the present invention, improved methods for reducing the dislocation density of nitride epitaxial films are provided. Specifically, an in-situ etch treatment is provided to preferentially etch the dislocations of the nitride epitaxial layer to prevent threading of the dislocations through the nitride epitaxial layer. Subsequent to etching of the dislocations, an epitaxial layer overgrowth is performed. In certain embodiments, the etching of the dislocations occurs simultaneously with growth of the epitaxial layer. In other embodiments, a dielectric mask is deposited within the etch pits formed at the dislocations prior to the epitaxial layer overgrowth.

Owner:APPLIED MATERIALS INC

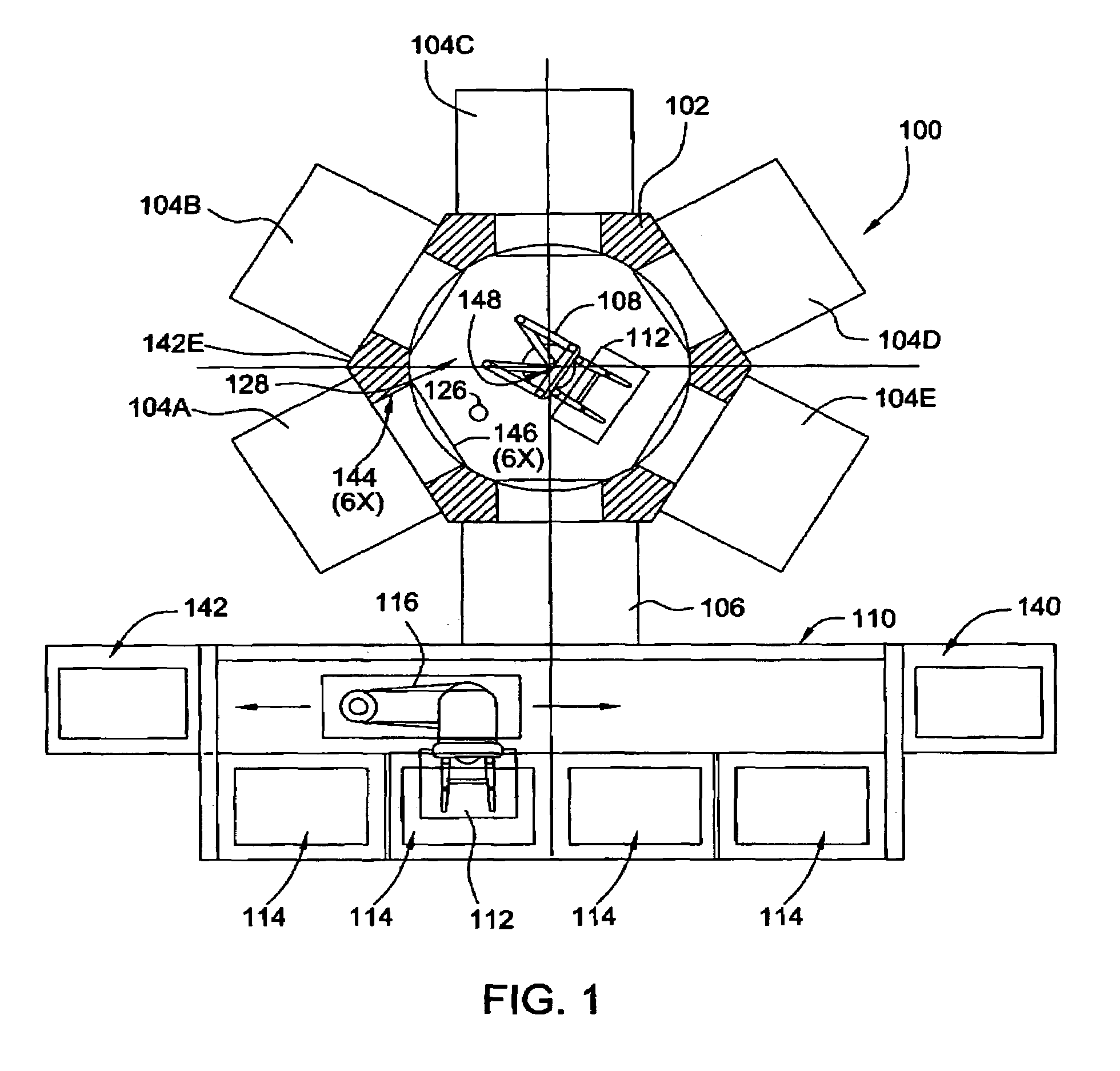

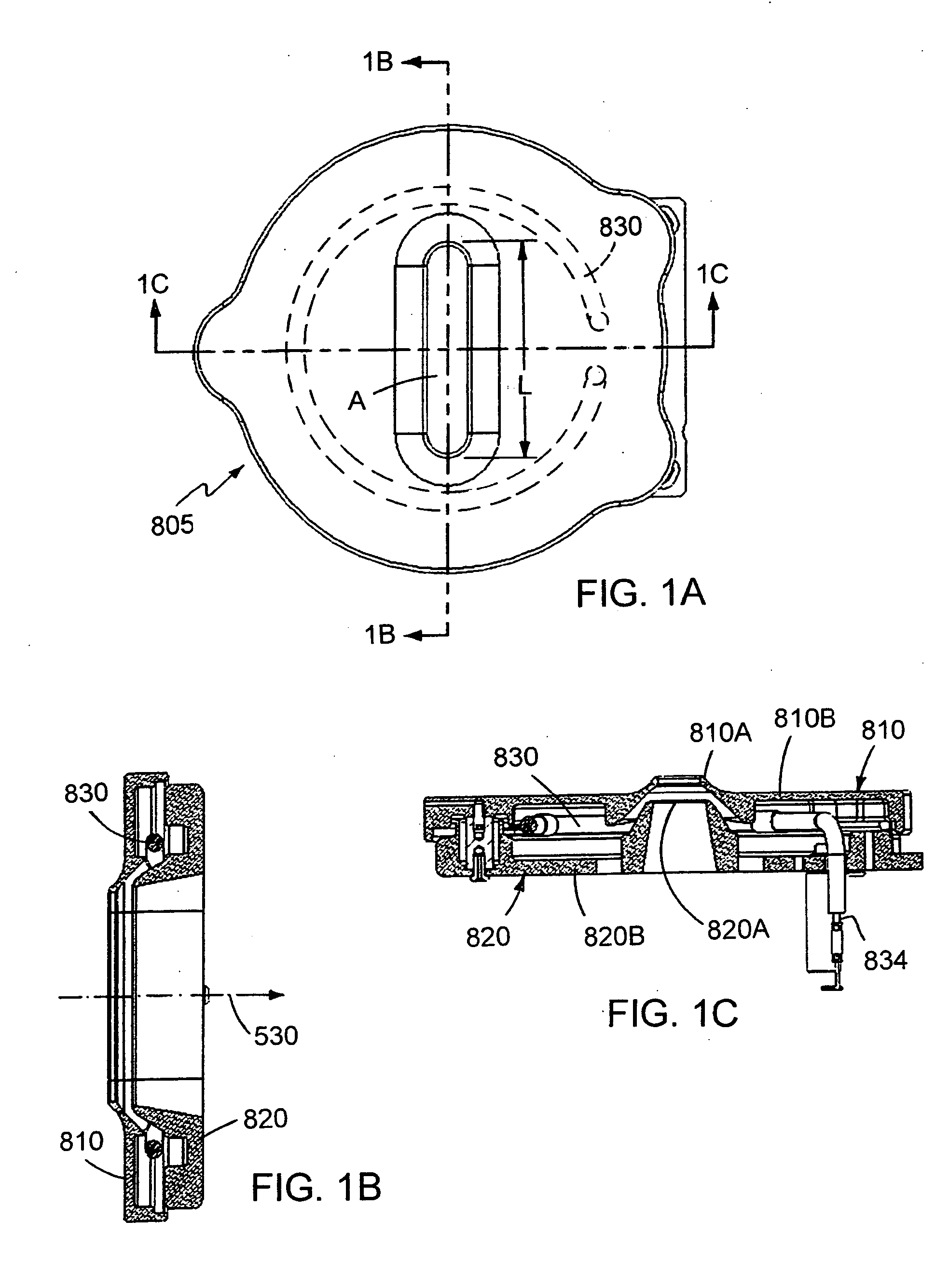

Method and apparatus for in-situ film stack processing

InactiveUS7358192B2Electric discharge tubesDecorative surface effectsDisplay deviceFlat panel display

Owner:APPLIED MATERIALS INC

Method and apparatus for in-situ film stack processing

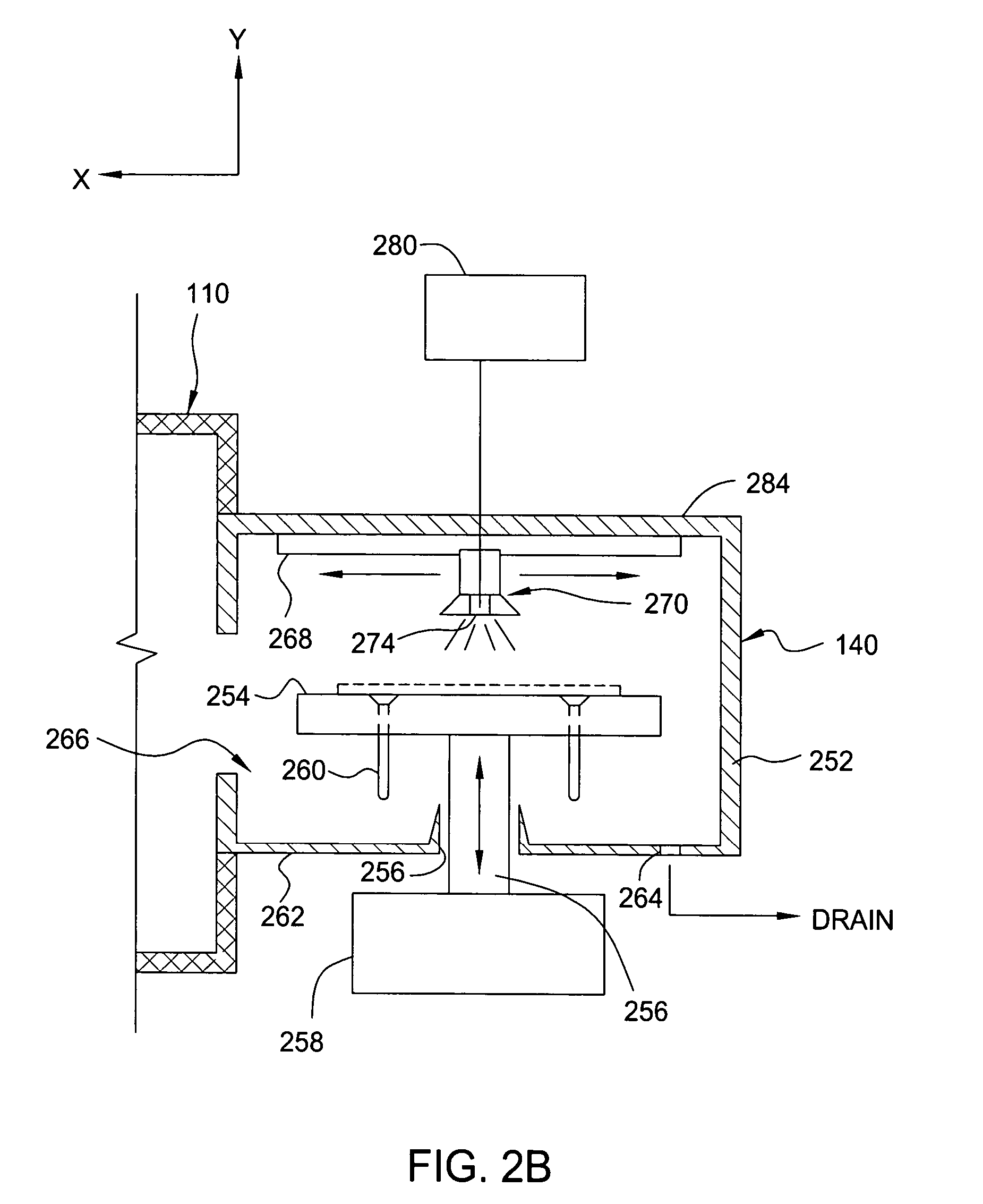

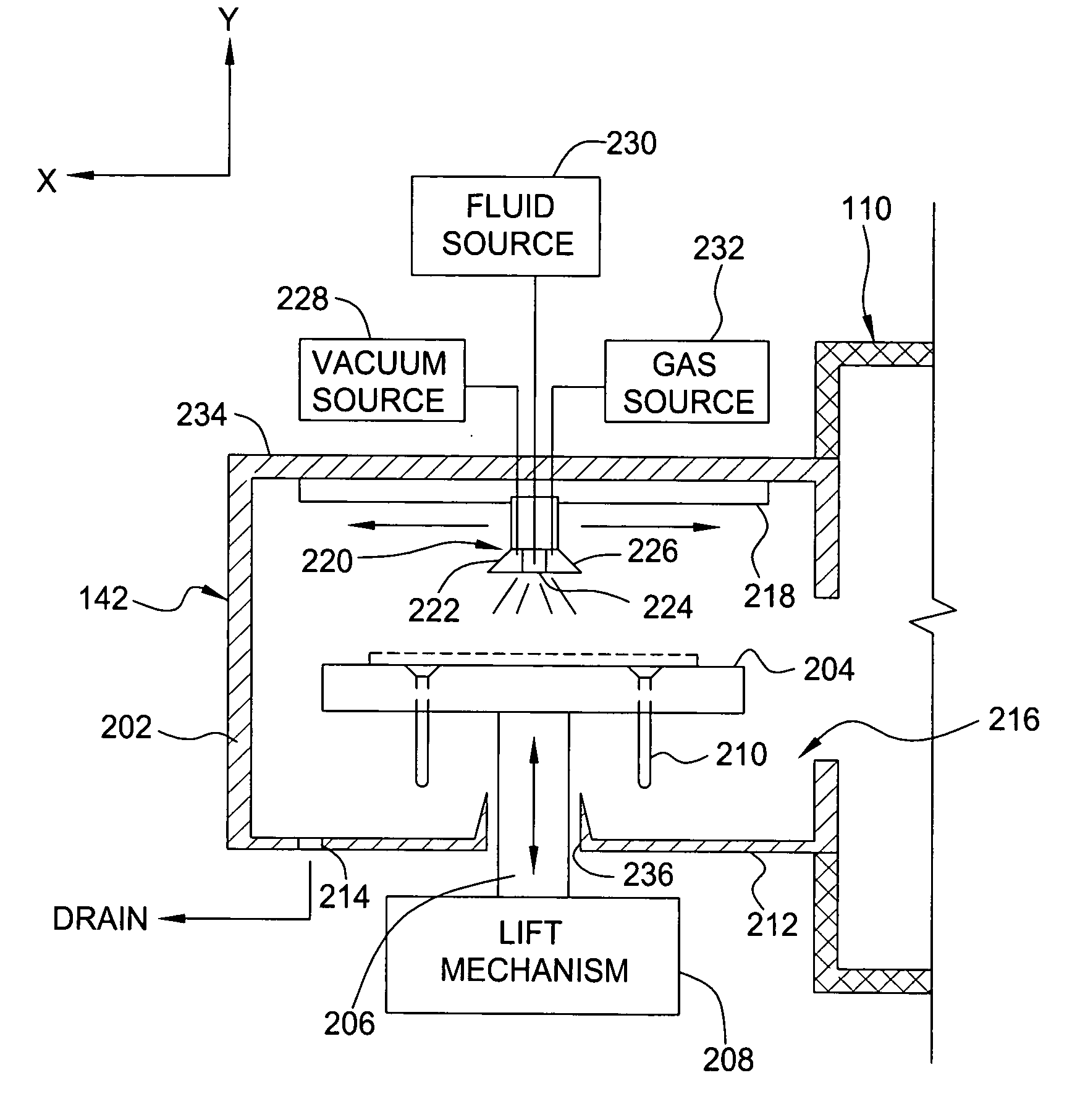

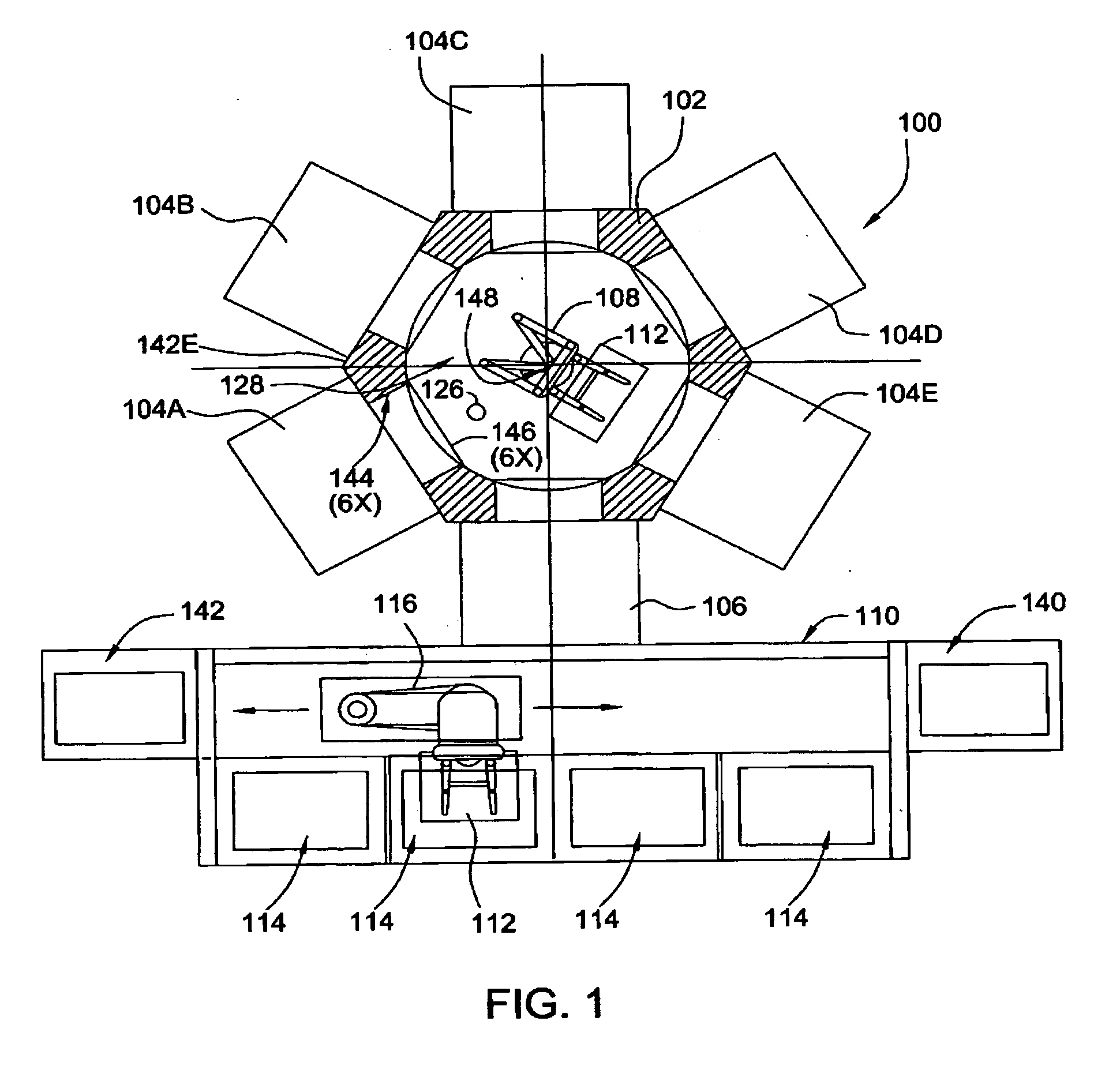

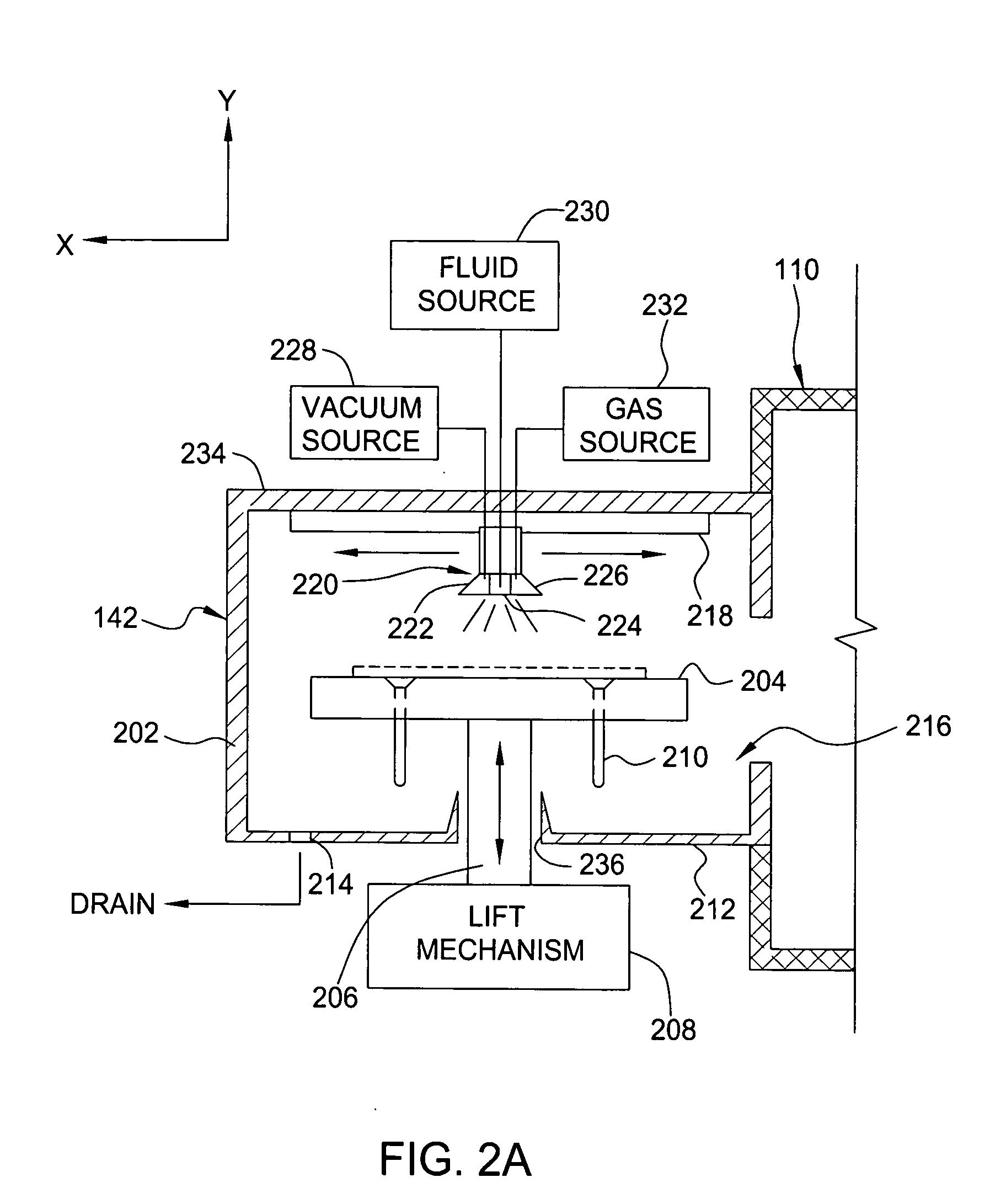

Embodiments of a cluster tool, processing chamber and method for processing a film stack are provided. In one embodiment, a method for in-situ etching of silicon and metal layers of a film stack is provided that includes the steps of etching an upper metal layer of the film stack in a processing chamber to expose a portion of an underlying silicon layer, and etching a trench in the silicon layer without removing the substrate from the processing chamber. The invention is particularly useful for thin film transistor fabrication for flat panel displays.

Owner:APPLIED MATERIALS INC

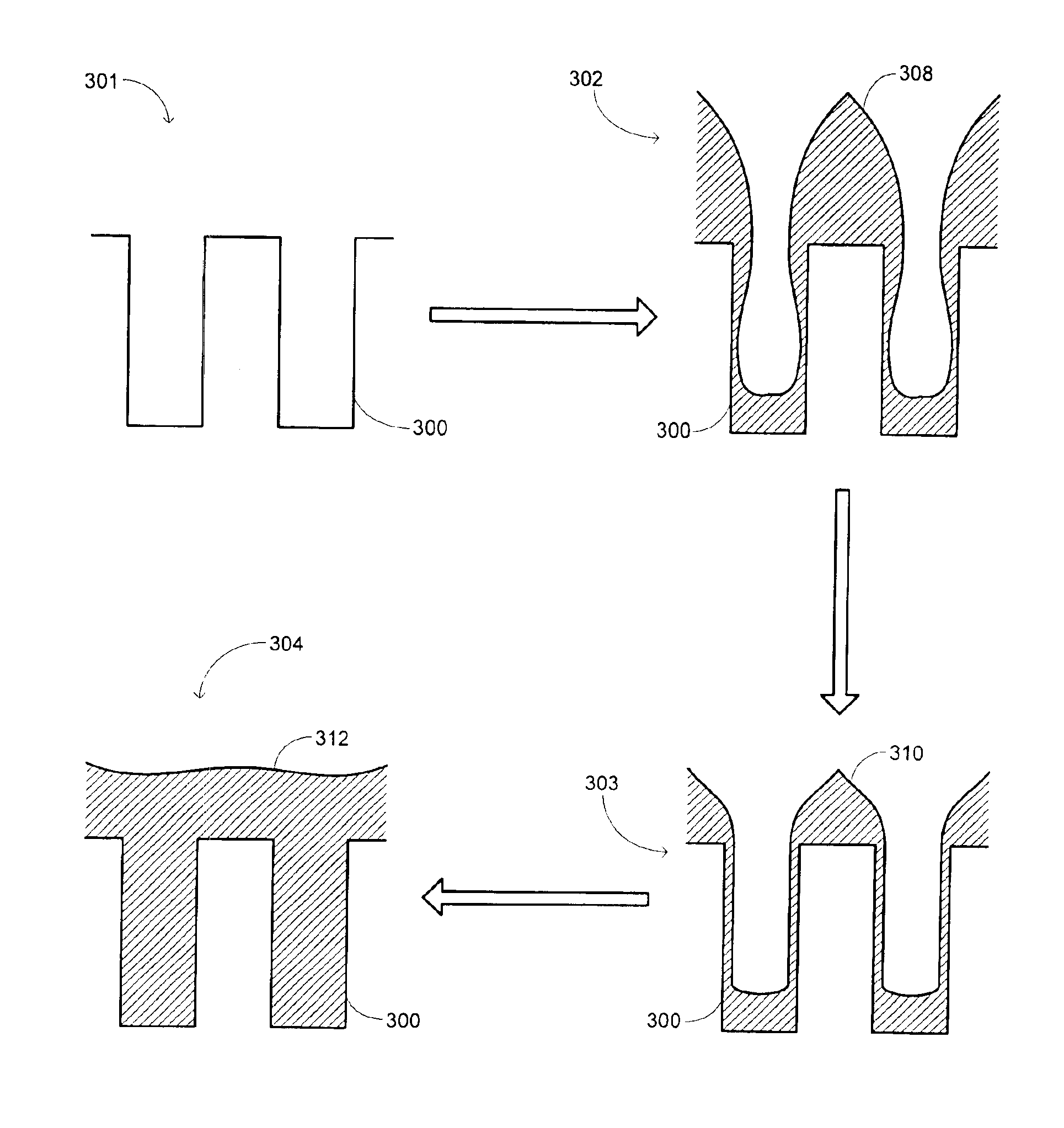

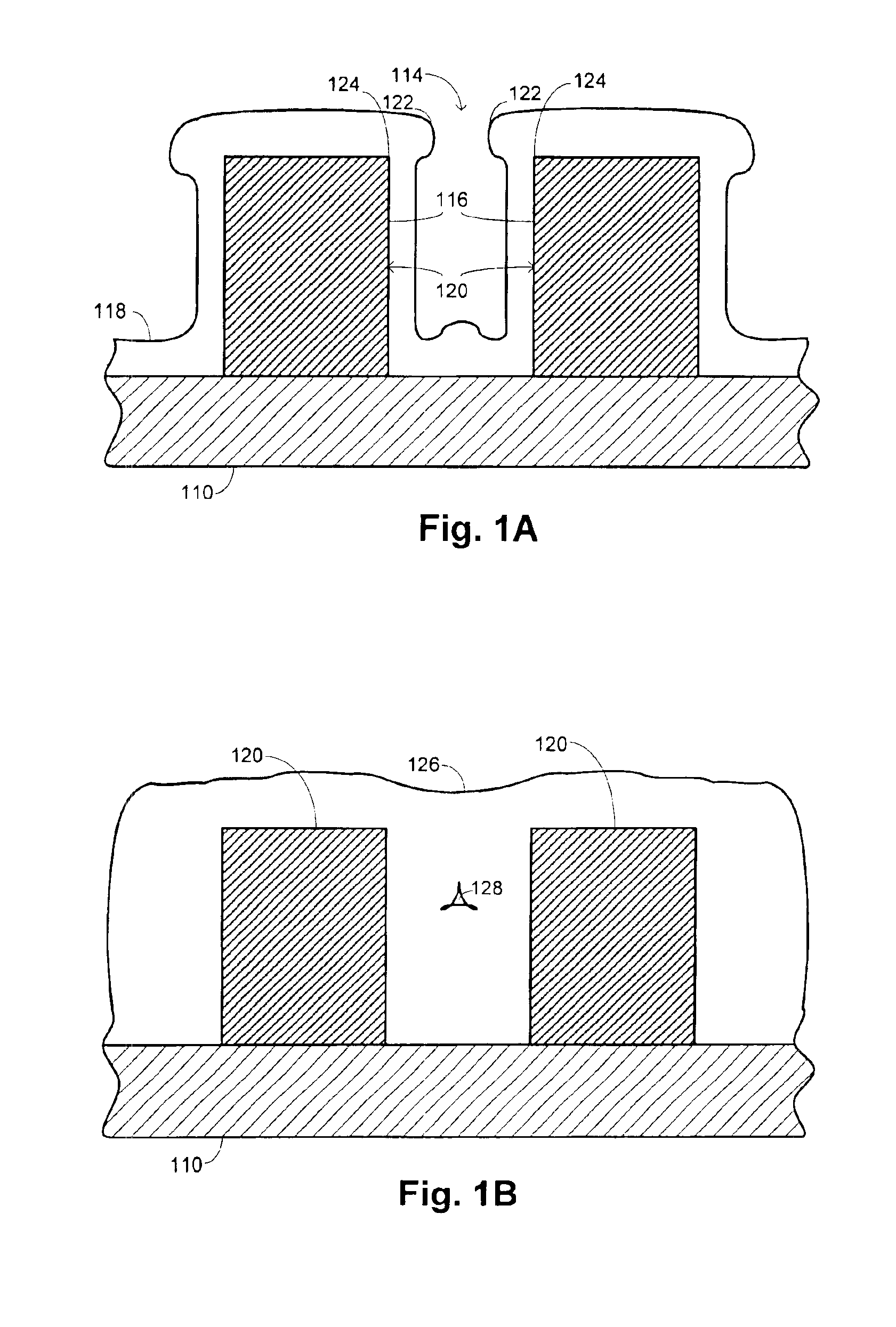

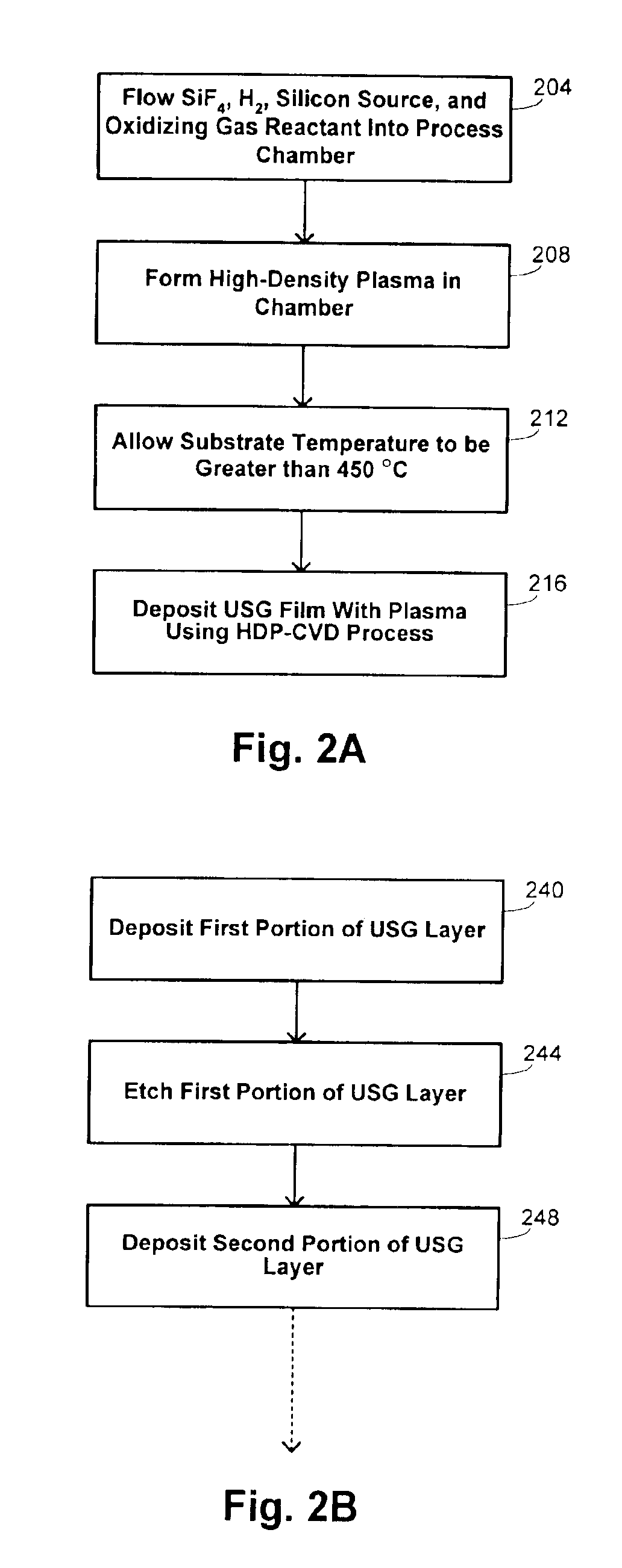

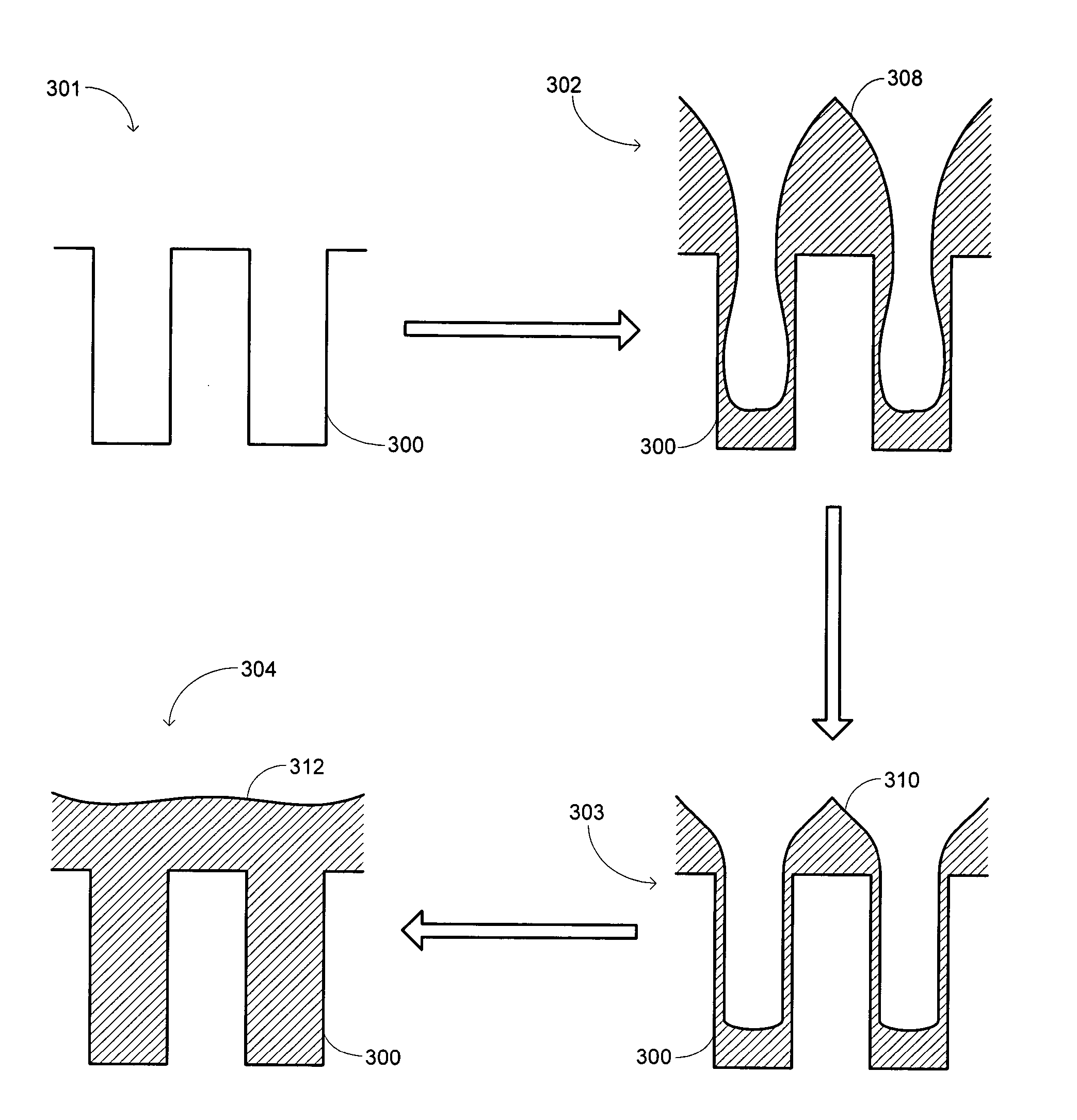

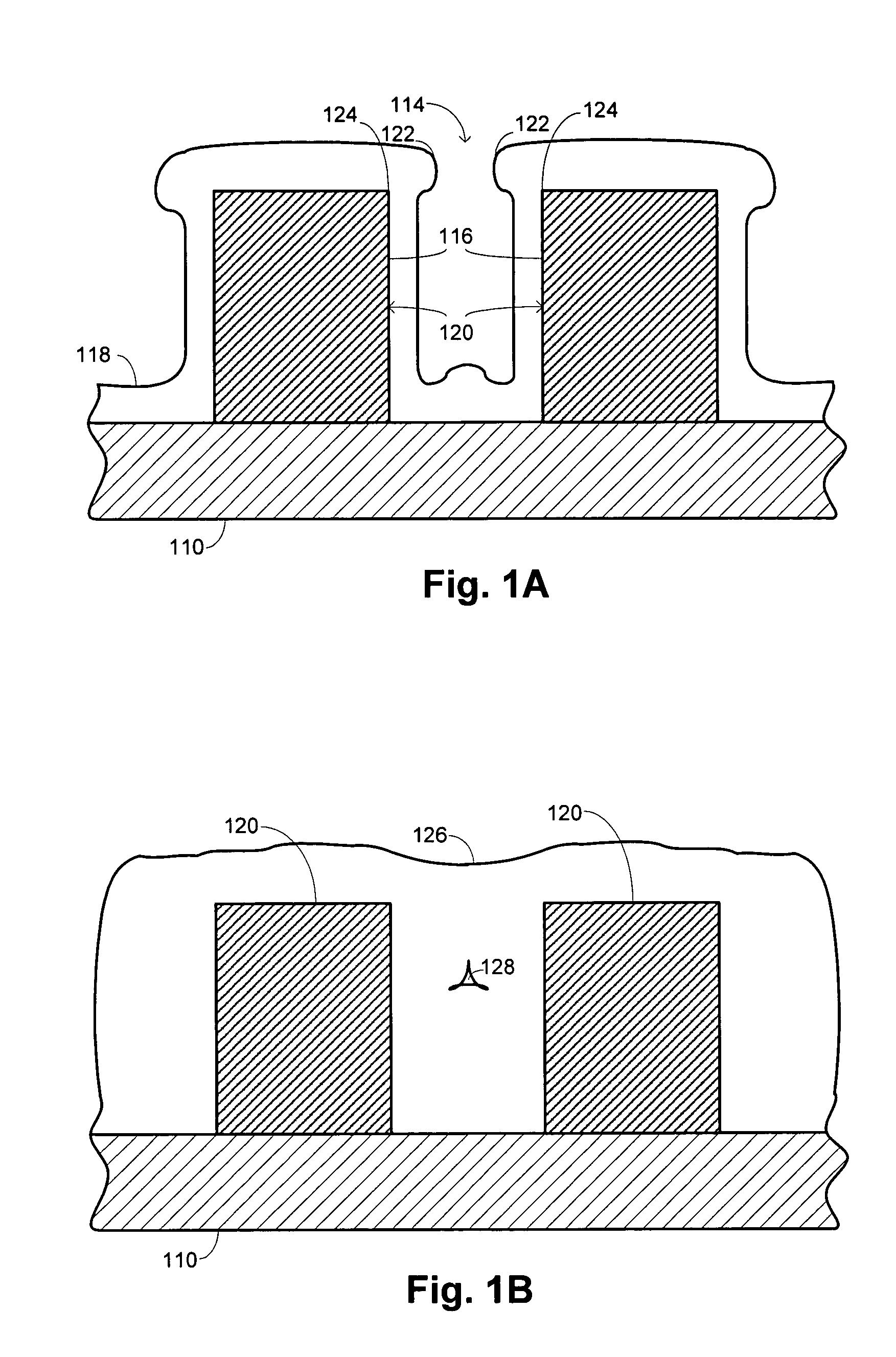

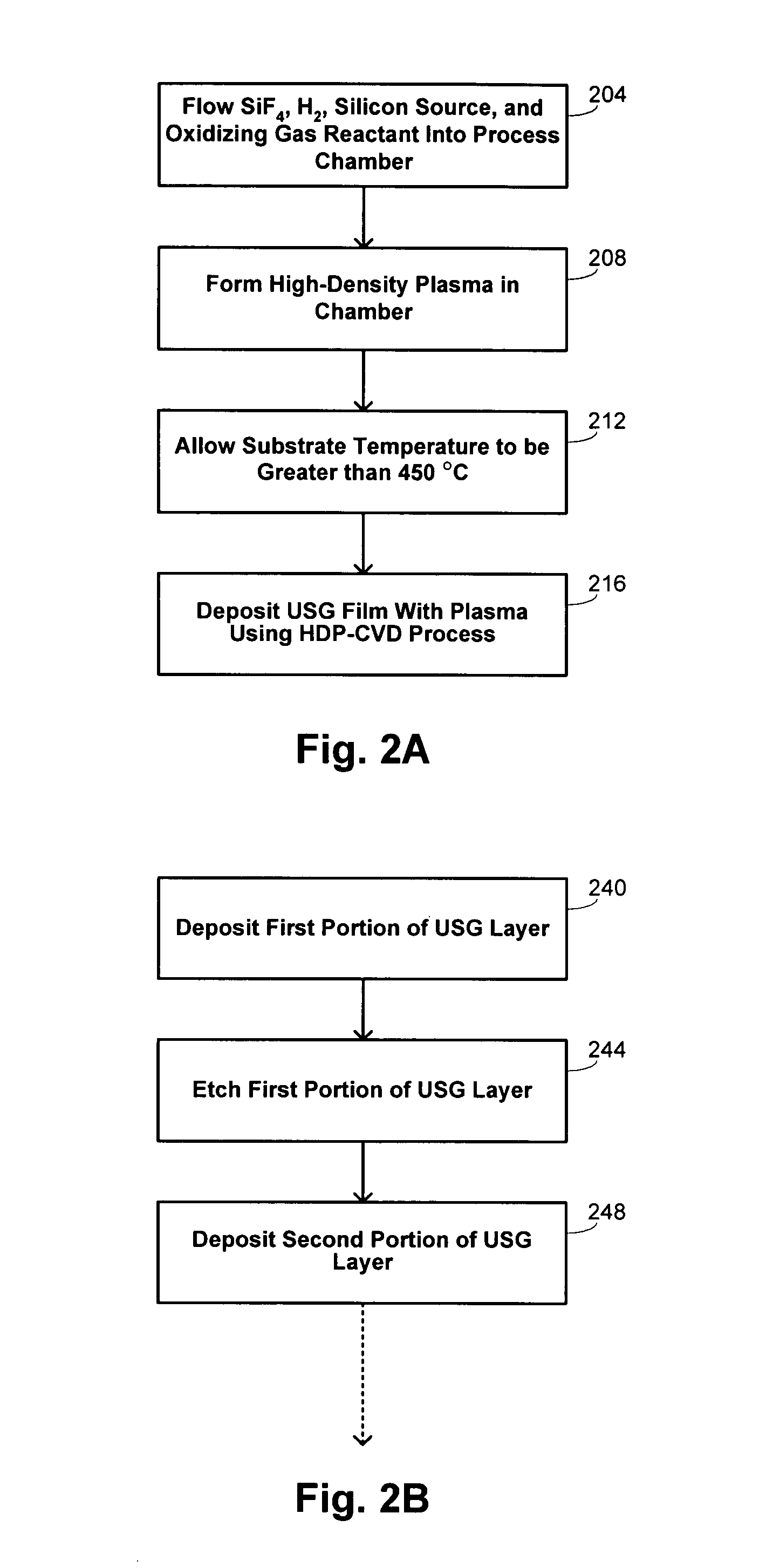

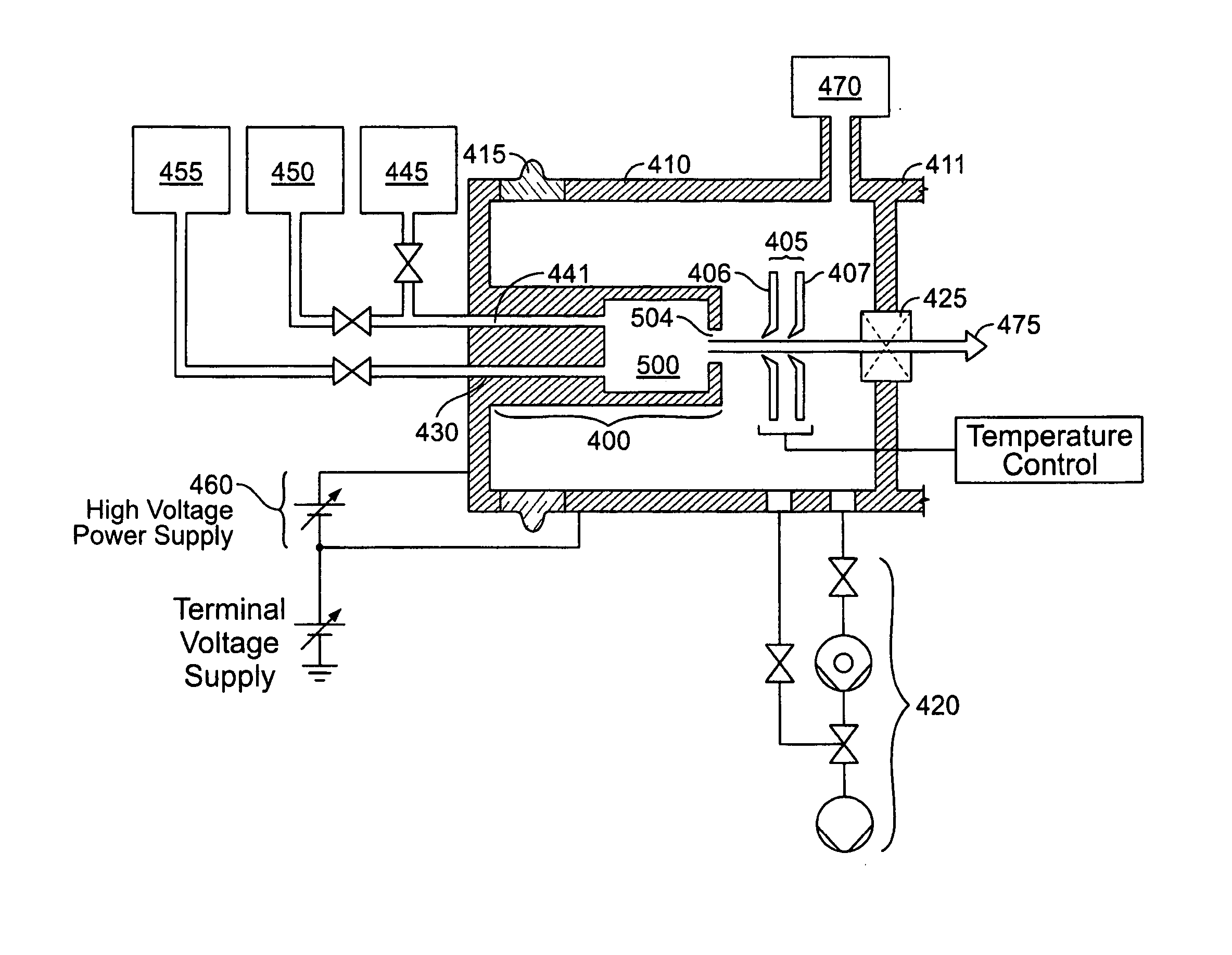

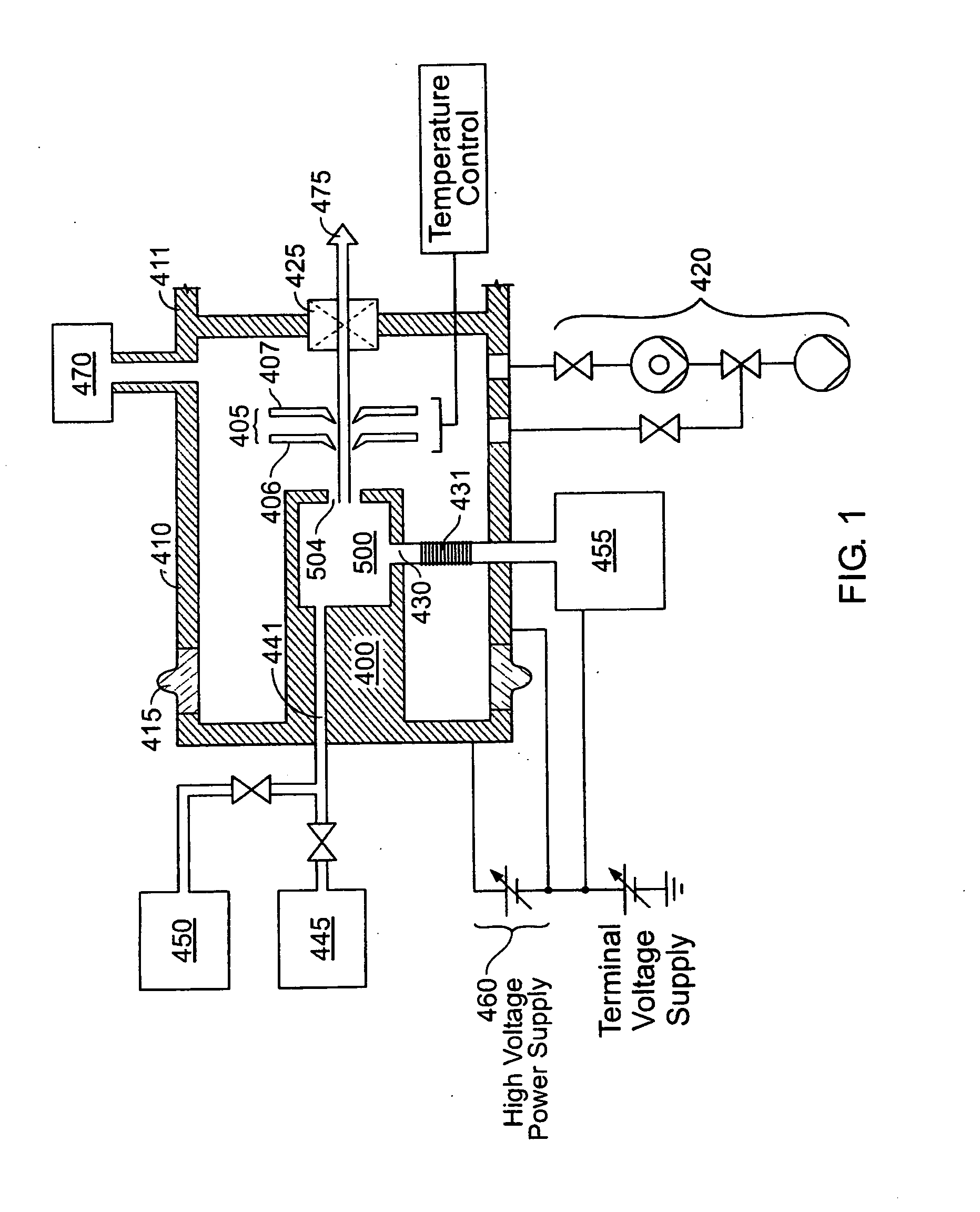

In-situ-etch-assisted HDP deposition using SiF4 and hydrogen

InactiveUS6903031B2Reduce concentrationImprove featuresSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenIon density

Owner:APPLIED MATERIALS INC

In-situ-etch-assisted HDP deposition using SiF4 and hydrogen

ActiveUS20050048801A1Good gapfill characteristicReduce fluorine concentrationSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHydrogenIon density

A process is provided for depositing an undoped silicon oxide film on a substrate disposed in a process chamber. A process gas that includes SiF4, H2, a silicon source, and an oxidizing gas reactant is flowed into the process chamber. A plasma having an ion density of at least 1011 ions / cm3 is formed from the process gas. The undoped silicon oxide film is deposited over the substrate with the plasma using a process that has simultaneous deposition and sputtering components. A temperature of the substrate during such depositing is greater than 450° C.

Owner:APPLIED MATERIALS INC

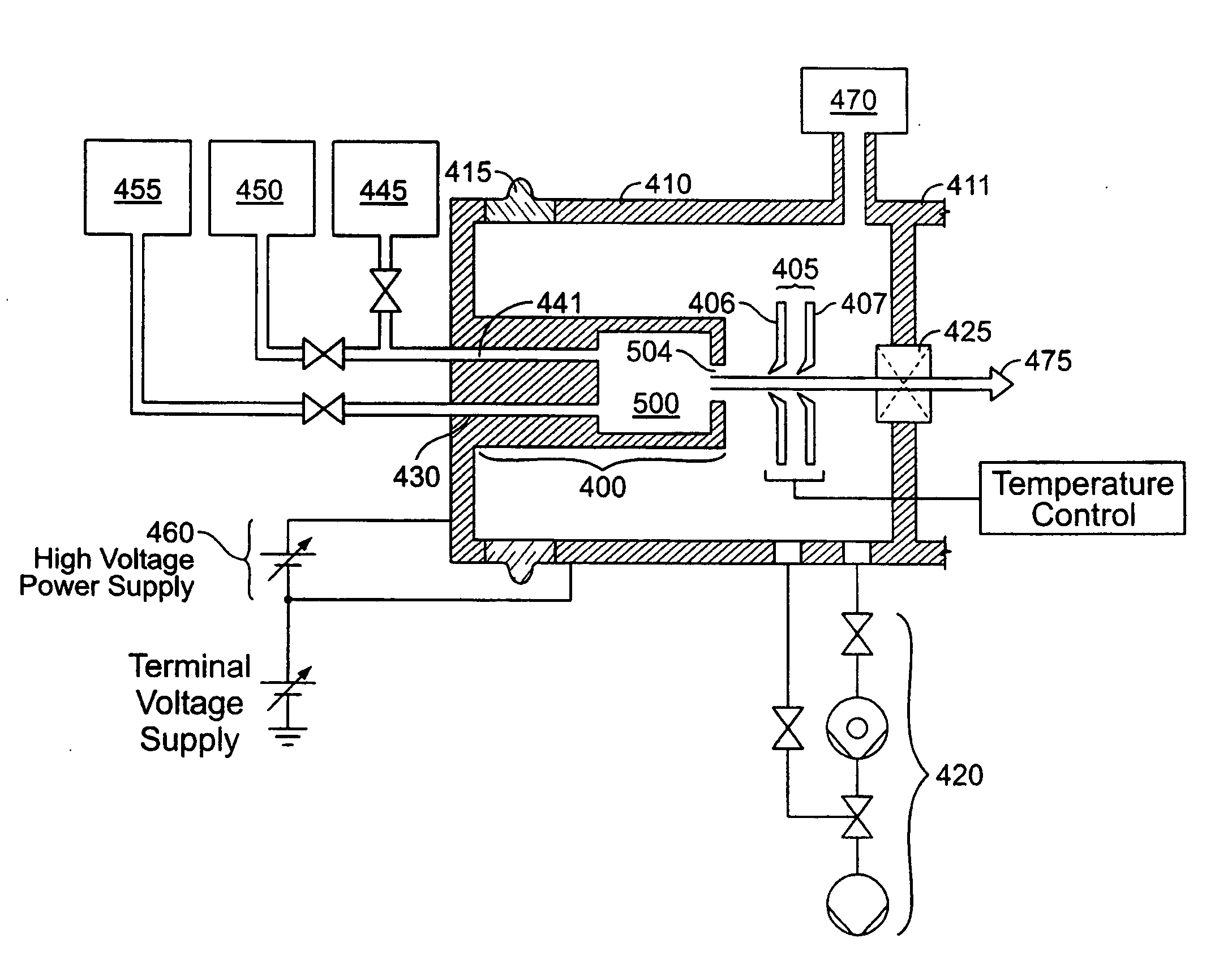

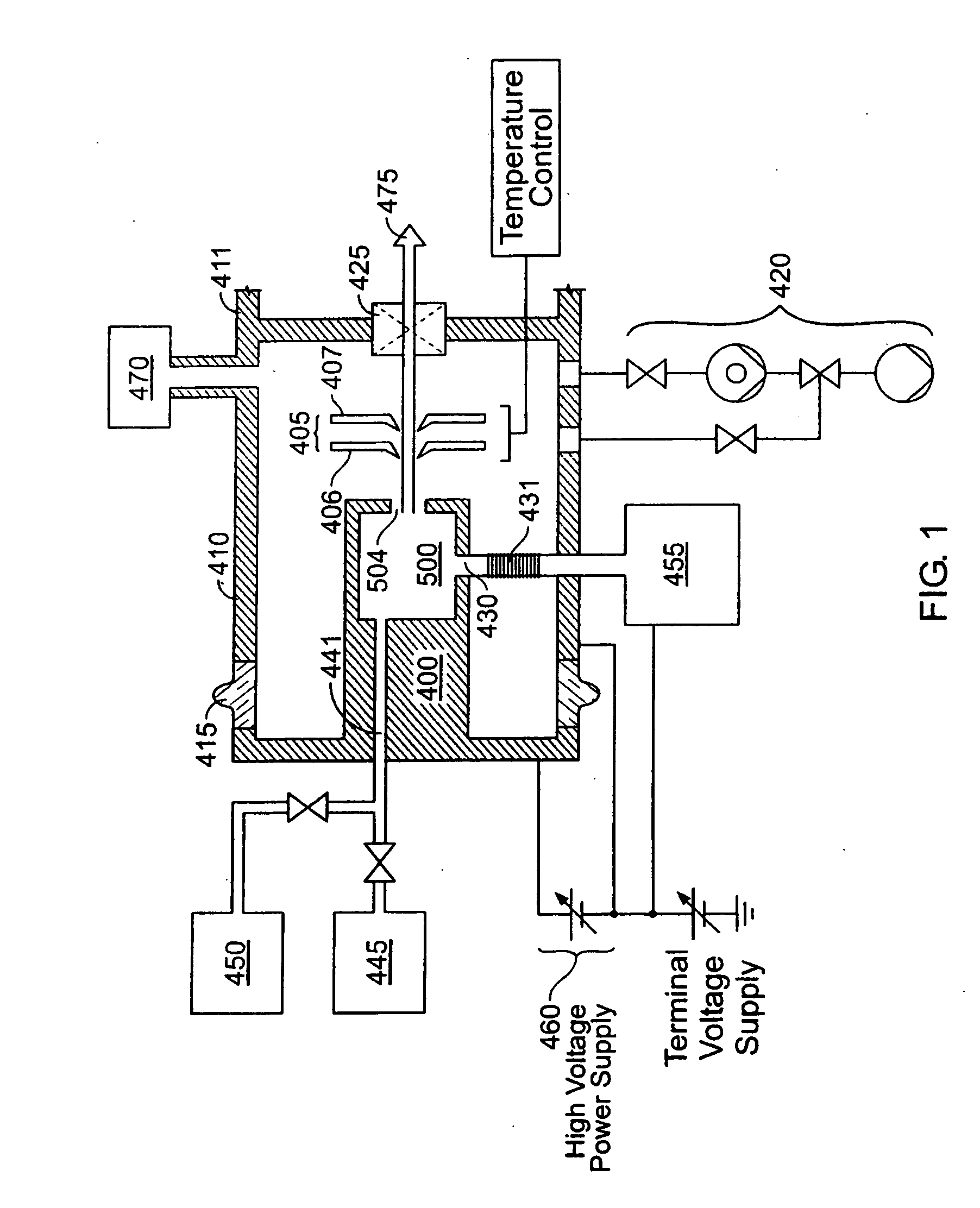

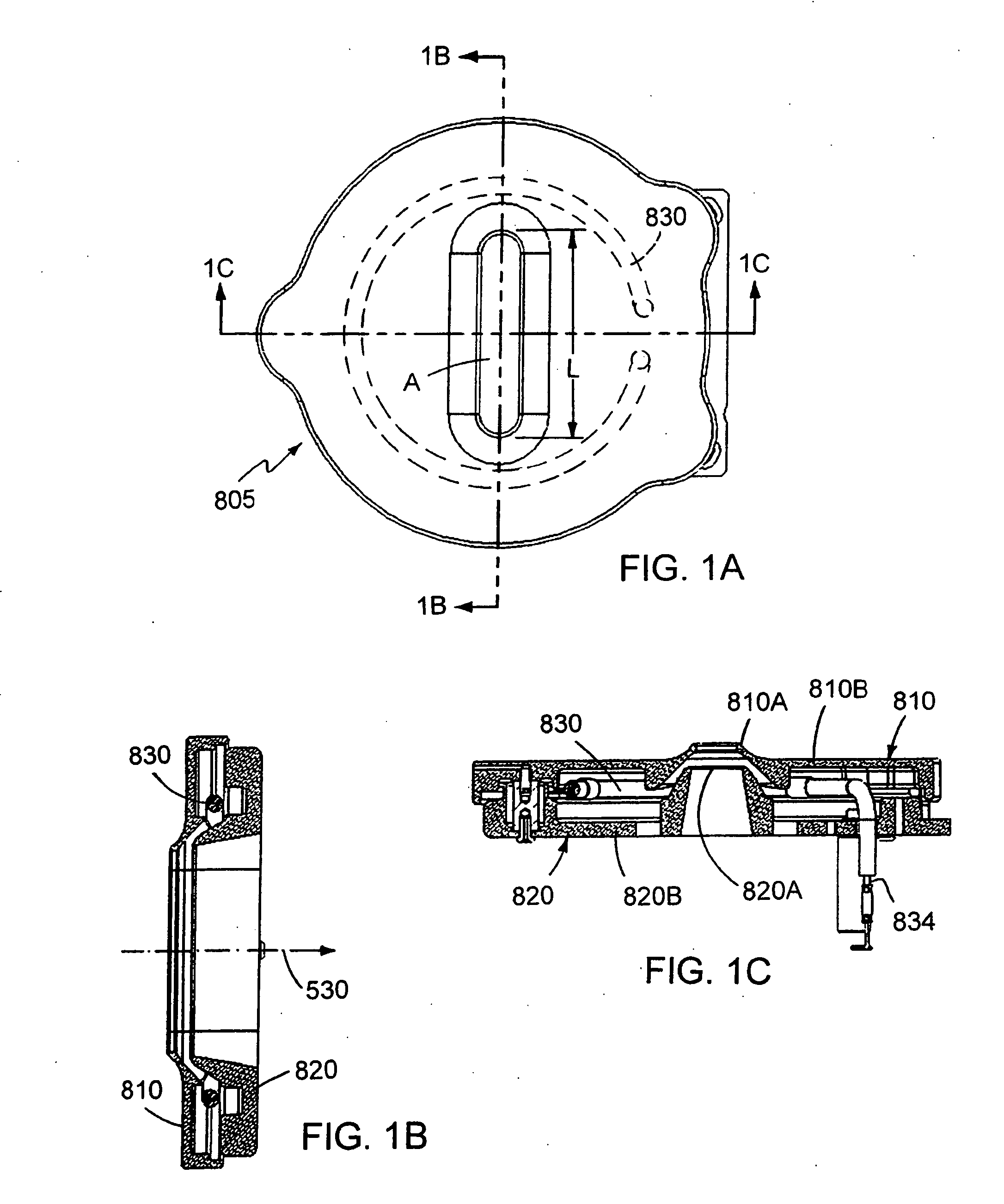

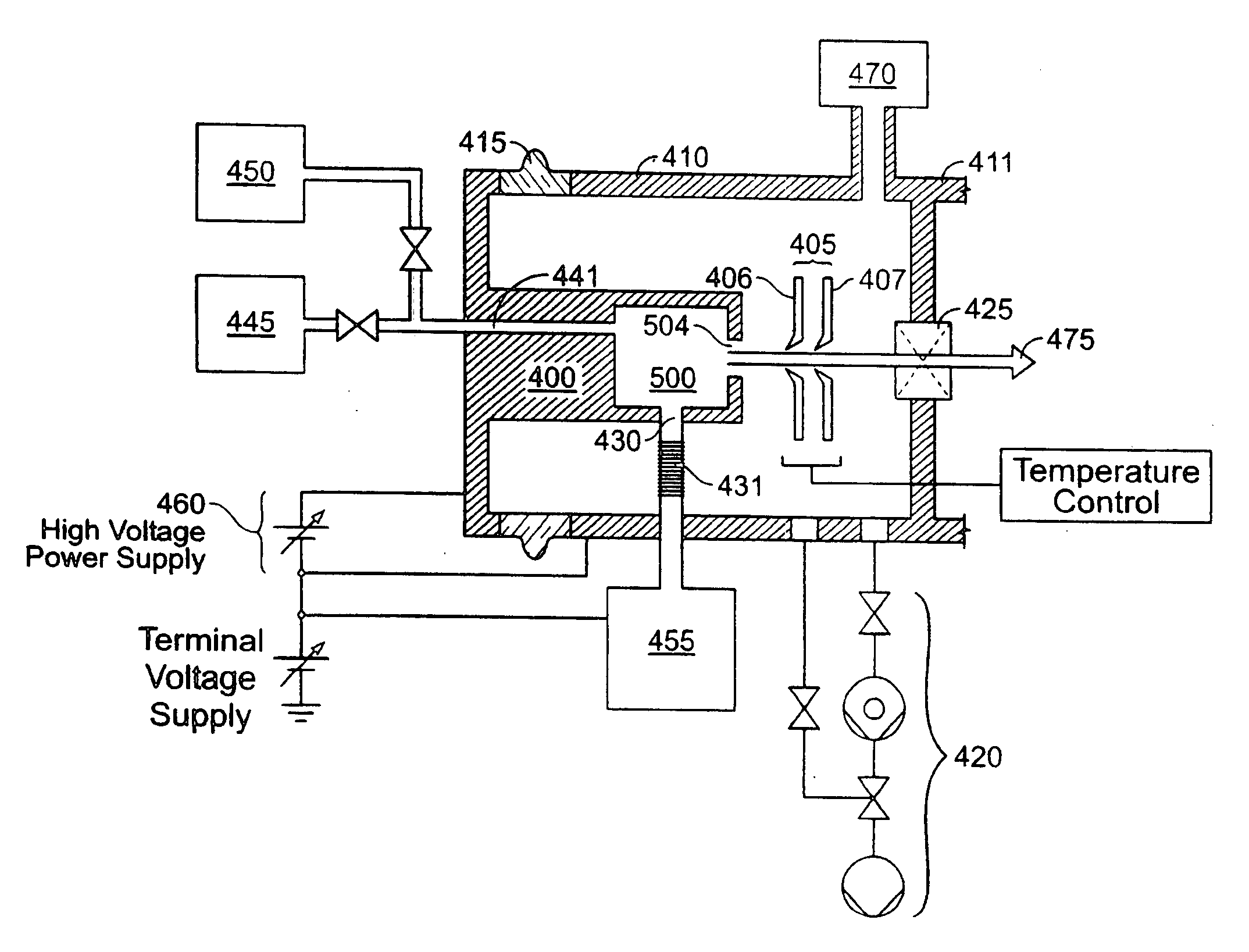

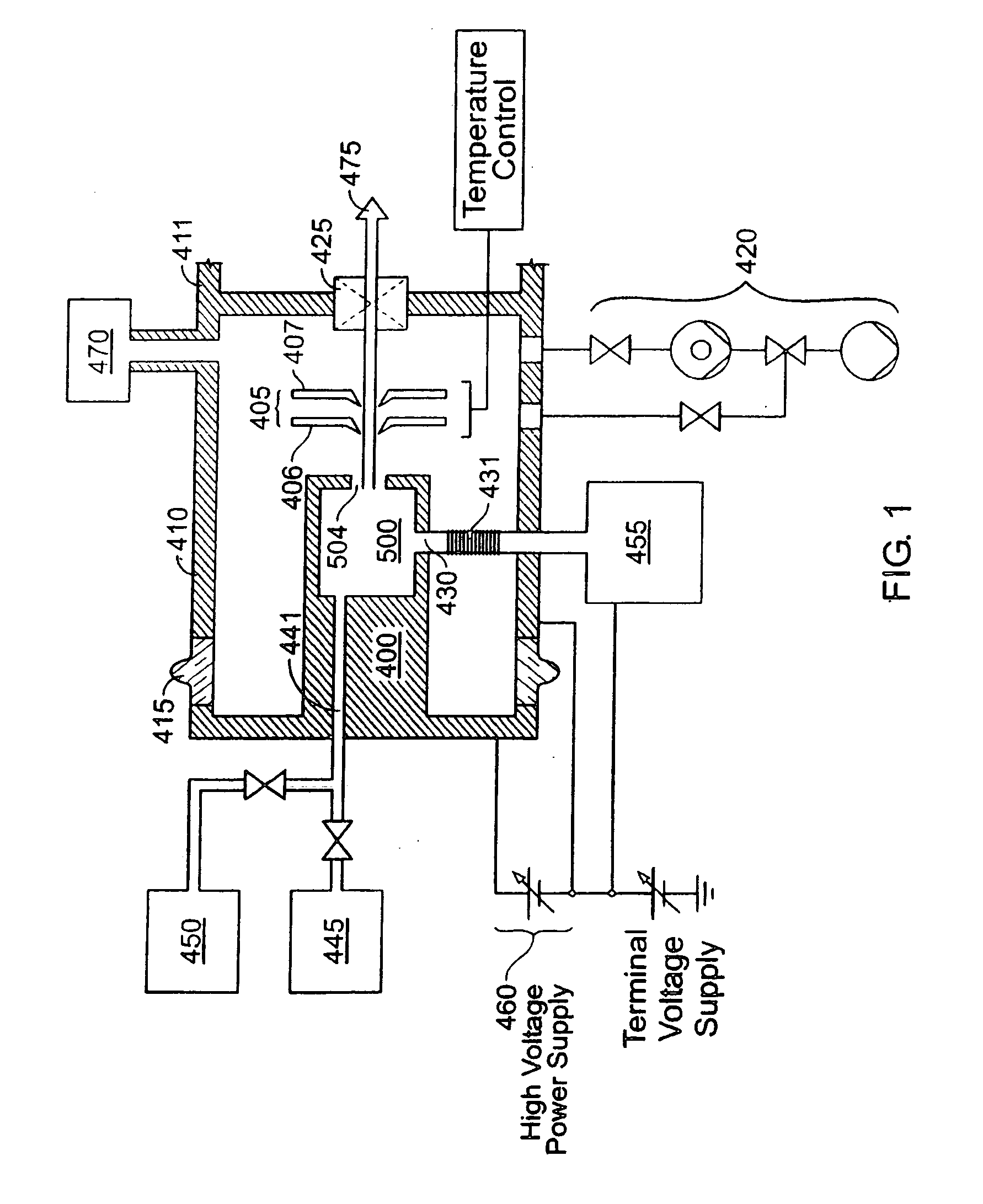

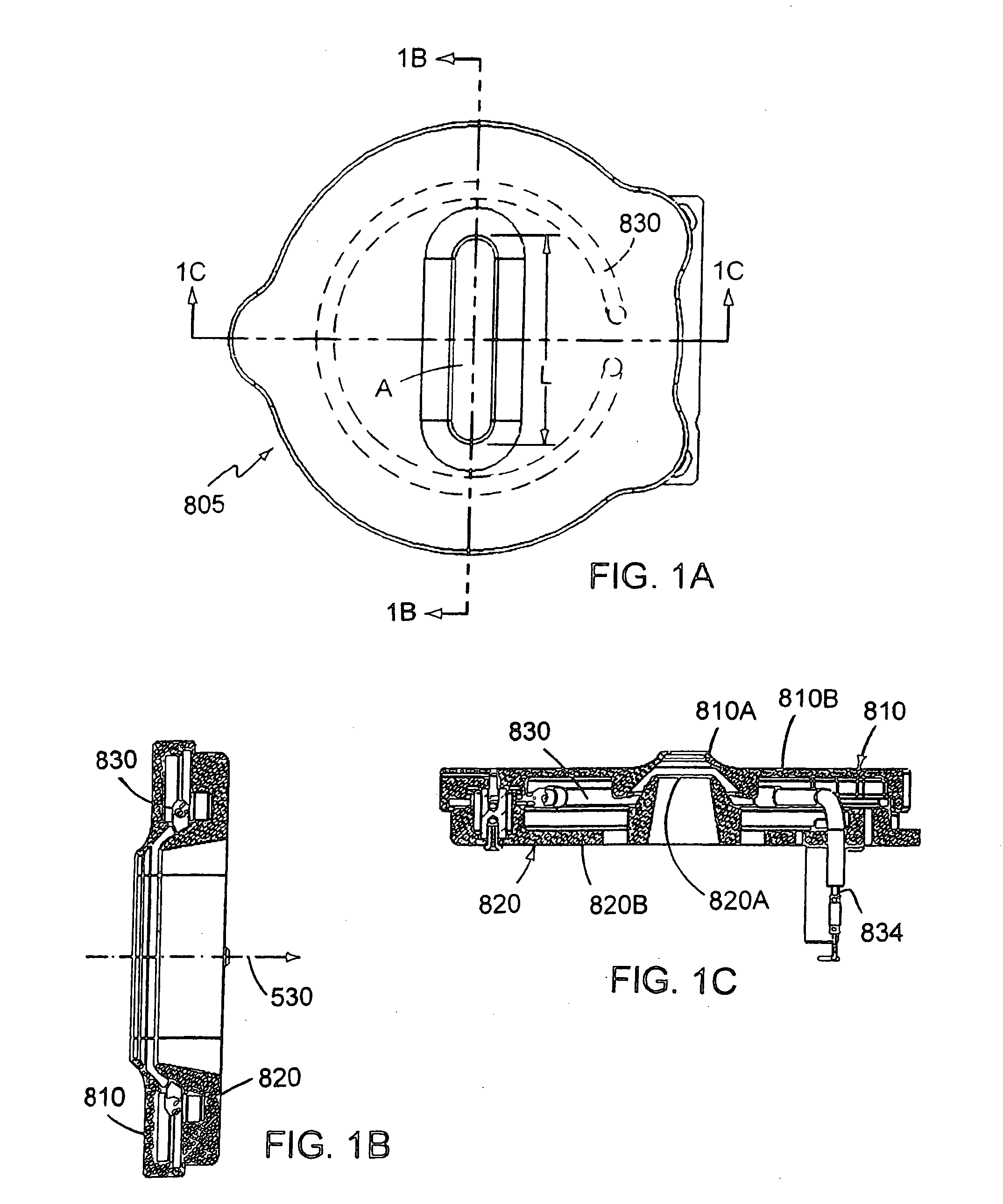

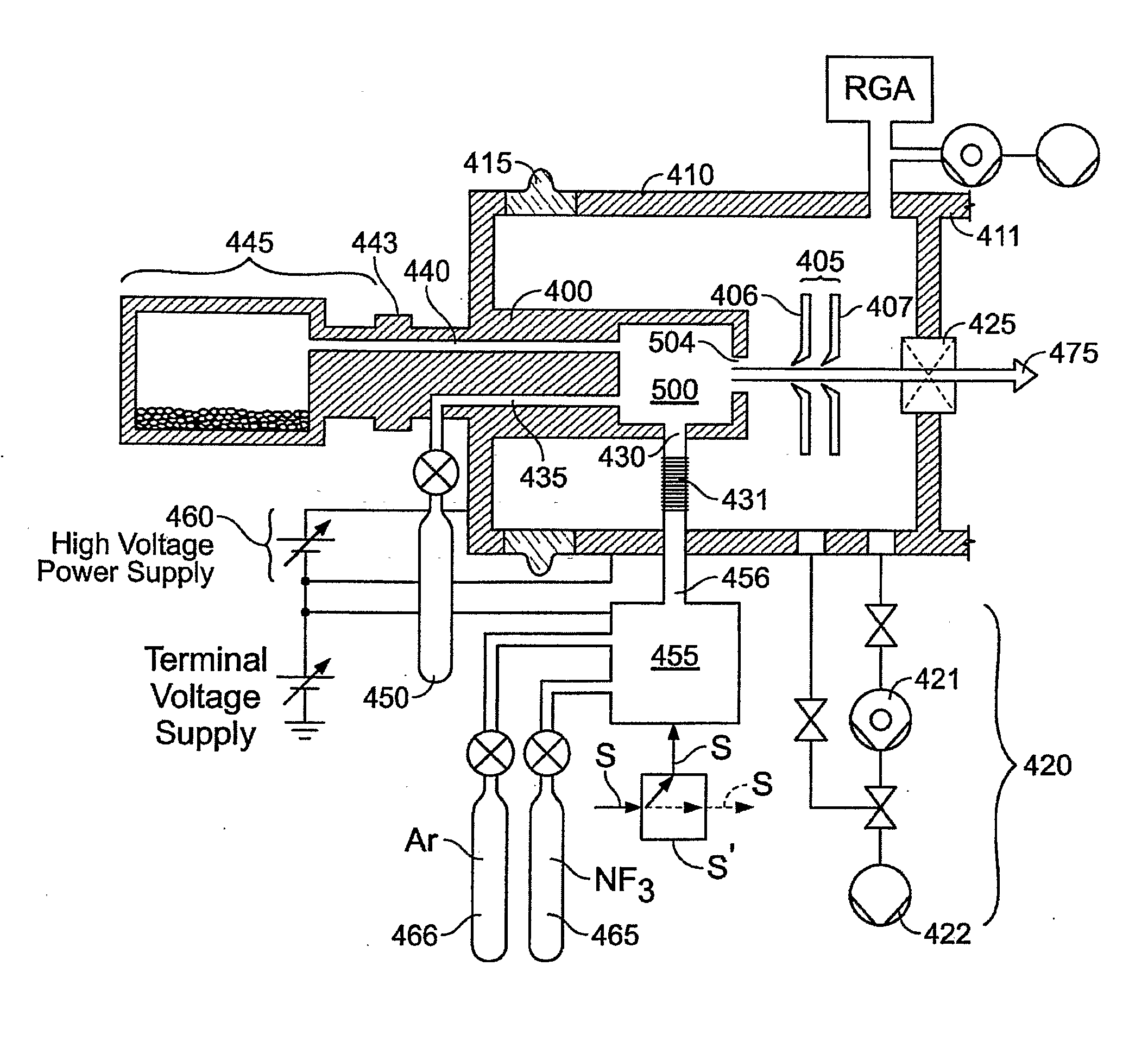

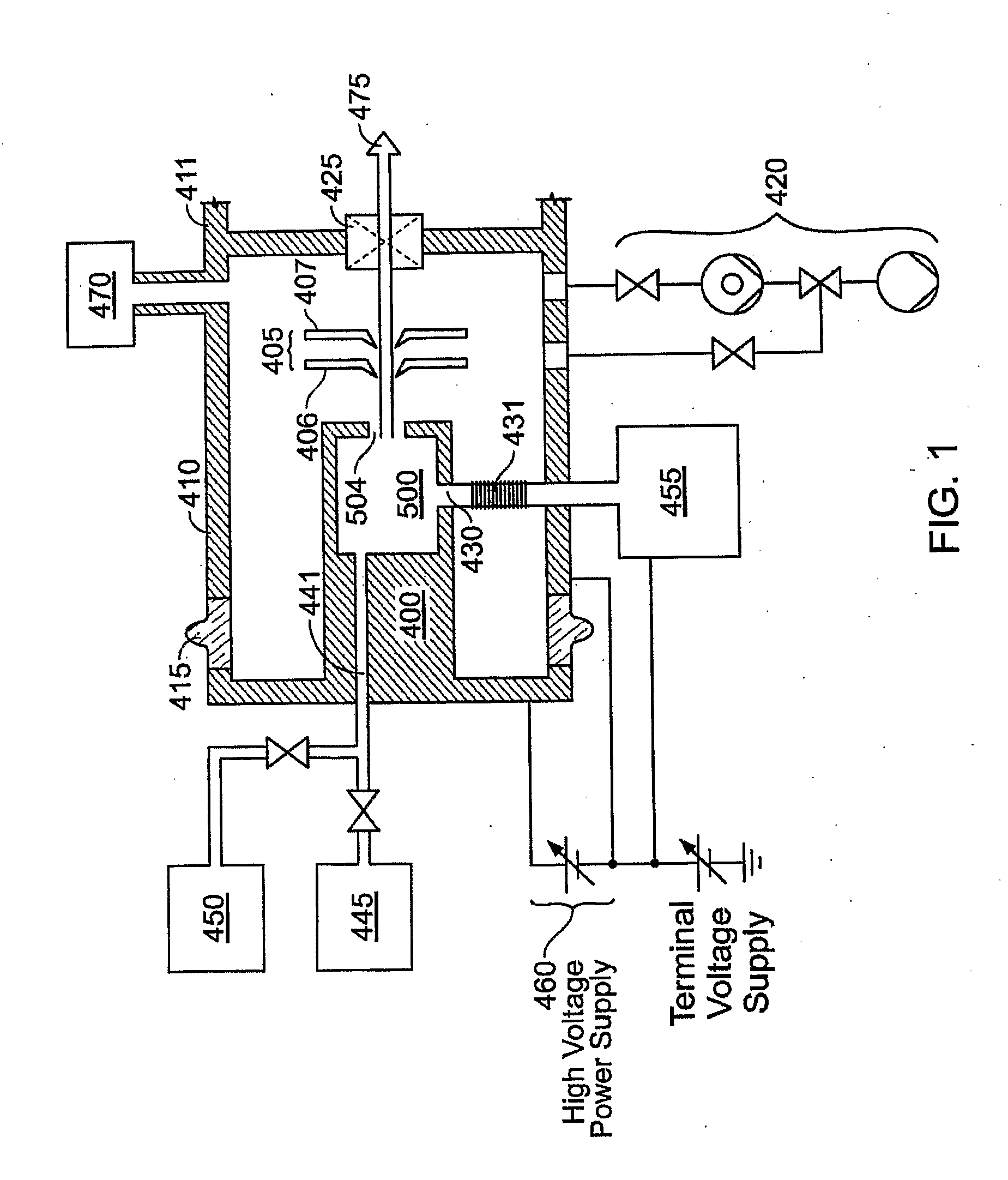

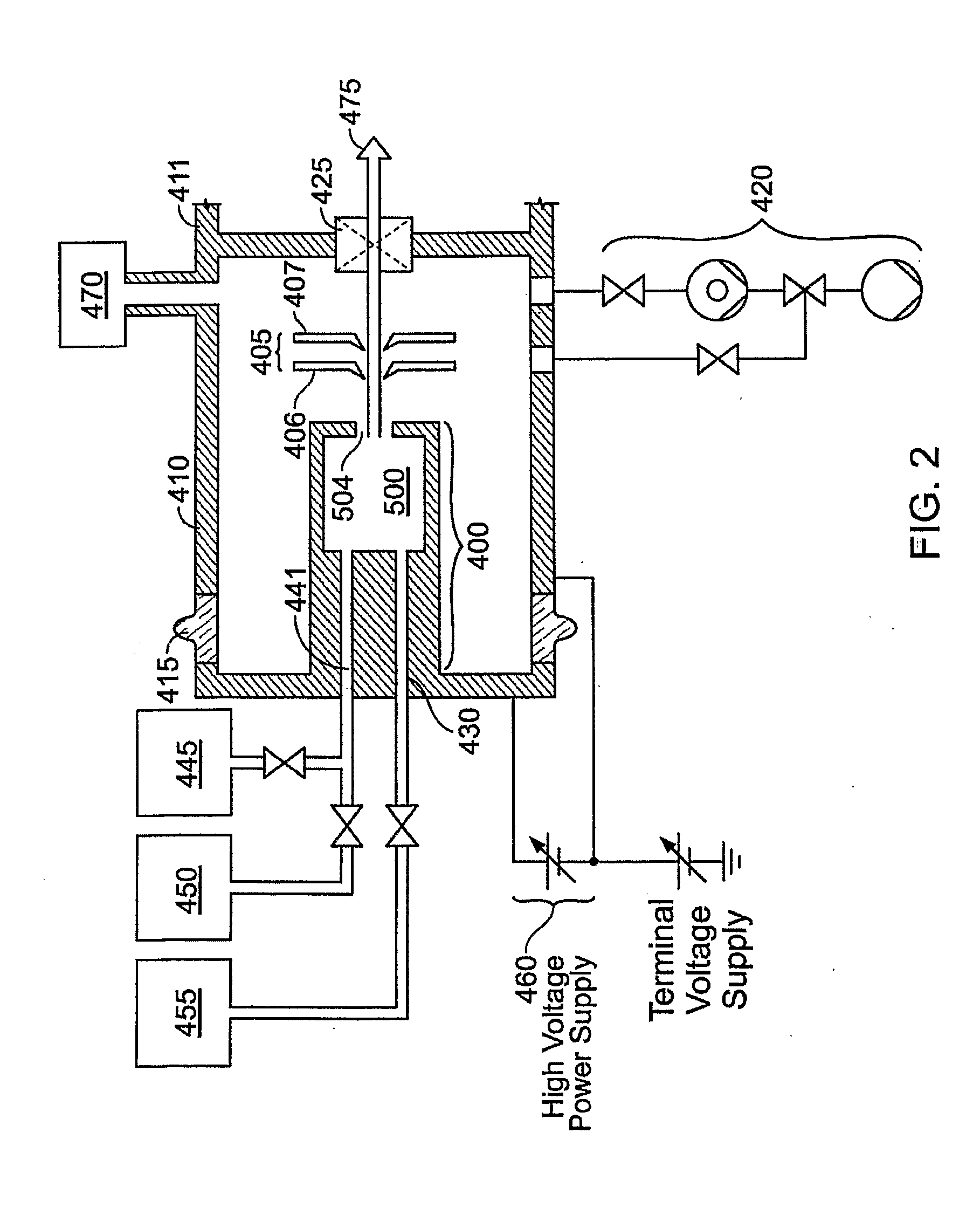

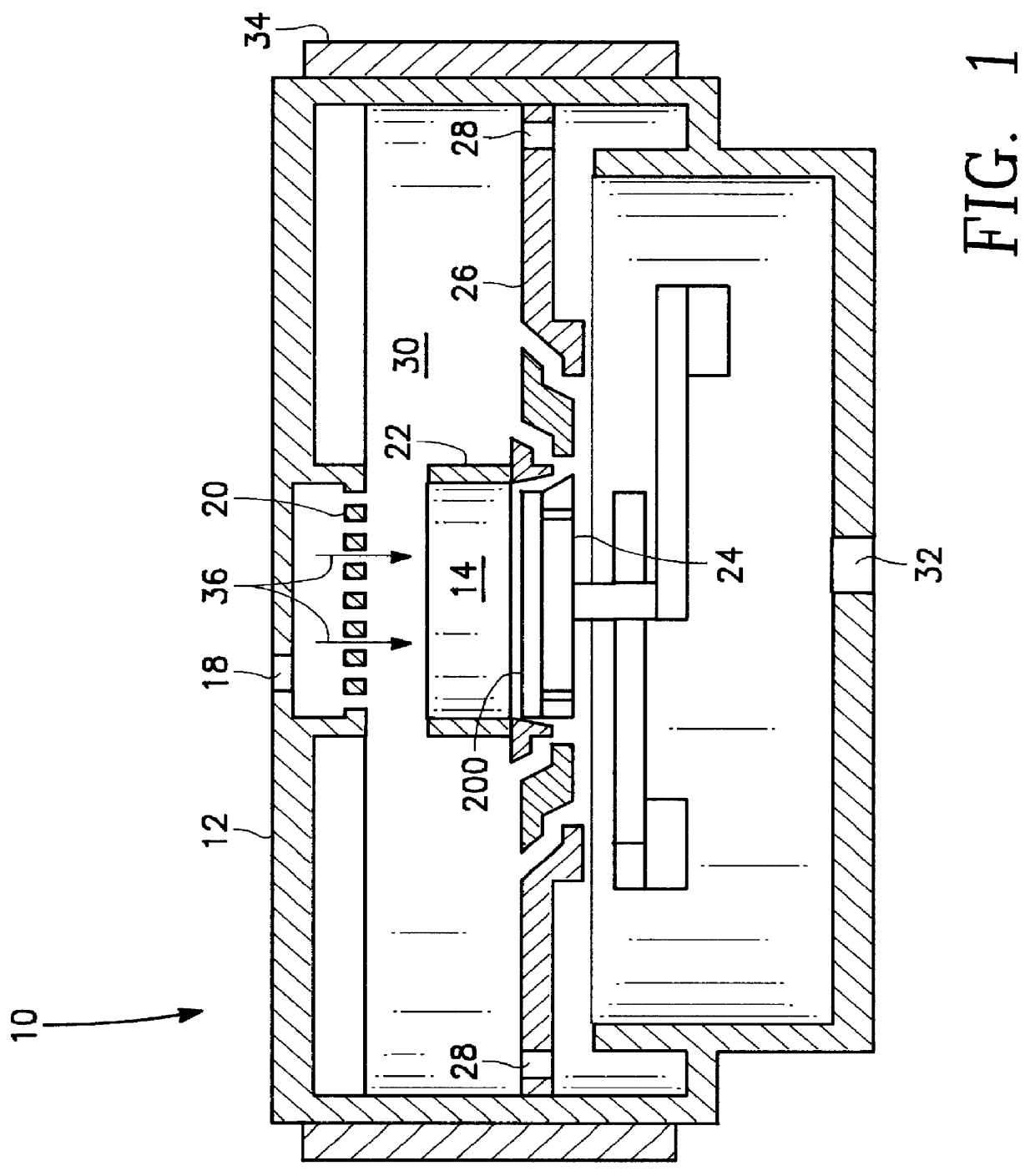

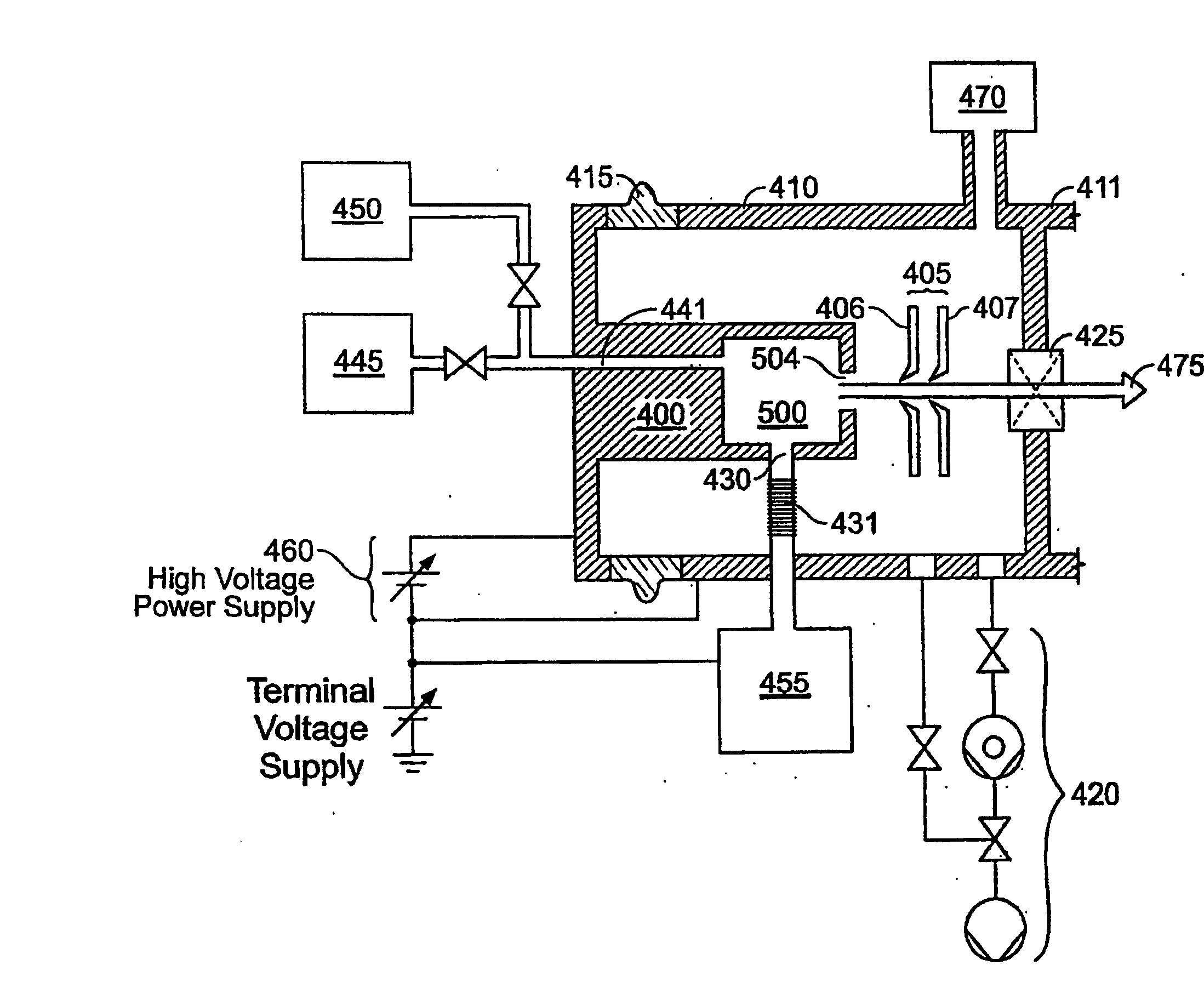

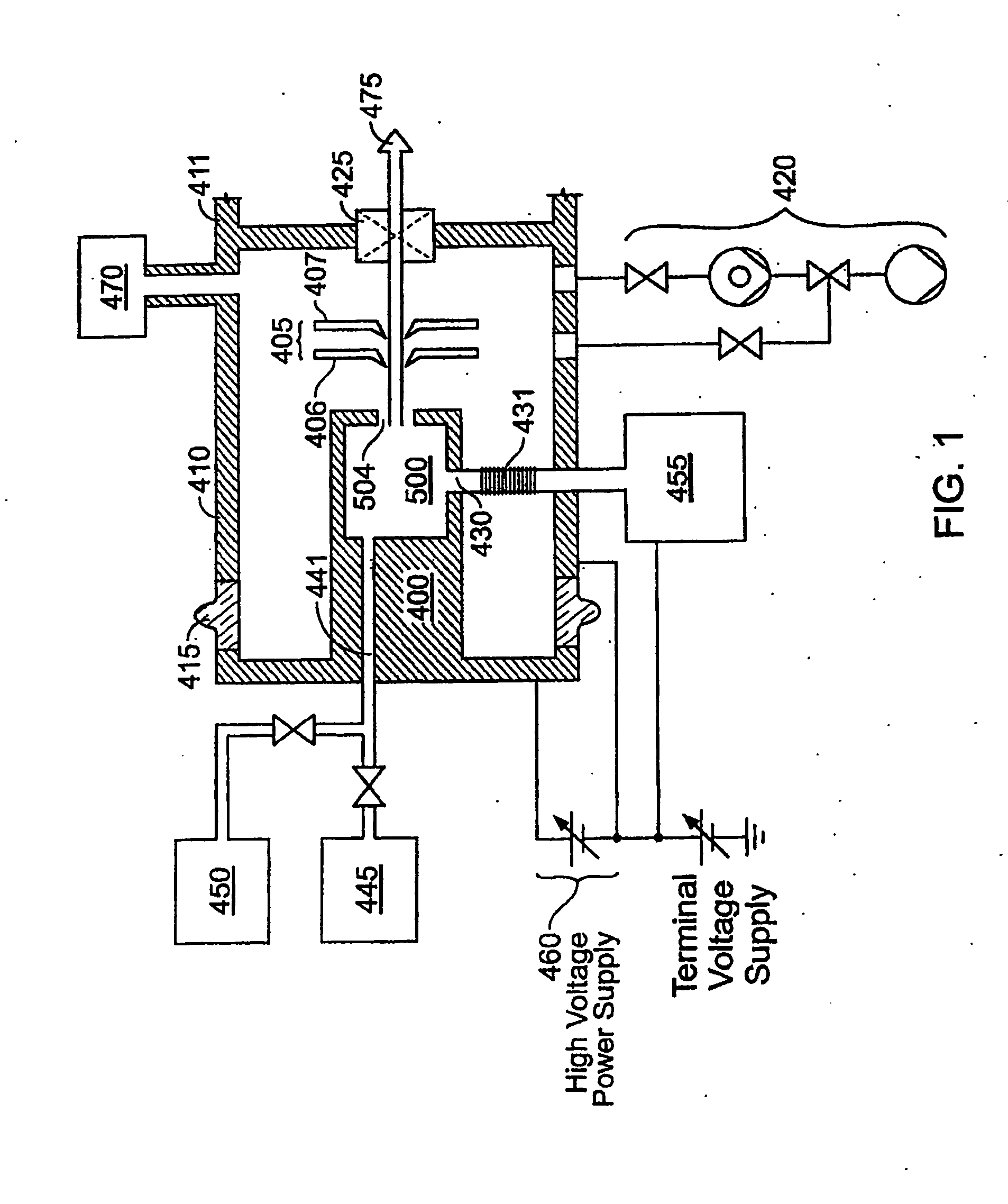

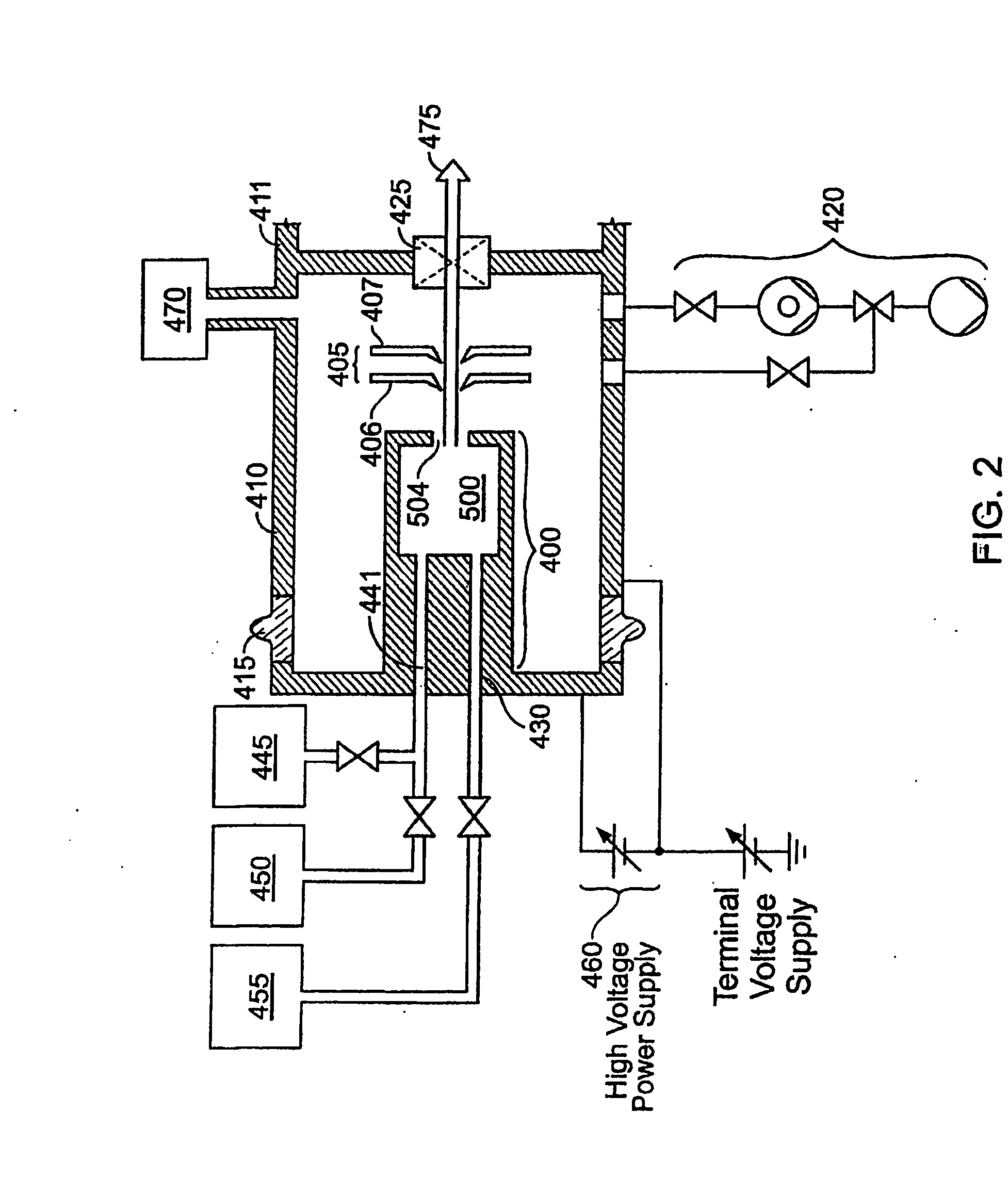

Method and apparatus for extracting ions from an ion source for use in ion implantation

InactiveUS20060272775A1Avoid unstable operationMaintain dimensional stabilityVacuum evaporation coatingSemiconductor/solid-state device manufacturingRemote plasmaActive cooling

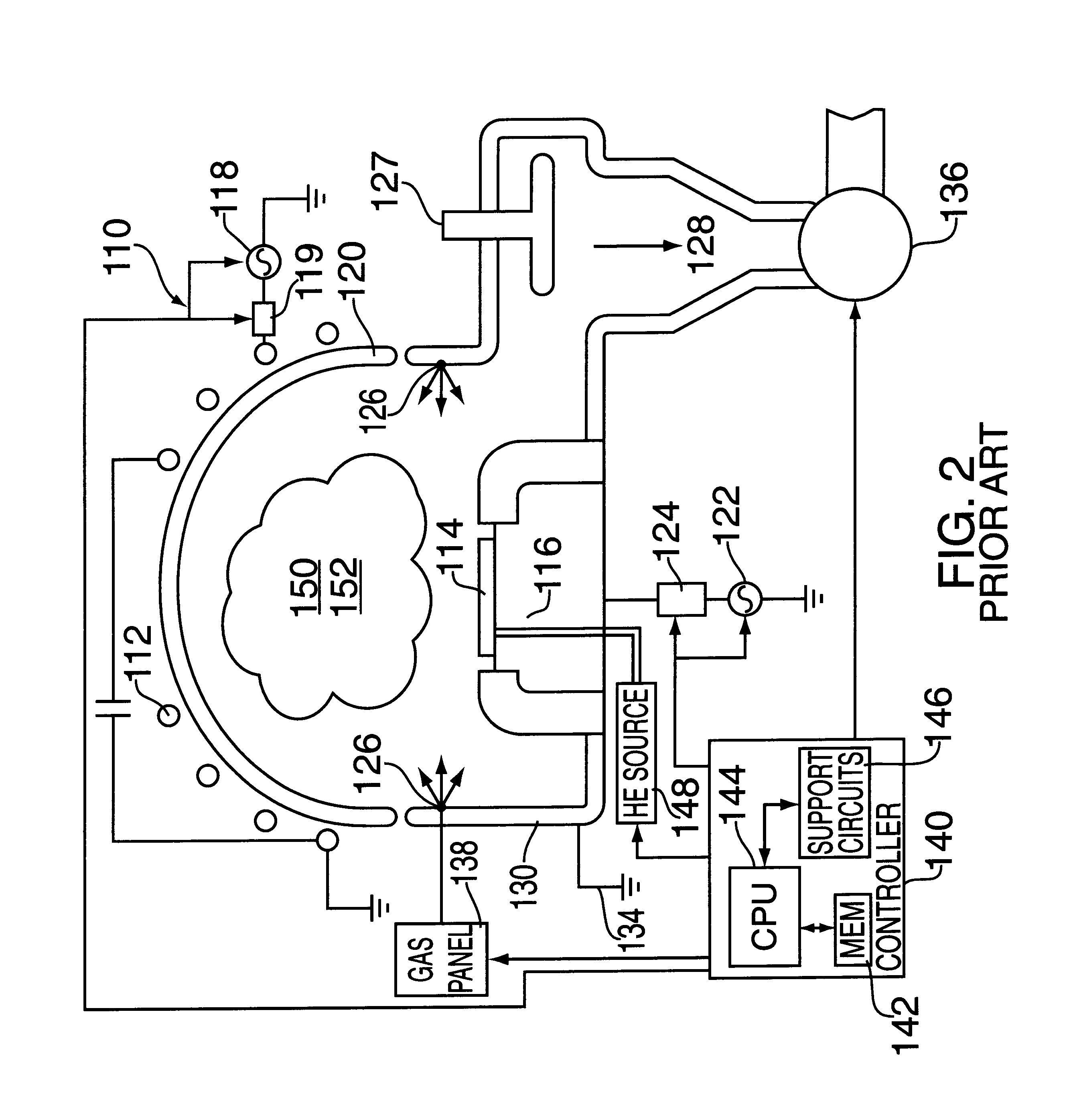

Thermal control is provided for an extraction electrode of an ion-beam producing system that prevents formation of deposits and unstable operation and enables use with ions produced from condensable vapors and with ion sources capable of cold and hot operation. Electrical heating of the extraction electrode is employed for extracting decaborane or octadecaborane ions. Active cooling during use with a hot ion source prevents electrode destruction, permitting the extraction electrode to be of heat-conductive and fluorine-resistant aluminum composition. The service lifetime of the system is enhanced by provisions for in-situ etch cleaning of the ion source and extraction electrode, using reactive halogen gases, and by having features that extend the service duration between cleanings, including accurate vapor flow control and accurate focusing of the ion beam optics. A remote plasma source delivers F or Cl ions to the de-energized ion source for the purpose of cleaning deposits in the ion source and the extraction electrode. These techniques enable long equipment uptime when running condensable feed gases such as sublimated vapors, and are particularly applicable for use with so-called cold ion sources and universal ion sources. Methods and apparatus are described which enable long equipment uptime when decaborane and octadecaborane are used as feed materials, as well as when vaporized elemental arsenic and phosphorus are used, and which serve to enhance beam stability during ion implantation.

Owner:SEMEQUIP

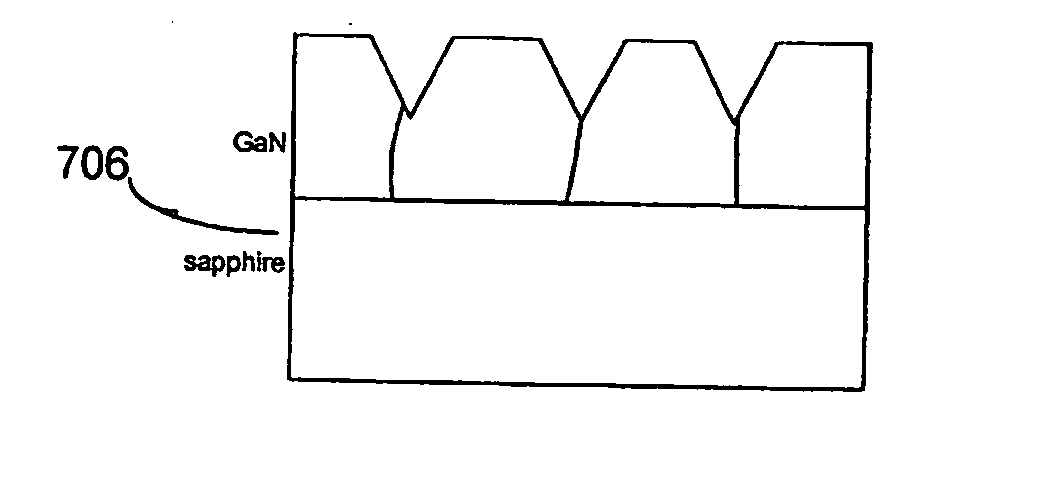

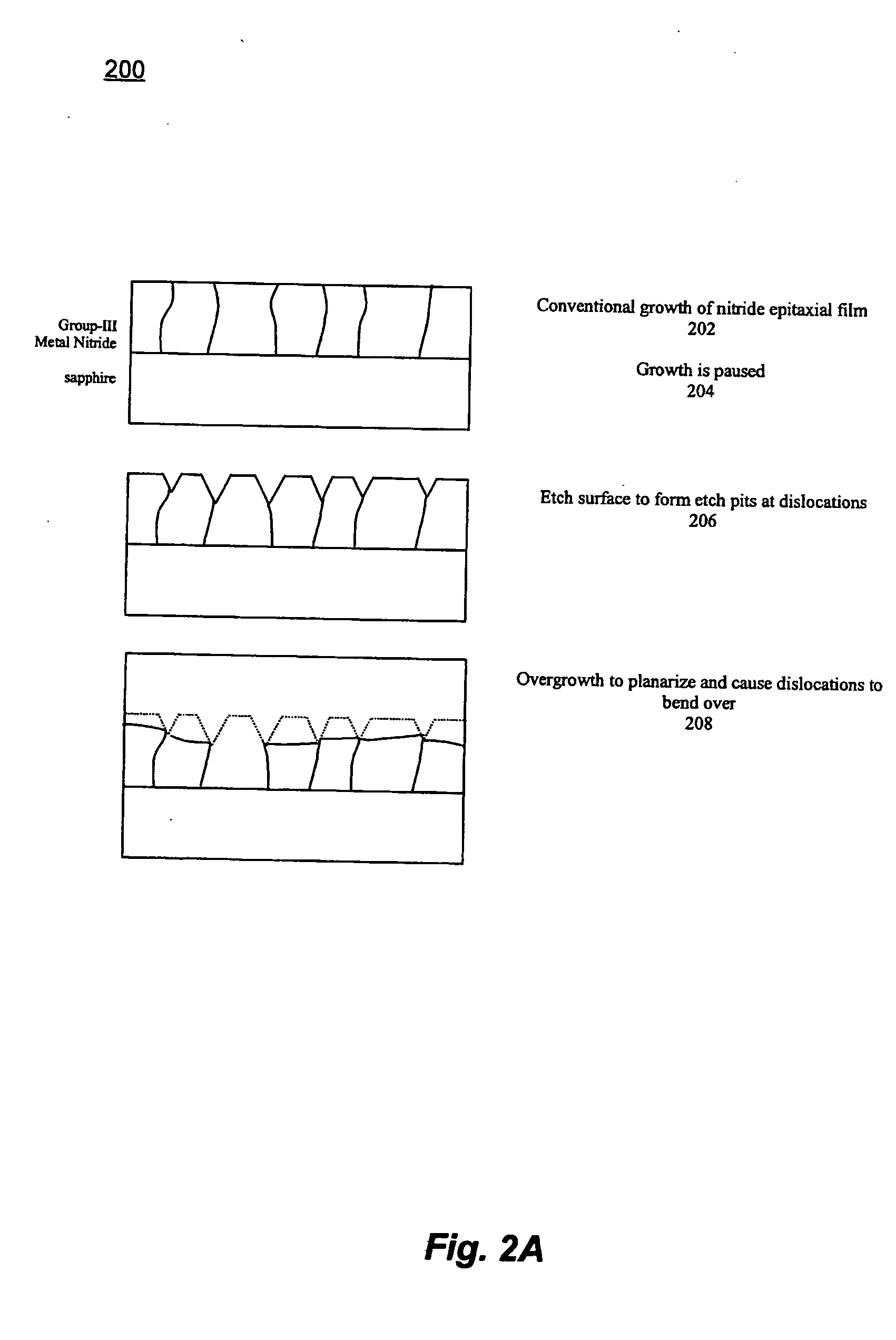

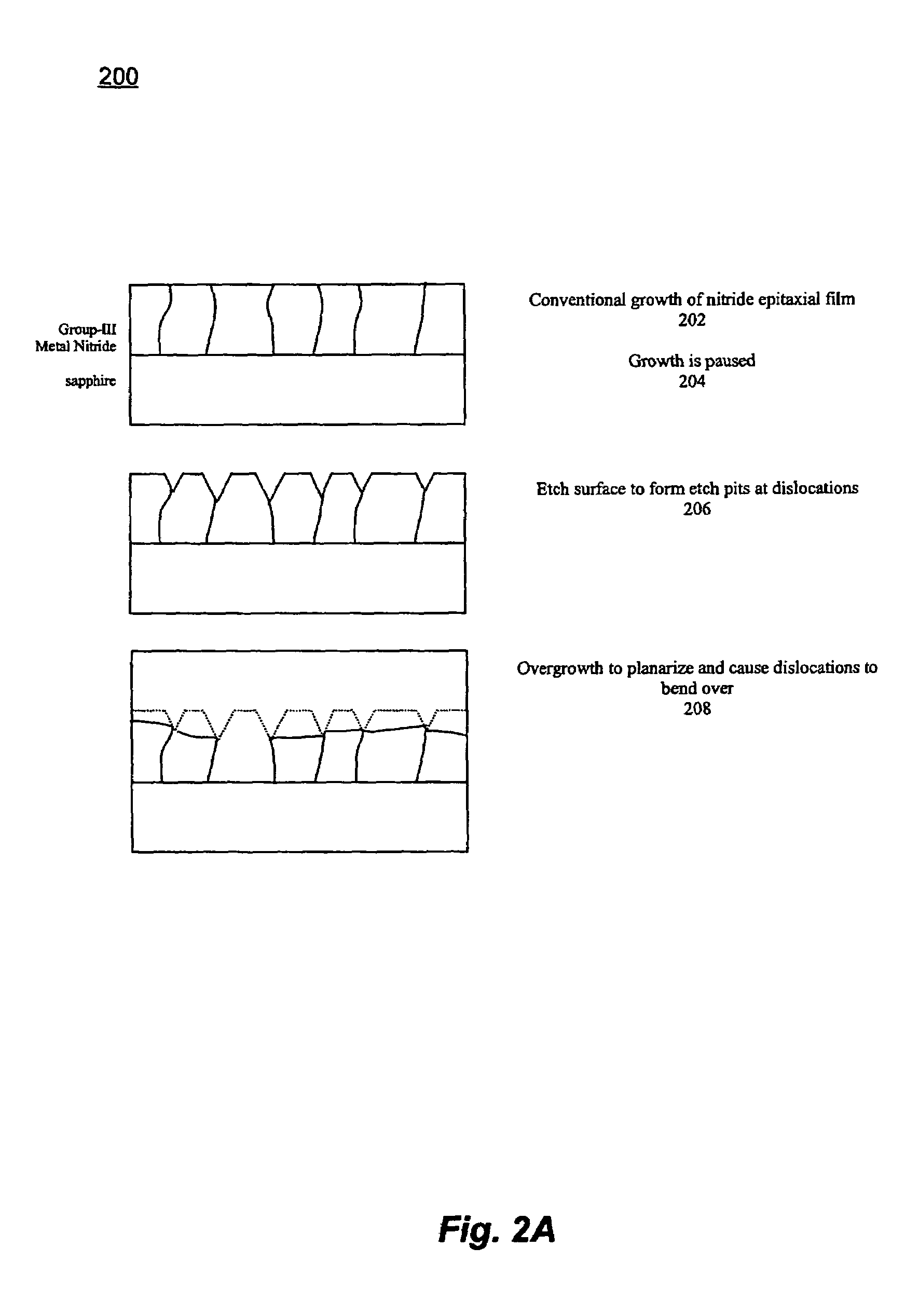

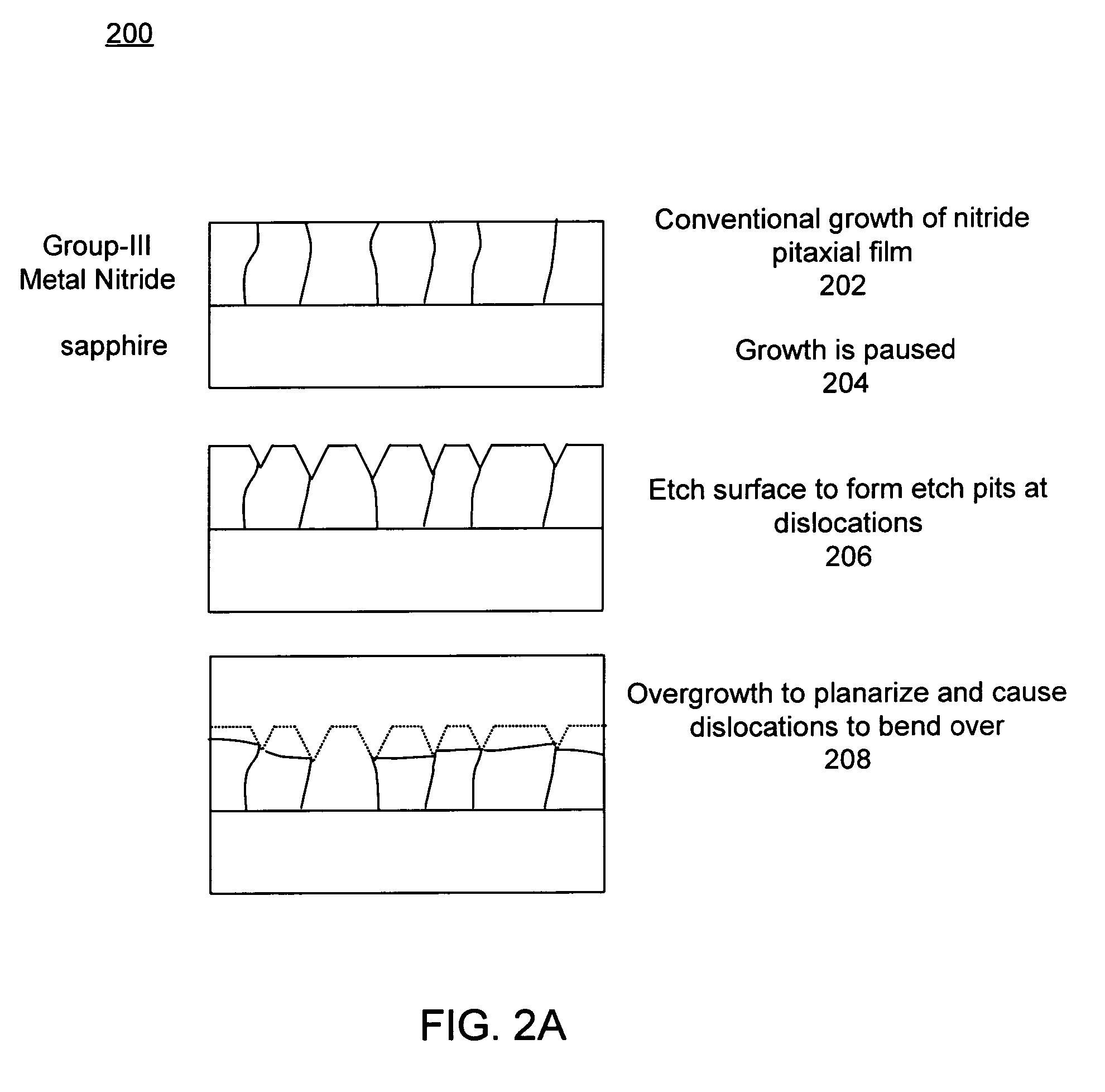

Dislocation-specific lateral epitaxial overgrowth to reduce dislocation density of nitride films

InactiveUS20070259504A1Reduce dislocation densityInhibit threading of the lattice mismatchPolycrystalline material growthBy zone-melting liquidsEtchingDislocation

In accordance with the present invention, improved methods for reducing the dislocation density of nitride epitaxial films are provided. Specifically, an in-situ etch treatment is provided to preferentially etch the dislocations of the nitride epitaxial layer to prevent threading of the dislocations through the nitride epitaxial layer. Subsequent to etching of the dislocations, an epitaxial layer overgrowth is performed. In certain embodiments, the etching of the dislocations occurs simultaneously with growth of the epitaxial layer. In other embodiments, a dielectric mask is deposited within the etch pits formed at the dislocations prior to the epitaxial layer overgrowth.

Owner:APPLIED MATERIALS INC

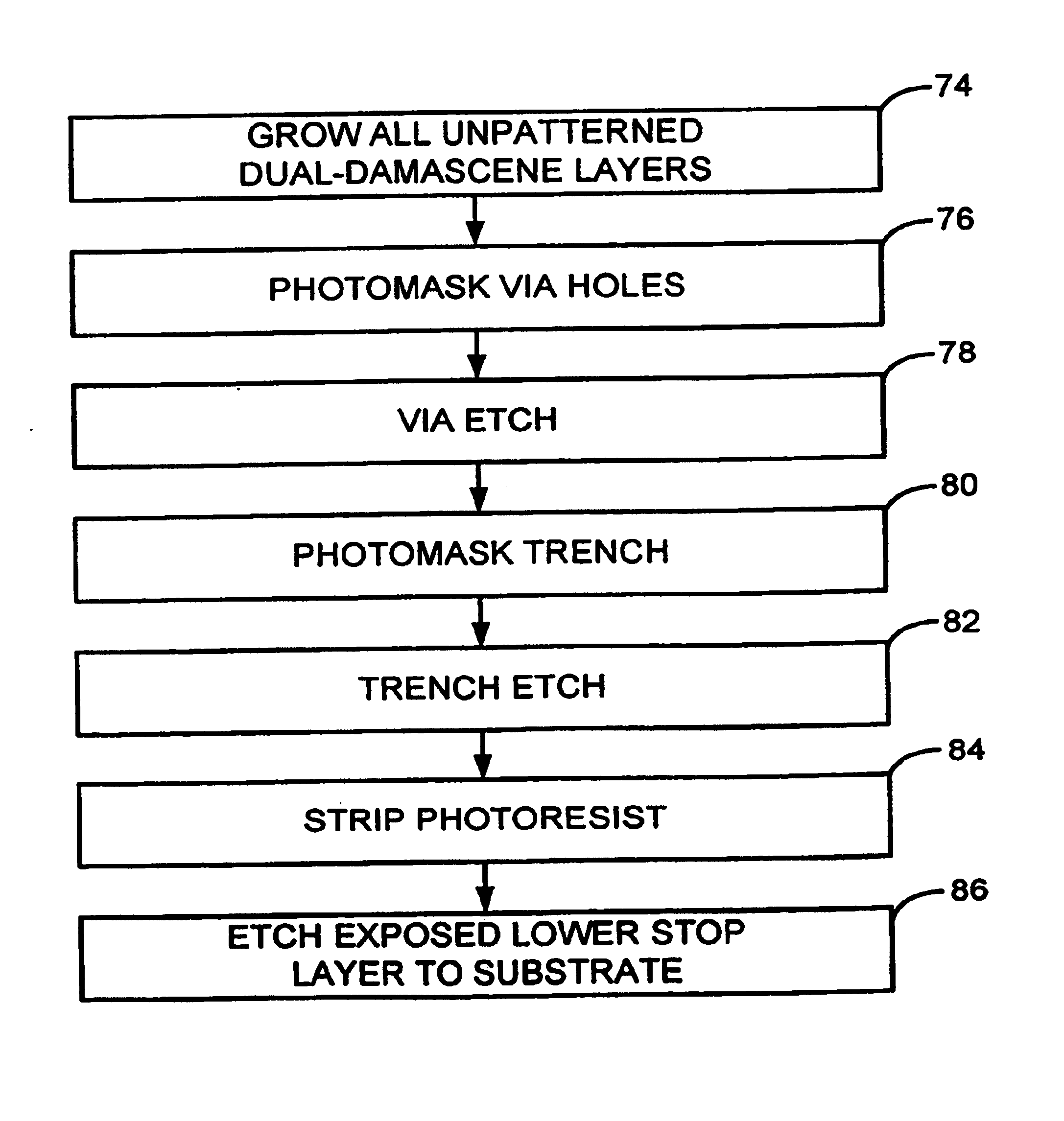

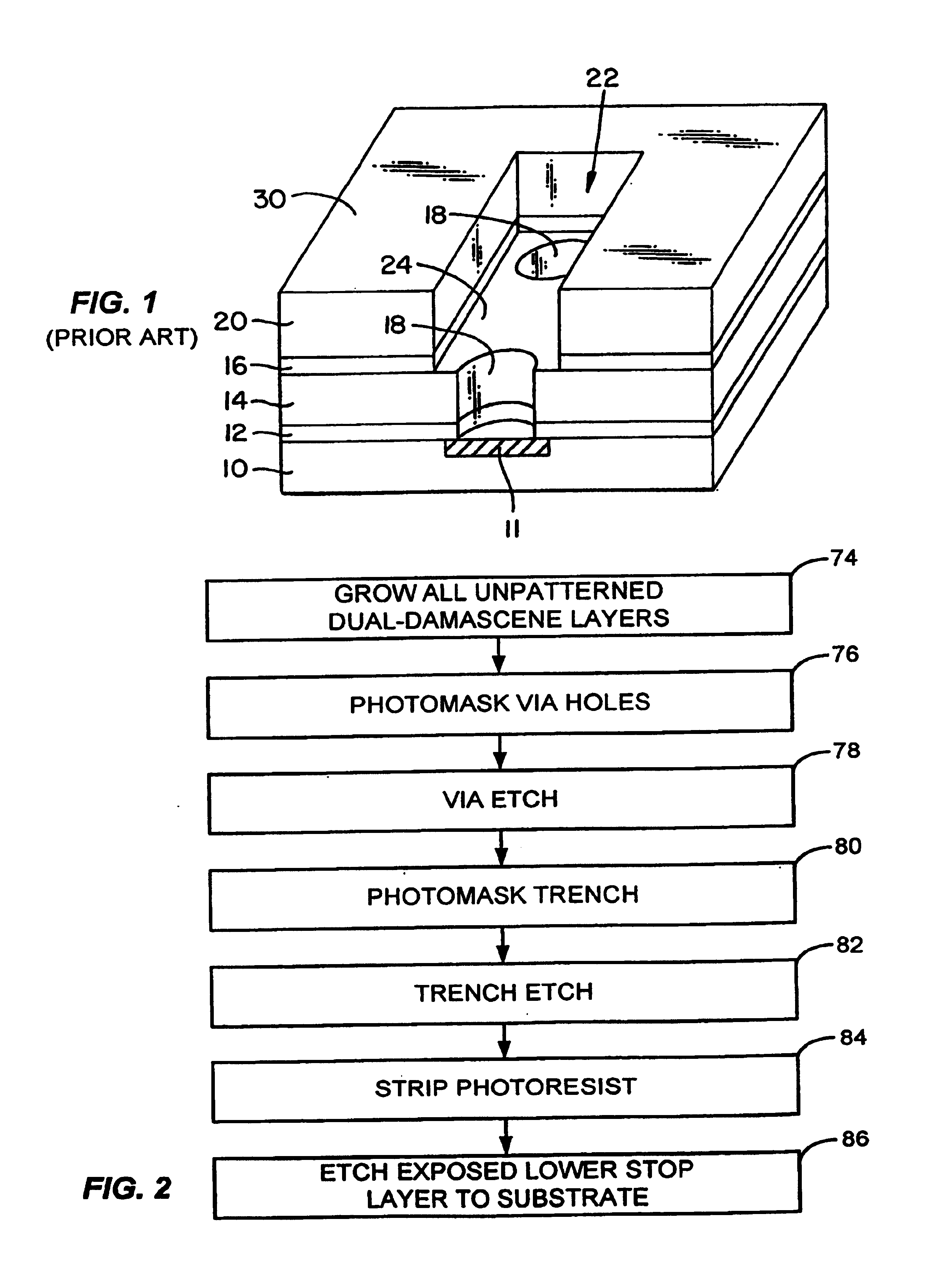

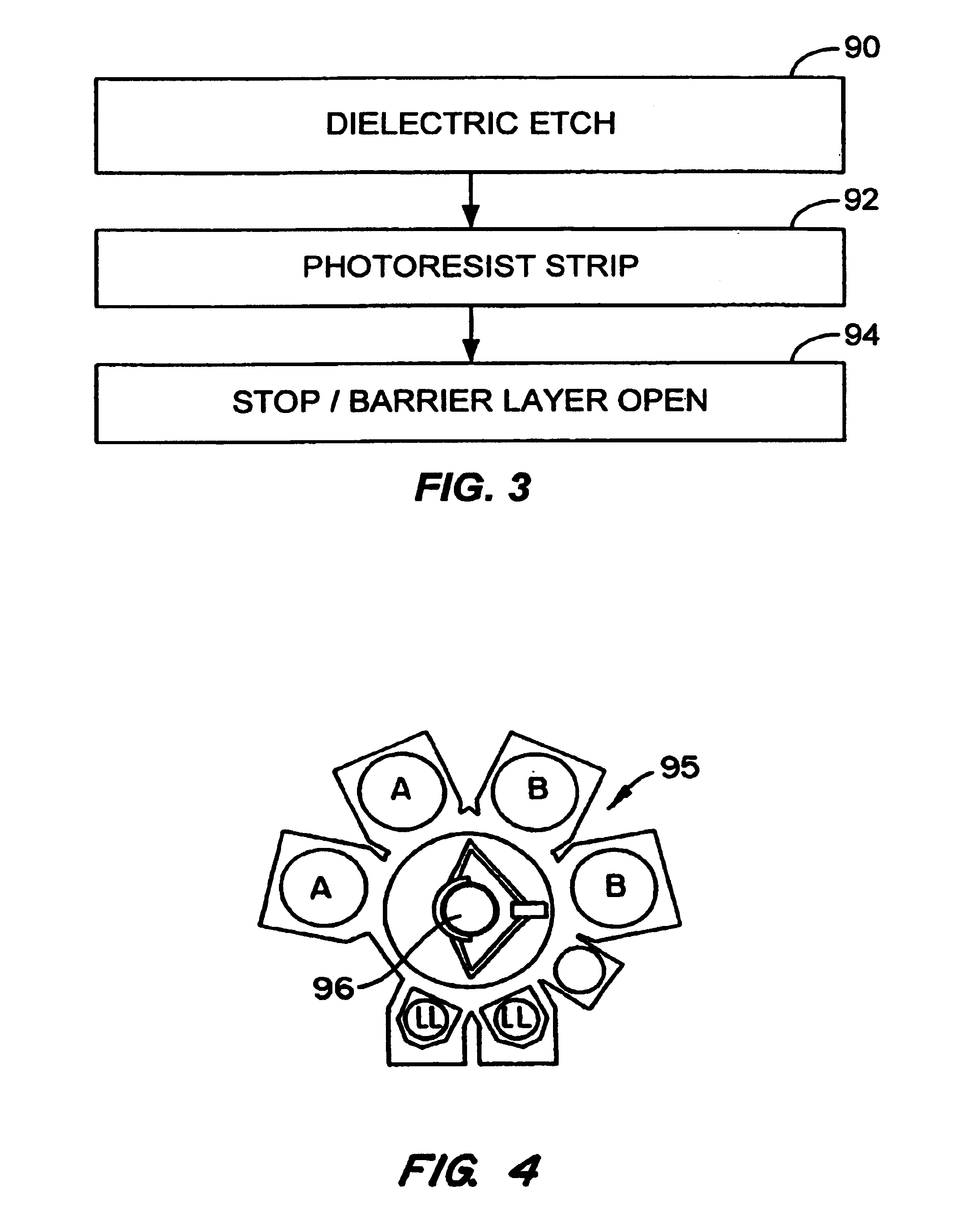

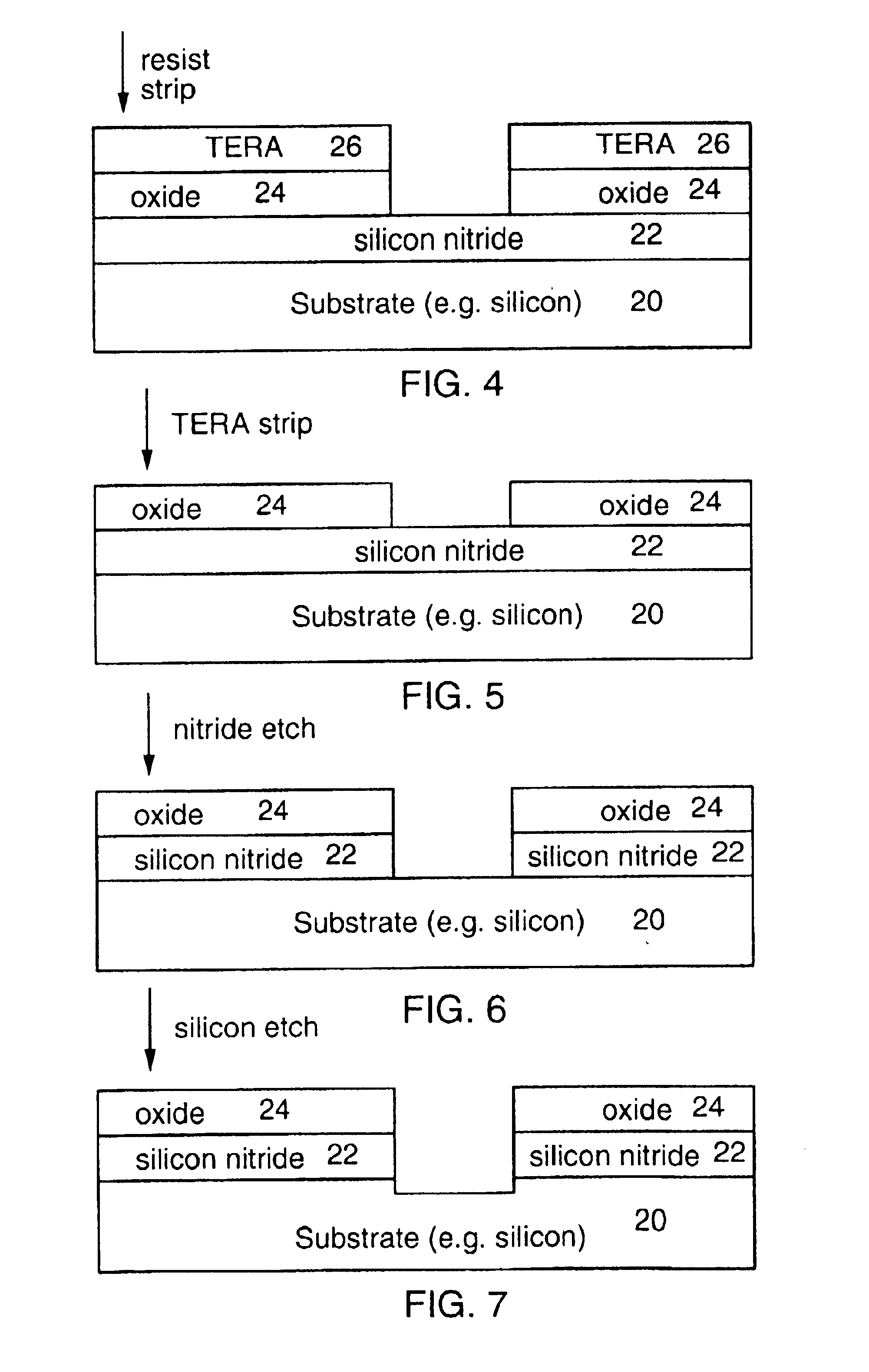

System level in-situ integrated dielectric etch process particularly useful for copper dual damascene

InactiveUS6949203B2Low costImproved etch resultElectric discharge tubesVacuum gauge using ionisation effectsResistReactive plasma

An integrated in situ etch process performed in a multichamber substrate processing system having first and second etching chambers. In one embodiment the first chamber includes an interior surface that has been roughened to at least 100 Ra and the second chamber includes an interior surface that has a roughness of less than about 32 Ra. The process includes transferring a substrate having formed thereon in a downward direction a patterned photoresist mask, a dielectric layer, a barrier layer and a feature in the substrate to be contacted into the first chamber where the dielectric layer is etched in a process that encourages polymer formation over the roughened interior surface of the chamber. The substrate is then transferred from the first chamber to the second chamber under vacuum conditions and, in the second chamber, is exposed to a reactive plasma such as oxygen to strip away the photoresist mask deposited over the substrate. After the photoresist mask is stripped, the barrier layer is etched through to the feature to be contacted in the second chamber of the multichamber substrate processing system using a process that discourages polymer formation over the relatively smooth interior surface of the second chamber. All three etching steps are performed in a system level in situ process so that the substrate is not exposed to an ambient between steps. In some embodiments the interior surface of the first chamber has a roughness between 100 and 200 Ra and in other embodiments the roughness of the first chamber's interior surface is between 110 and 160 Ra.

Owner:APPLIED MATERIALS INC

Method and apparatus for extracting ions from an ion source for use in ion implantation

InactiveUS20060272776A1Extended service lifeReduce downtimeVacuum evaporation coatingSemiconductor/solid-state device manufacturingRemote plasmaActive cooling

Thermal control is provided for an extraction electrode of an ion-beam producing system that prevents formation of deposits and unstable operation and enables use with ions produced from condensable vapors and with ion sources capable of cold and hot operation. Electrical heating of the extraction electrode is employed for extracting decaborane or octadecaborane ions. Active cooling during use with a hot ion source prevents electrode destruction, permitting the extraction electrode to be of heat-conductive and fluorine-resistant aluminum composition. The service lifetime of the system is enhanced by provisions for in-situ etch cleaning of the ion source and extraction electrode, using reactive halogen gases, and by having features that extend the service duration between cleanings, including accurate vapor flow control and accurate focusing of the ion beam optics. A remote plasma source delivers F or Cl ions to the de-energized ion source for the purpose of cleaning deposits in the ion source and the extraction electrode. These techniques enable long equipment uptime when running condensable feed gases such as sublimated vapors, and are particularly applicable for use with so-called cold ion sources and universal ion sources. Methods and apparatus are described which enable long equipment uptime when decaborane and octadecaborane are used as feed materials, as well as when vaporized elemental arsenic and phosphorus are used, and which serve to enhance beam stability during ion implantation.

Owner:SEMEQUIP

Method and apparatus for extracting ions from an ion source for use in ion implantation

InactiveUS20070108395A1Extended service lifeReduce downtimeVacuum evaporation coatingSputtering coatingRemote plasmaActive cooling

Thermal control is provided for an extraction electrode of an ion-beam producing system that prevents formation of deposits and unstable operation and enables use with ions produced from condensable vapors and with ion sources capable of cold and hot operation. Electrical heating of the extraction electrode is employed for extracting decaborane or octadecaborane ions. Active cooling during use with a hot ion source prevents electrode destruction, permitting the extraction electrode to be of heat-conductive and fluorine-resistant aluminum composition. The service lifetime of the system is enhanced by provisions for in-situ etch cleaning of the ion source and extraction electrode, using reactive halogen gases, and by having features that extend the service duration between cleanings, including accurate vapor flow control and accurate focusing of the ion beam optics. A remote plasma source delivers F or Cl ions to the de-energized ion source for the purpose of cleaning deposits in the ion source and the extraction electrode. These techniques enable long equipment uptime when running condensable feed gases such as sublimated vapors, and are particularly applicable for use with so-called cold ion sources and universal ion sources. Methods and apparatus are described which enable long equipment uptime when decaborane and octadecaborane are used as feed materials, as well as when vaporized elemental arsenic and phosphorus are used, and which serve to enhance beam stability during ion implantation.

Owner:SEMEQUIP

Method And Apparatus For Extending Equipment Uptime In Ion Implantation

InactiveUS20070210260A1Extended service lifeReduce equipment downtimeVacuum evaporation coatingElectric arc lampsIon implantationThermal control

The service lifetime of an ion source is enhanced or prolonged by the source having provisions for in-situ etch cleaning of the ion source and of an extraction electrode, using reactive halogen gases (F or Cl), and by having features that extend the service duration between cleanings. The latter include accurate vapor flow control, accurate focusing of the ion beam optics, and thermal control of the extraction electrode that prevents formation of deposits or prevents electrode destruction. An apparatus comprised of an ion source for generating dopant ions for semiconductor wafer processing is coupled to a remote plasma source which delivers F or Cl ions to the first ion source for the purpose of cleaning deposits in the first ion source and the extraction electrode. These methods and apparatus enable long equipment uptime when running condensable feed gases such as sublimated vapor sources, and are particularly applicable for use with so-called cold ion sources. Methods and apparatus are described which enable long equipment uptime when decaborane and octadecarborane are used as feed materials, as well as when vaporized elemental arsenic and phosphorus are used, and which serve to enhance beam stability during ion implantation.

Owner:SEMEQUIP

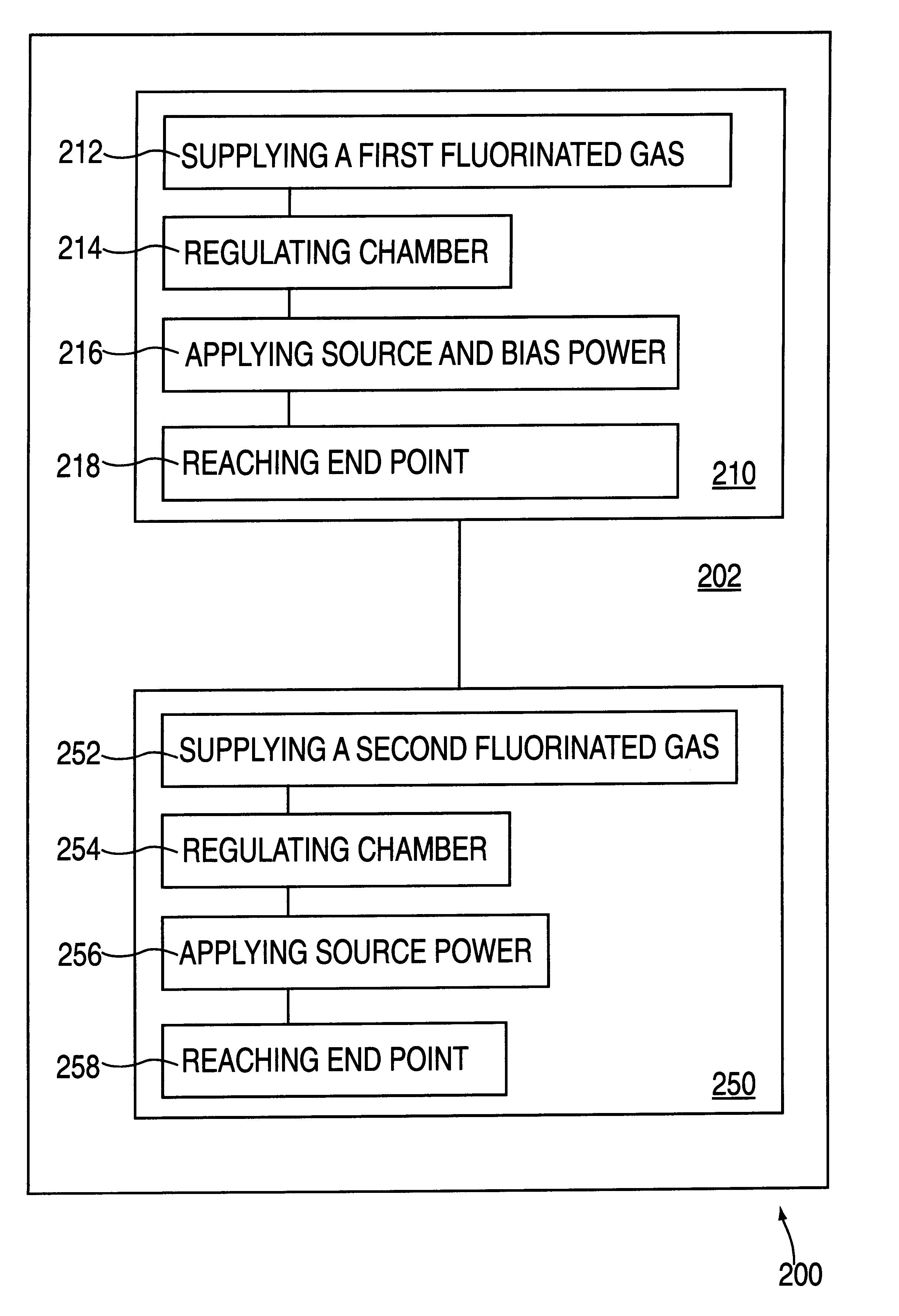

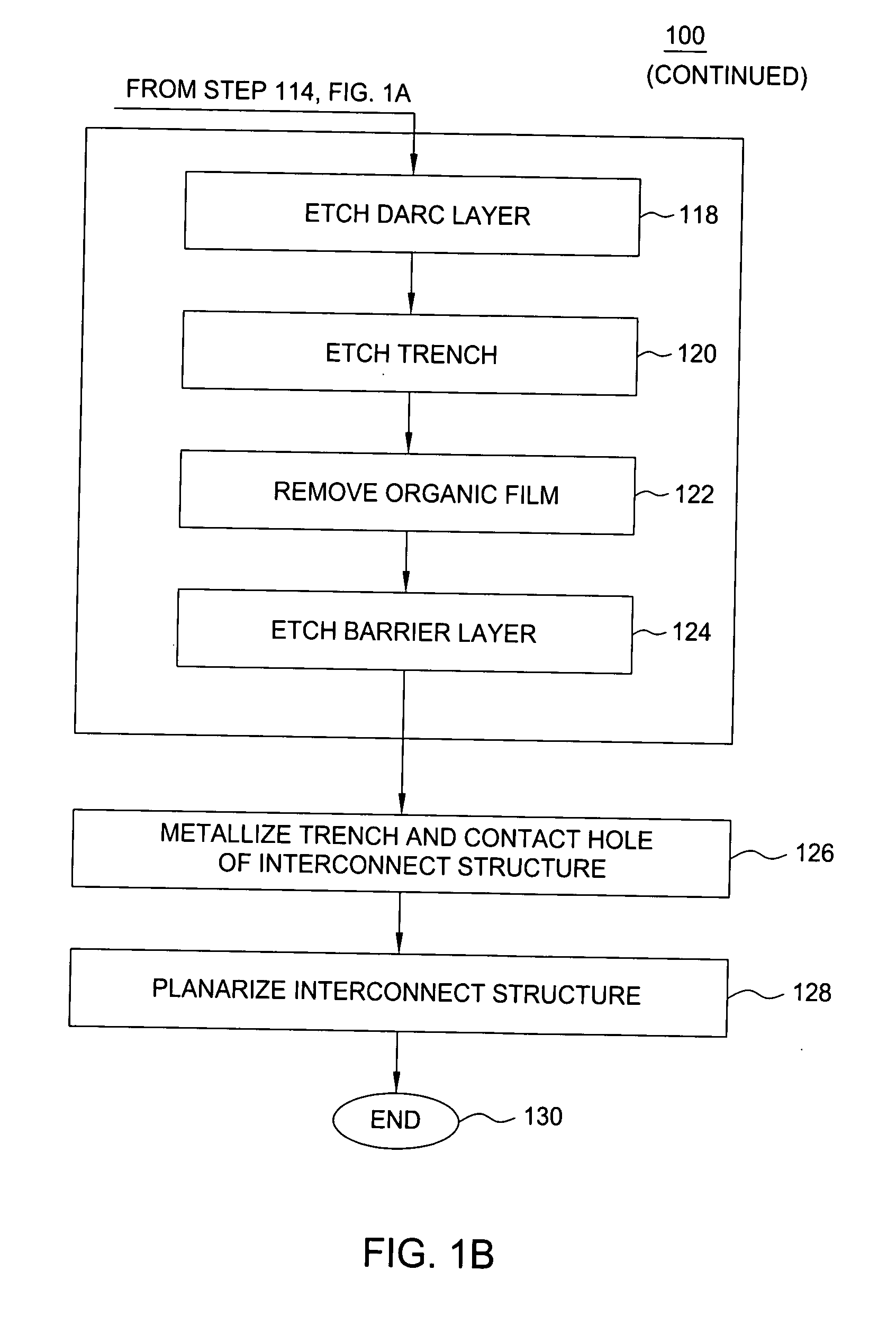

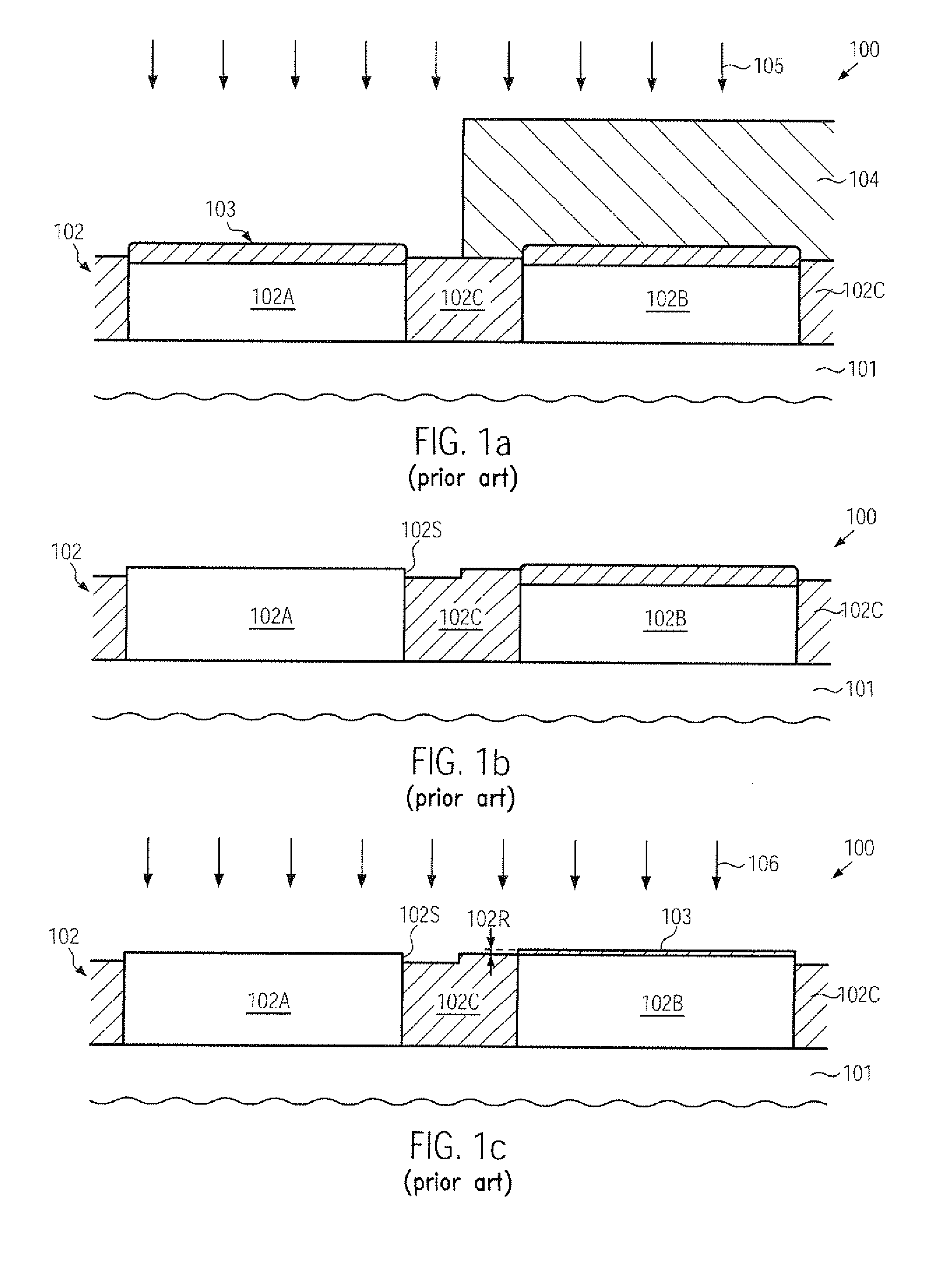

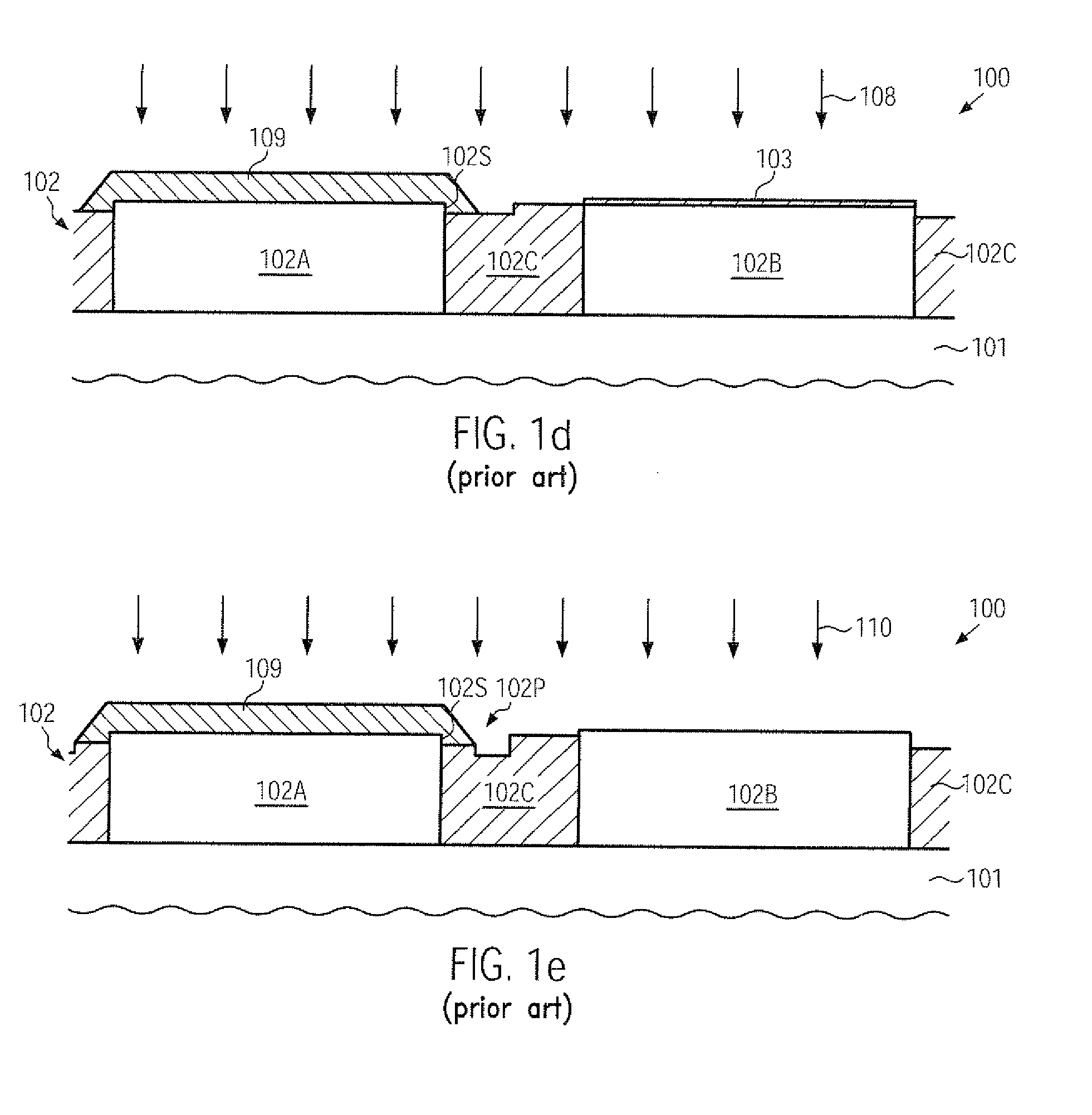

In situ Etching of inorganic dielectric anti-reflective coating from a substrate

InactiveUS6103632AImprove etch selectivityEtching precisionSemiconductor/solid-state device manufacturingAnti-reflective coatingComputational physics

The present invention is embodied in a method and apparatus for etching dielectric layers and inorganic ARC's without the need for removing the substrate being processed from the processing chamber and without the need for intervening processing steps such as chamber cleaning operations (in situ process). A layer and / or a multi-layer film deposited on a substrate, such as silicon, is located within a processing chamber. The substrate has a base, an underlying layer above the base, an overlying layer above the underlying layer, and a top dielectric anti-reflective coating (DARC) layer formed on the overlying layer. In the preferred method, first, the DARC layer and the overlying layer is etched by a first process gas. Next, the underlying layer is etched by a second process gas.

Owner:APPLIED MATERIALS INC

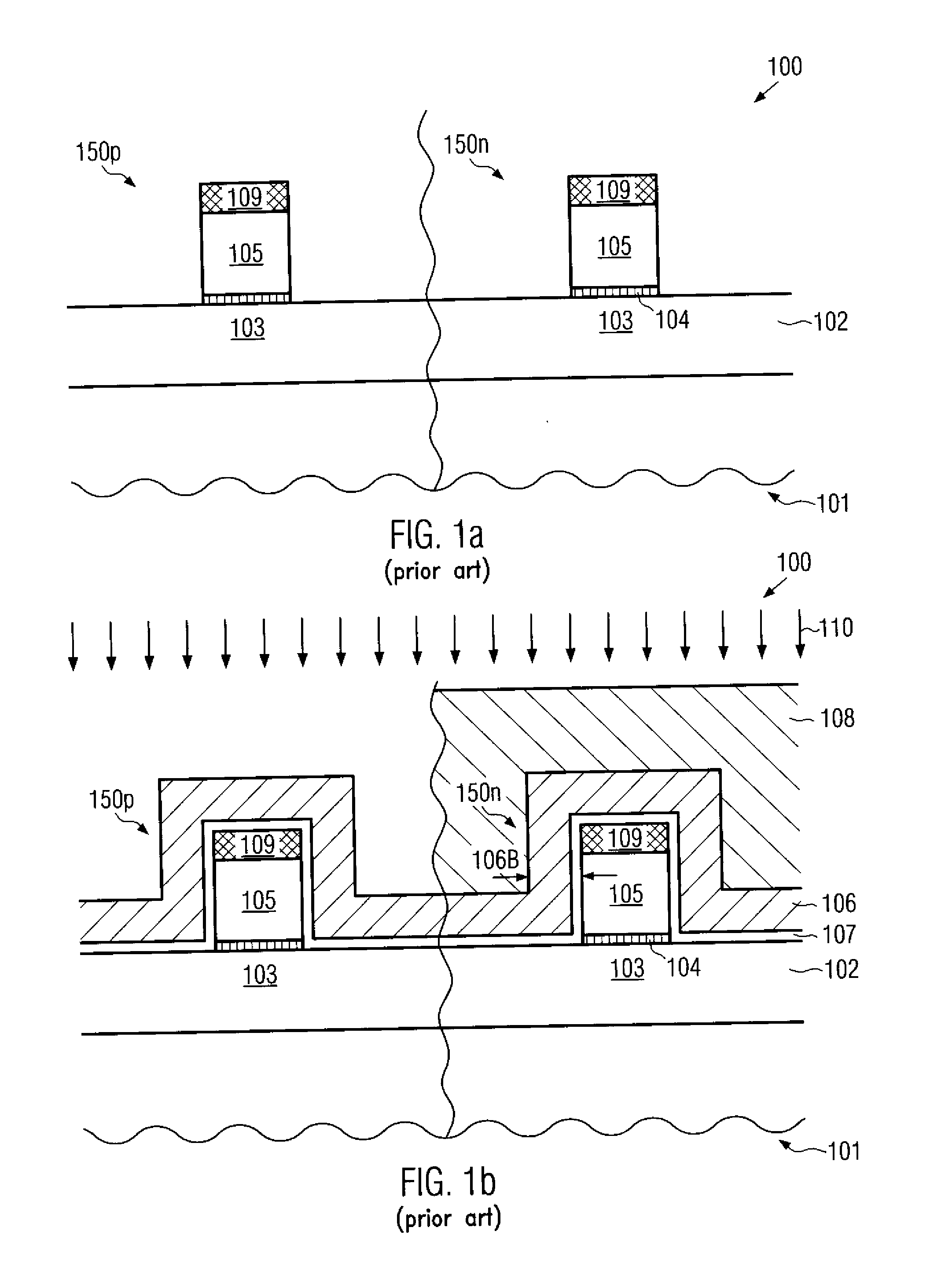

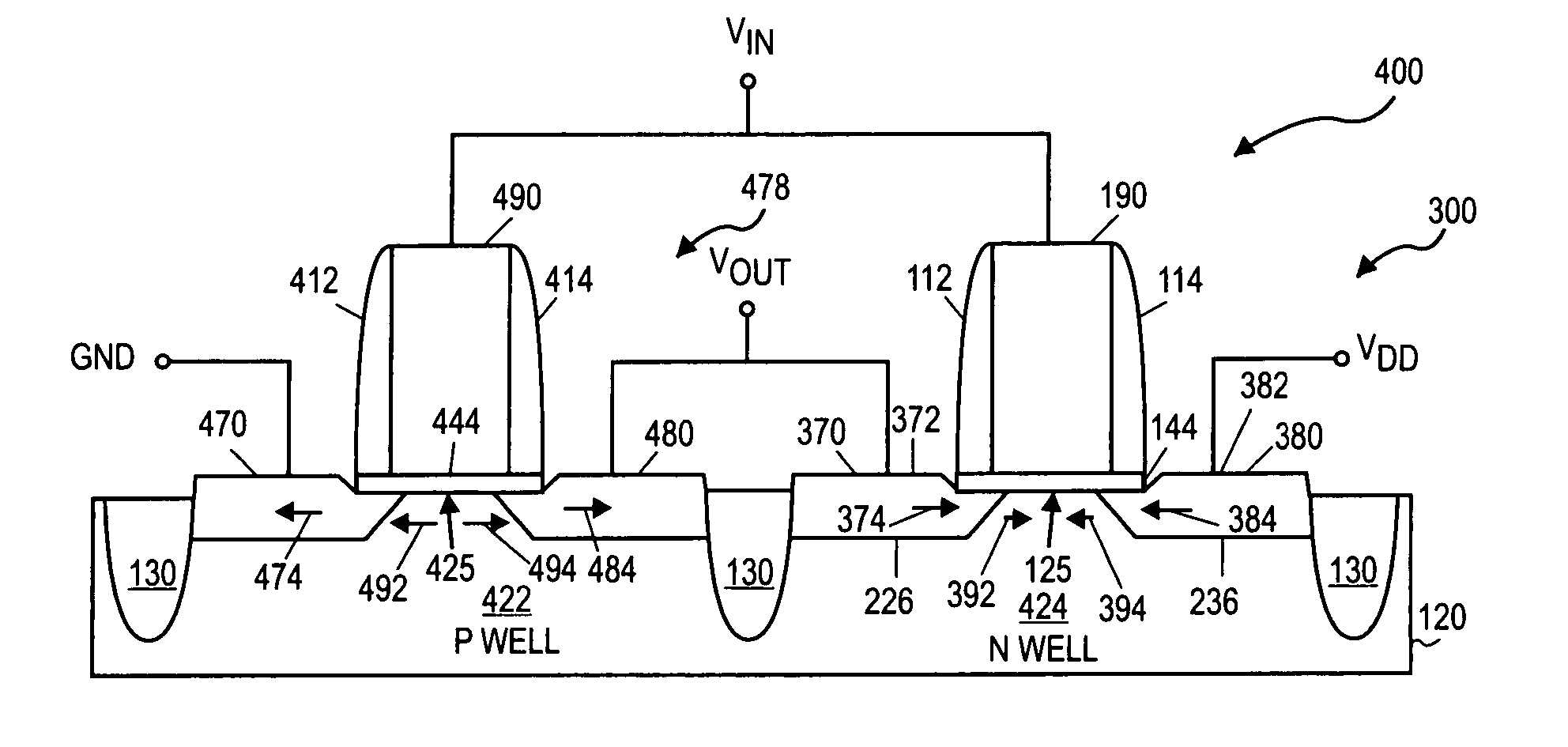

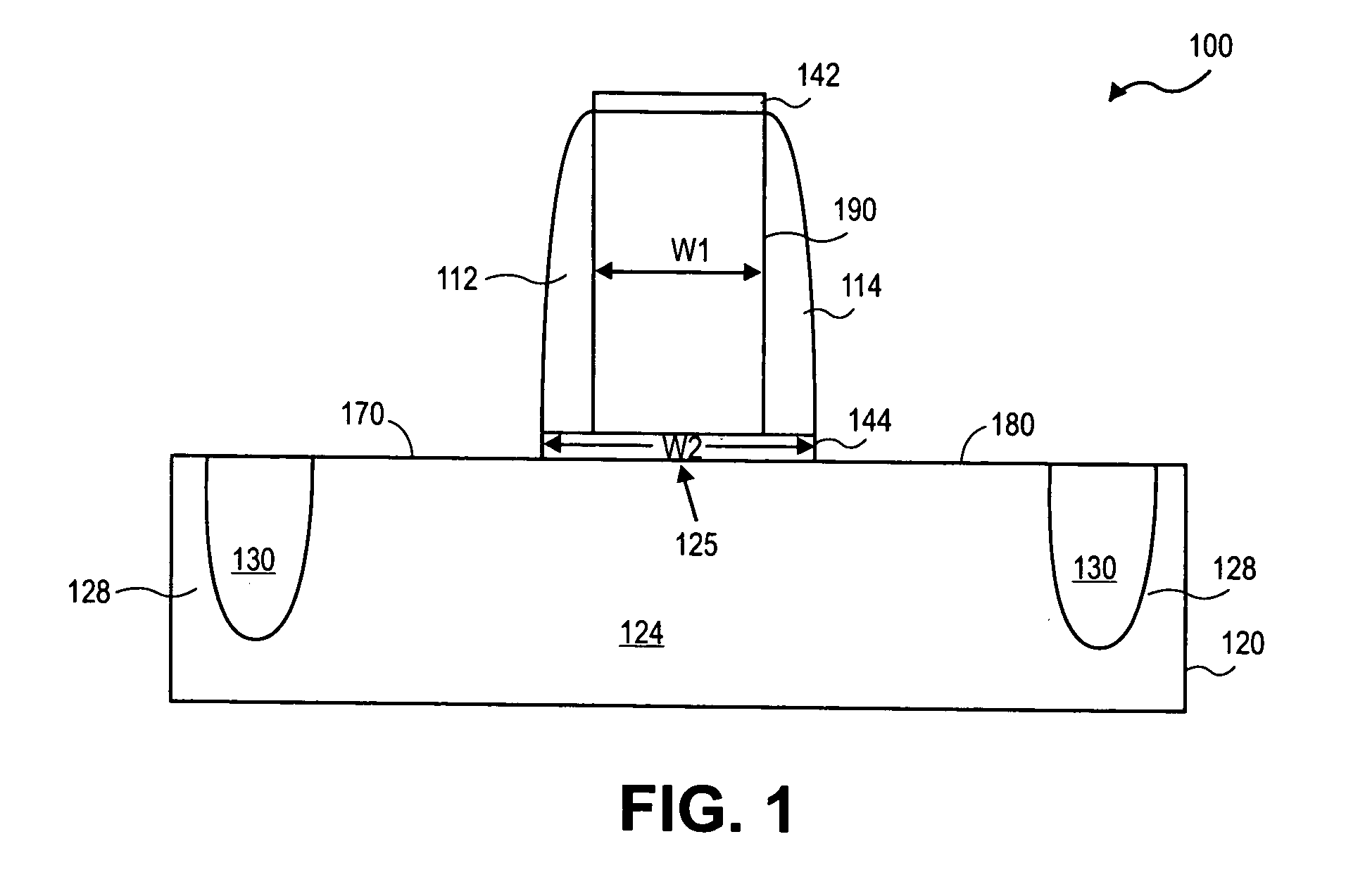

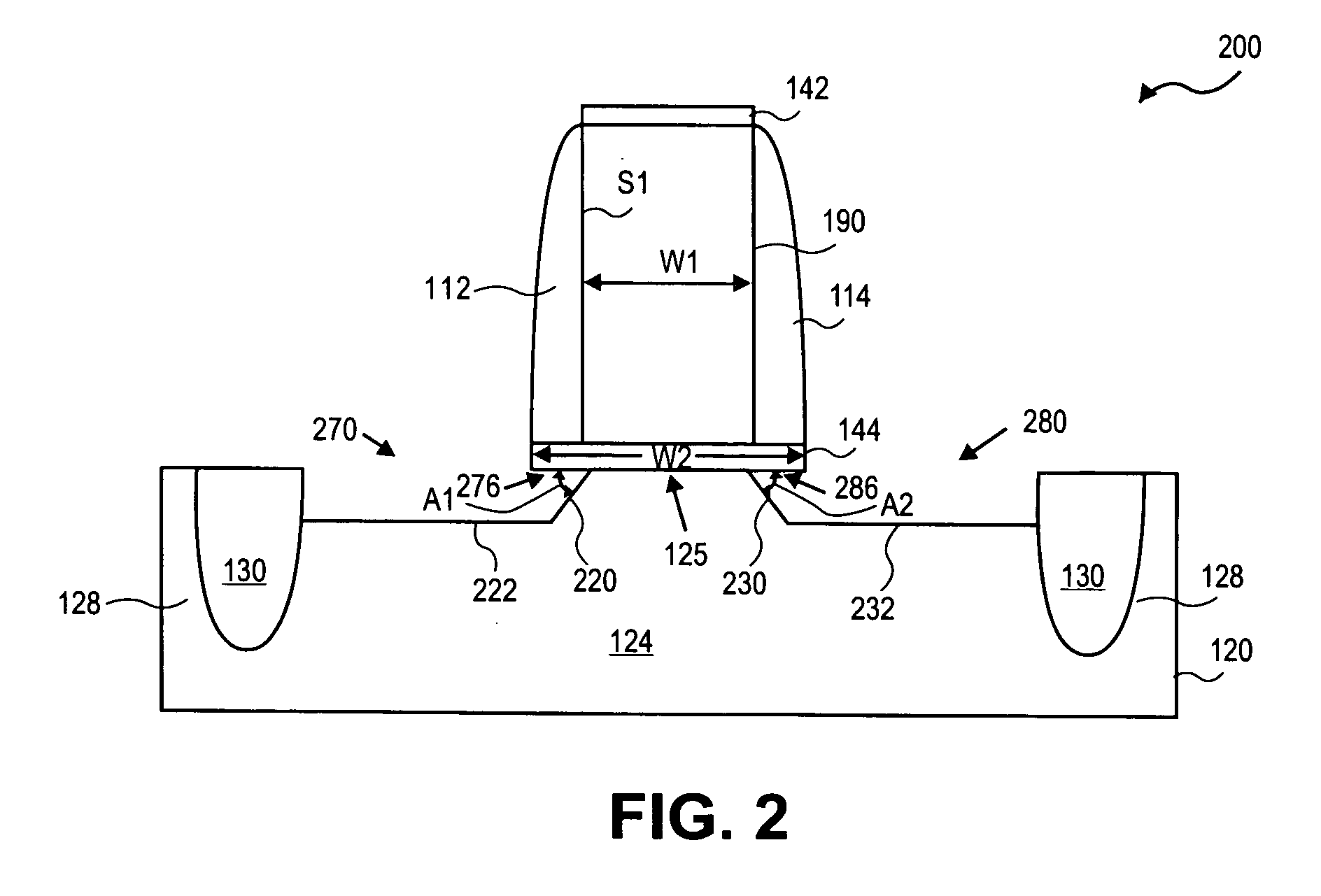

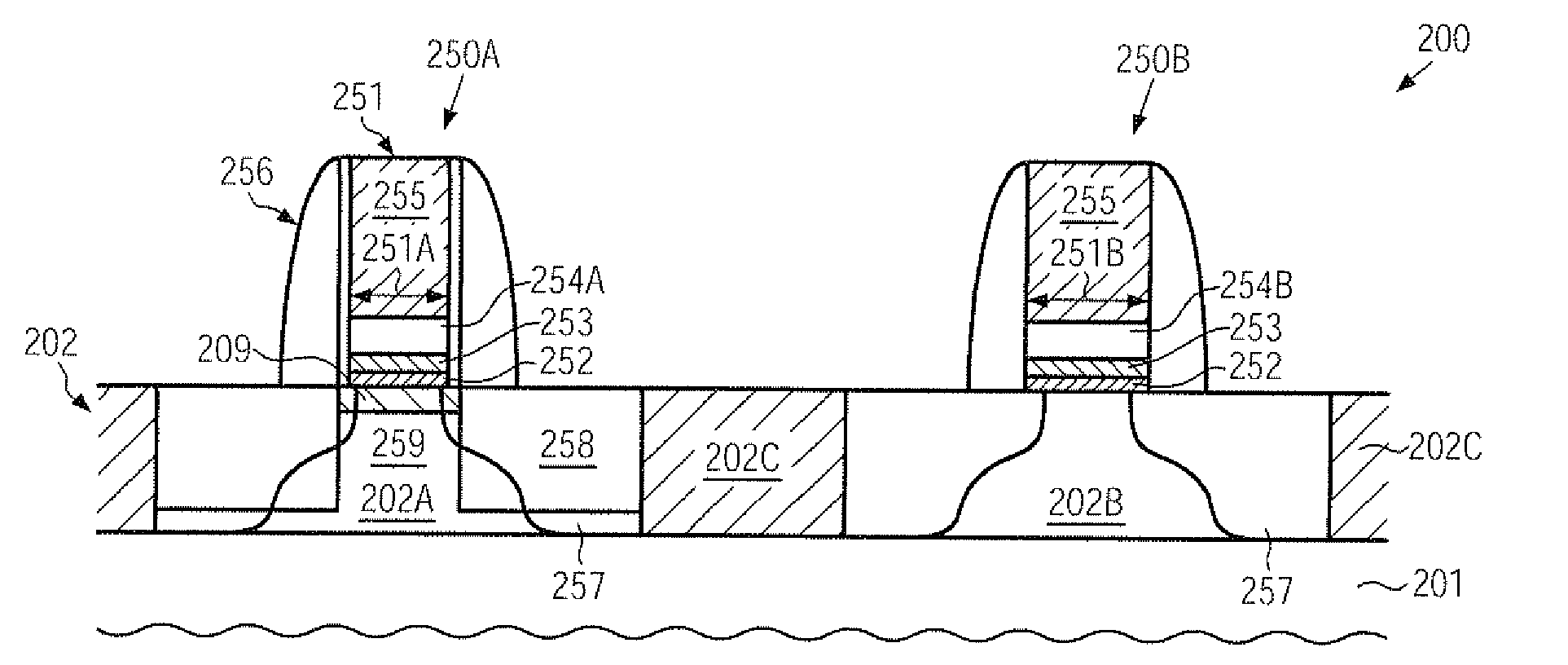

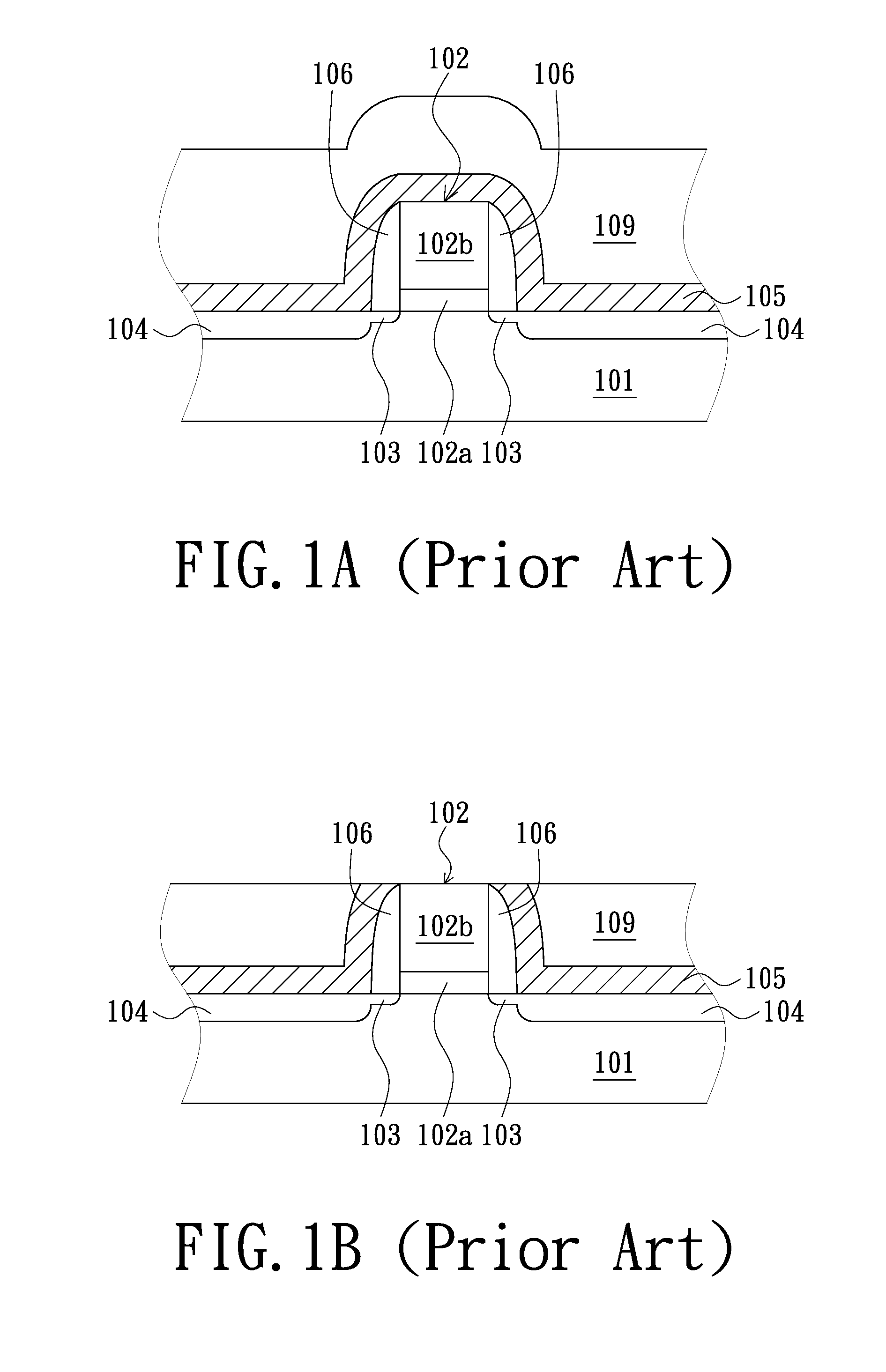

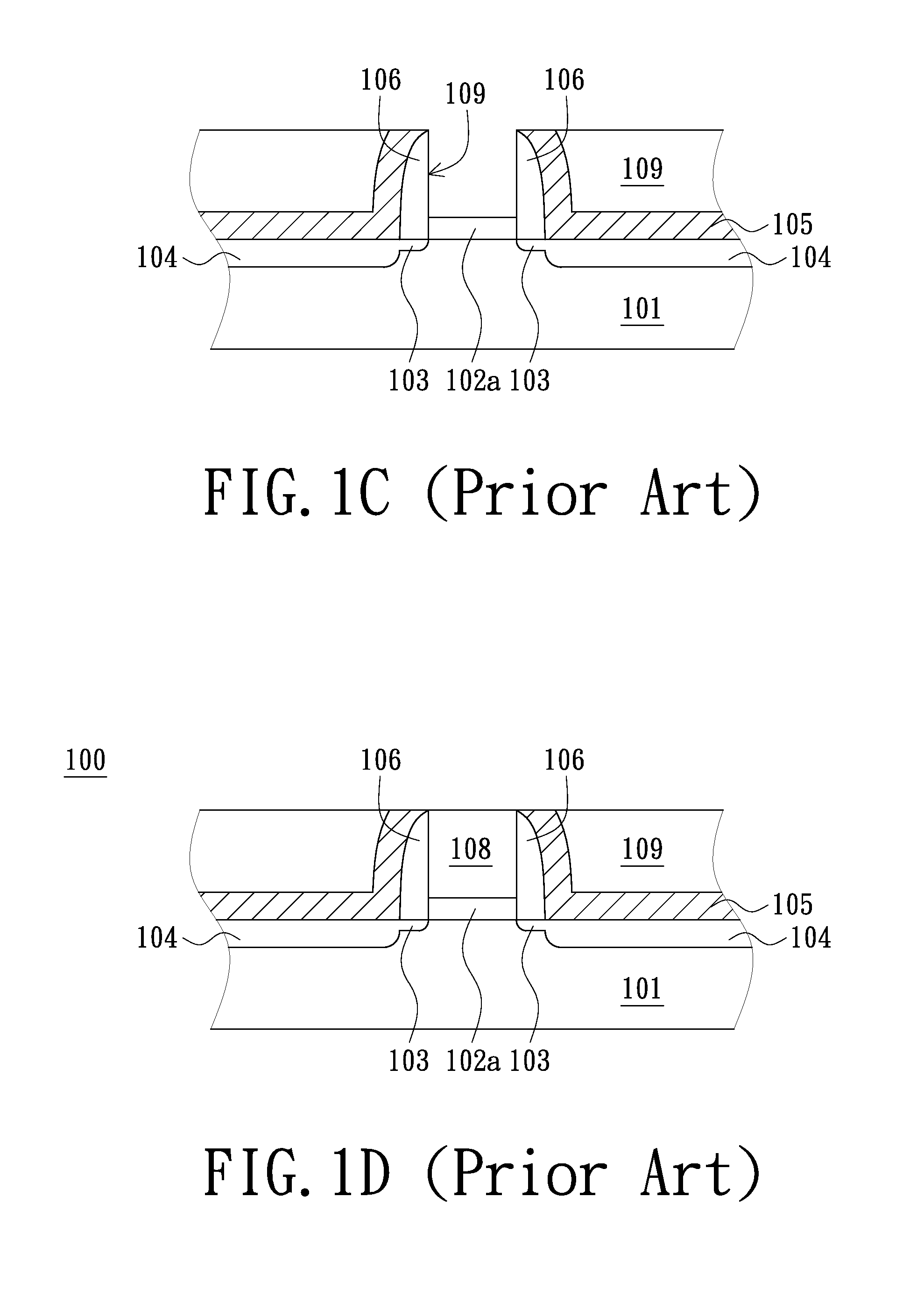

Method for forming embedded strained drain/source regions based on a combined spacer and cavity etch process

ActiveUS20070232006A1Increased processing flexibilityLess complexSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringAnisotropic etching

By patterning a spacer layer stack and etching a cavity in an in situ etch process, the process complexity, as well as the uniformity, during the formation of embedded strained semiconductor layers may be significantly enhanced. In an initial phase, the spacer layer stack may be patterned on the basis of an anisotropic etch step with a high degree of uniformity, since a selectivity between individual stack layers may not be necessary. Thereafter, a cleaning process may be performed followed by a cavity etch process, wherein a reduced over-etch time during the spacer patterning process significantly contributes to the uniformity of the finally obtained cavities, while the in situ nature of the process also provides a reduced overall process time.

Owner:INNOVATIVE FOUNDRY TECH LLC

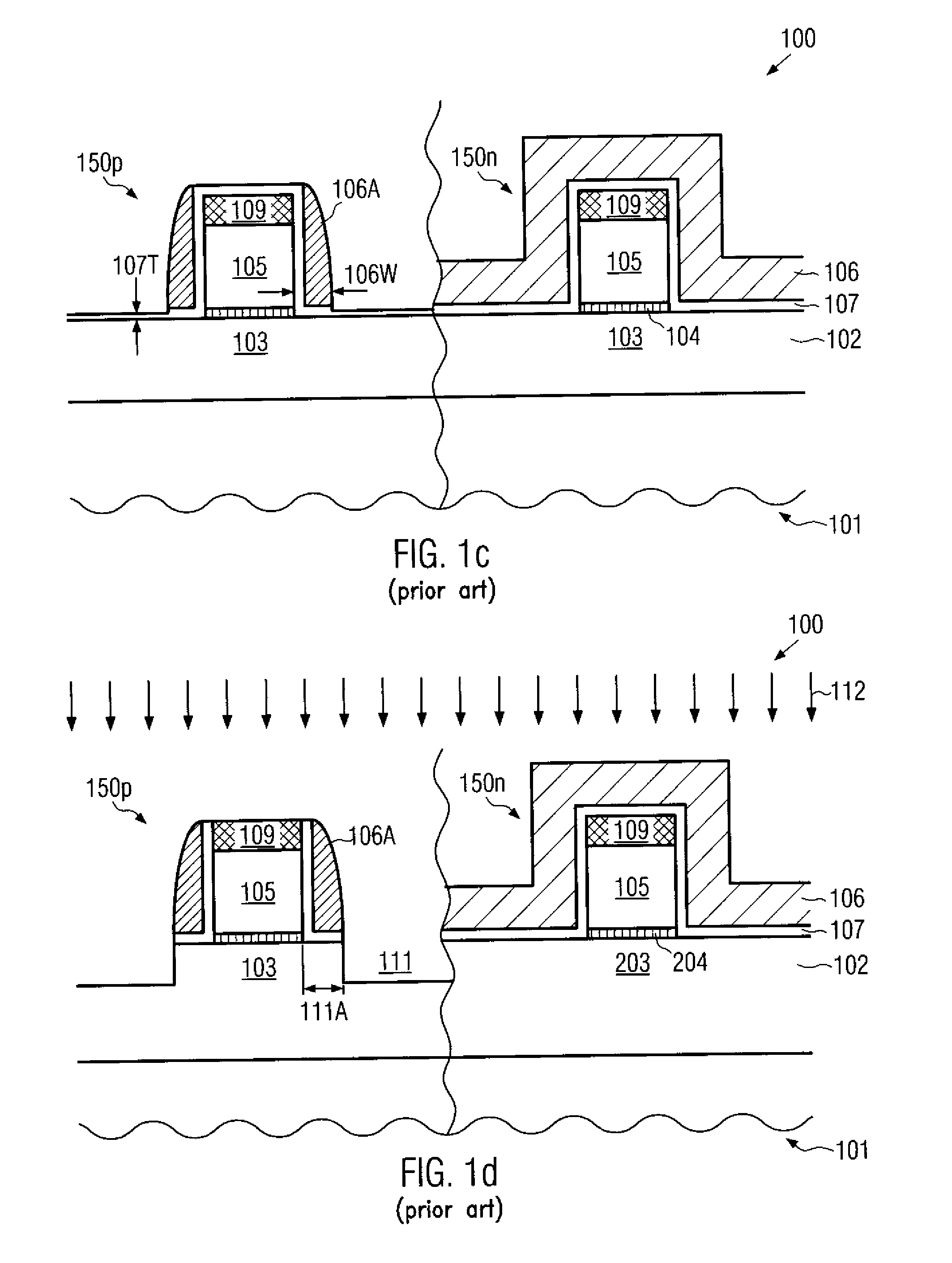

Method and apparatus for sequentially etching a wafer using anisotropic and isotropic etching

InactiveUS6221784B1Decorative surface effectsSemiconductor/solid-state device manufacturingFluorinated gasesAnisotropic etching

An apparatus and method for in-situ etching of a substrate comprising both a polysilicon layer and an overlying dielectric layer. An embodiment of the method comprises an anisotropic etch of the dielectric layer in a chamber using a first fluorinated gas (such as CF4, NF3, SF6, and the like) as an etch gas to expose at least a portion of underlying polysilicon layer. Following the anisotropic etch and without removing the substrate from the chamber, i.e., in situ, an isotropic etch is preformed on the underlying polysilicon layer using a second fluorinated gas (such as CF4, NF3, SF6, and the like) as an etch gas.

Owner:APPLIED MATERIALS INC

CMOS transistor junction regions formed by a CVD etching and deposition sequence

ActiveUS20070105331A1Semiconductor/solid-state device manufacturingNanotechnologyCMOSDriving current

This invention adds to the art of replacement source-drain cMOS transistors. Processes may involve etching a recess in the substrate material using one equipment set, then performing deposition in another. Disclosed is a method to perform the etch and subsequent deposition in the same reactor without atmospheric exposure. In-situ etching of the source-drain recess for replacement source-drain applications provides several advantages over state of the art ex-situ etching. Transistor drive current is improved by: (1) Eliminating contamination of the silicon-epilayer interface when the as-etched surface is exposed to atmosphere and (2) Precise control over the shape of the etch recess. Deposition may be done by a variety of techniques including selective and non-selective methods. In the case of blanket deposition, a measure to avoid amorphous deposition in performance critical regions is also presented.

Owner:DAEDALUS PRIME LLC

Dislocation-specific lateral epitaxial overgrowth to reduce dislocation density of nitride films

InactiveUS7560364B2Reduce dislocation densityInhibit threading of the lattice mismatchPolycrystalline material growthBy zone-melting liquidsEtchingNitride

In accordance with the present invention, improved methods for reducing the dislocation density of nitride epitaxial films are provided. Specifically, an in-situ etch treatment is provided to preferentially etch the dislocations of the nitride epitaxial layer to prevent threading of the dislocations through the nitride epitaxial layer. Subsequent to etching of the dislocations, an epitaxial layer overgrowth is performed. In certain embodiments, the etching of the dislocations occurs simultaneously with growth of the epitaxial layer. In other embodiments, a dielectric mask is deposited within the etch pits formed at the dislocations prior to the epitaxial layer overgrowth.

Owner:APPLIED MATERIALS INC

Method of preparing GaN monocrystal substrate in mechanical removal way

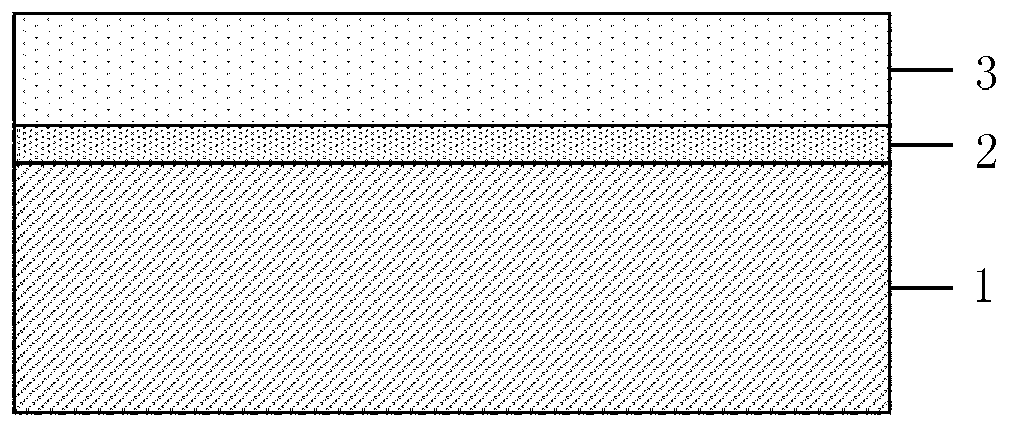

InactiveCN103021946AImprove crystal qualityAchieving Controlled SeparationPolycrystalline material growthAfter-treatment detailsSingle crystalGallium nitride

The invention discloses a method of preparing a GaN monocrystal substrate in a mechanical removal way. A thin film of layered structure is pre-deposited between a GaN monocrystal thick film and a substrate and the GaN monocrystal thick film and the substrate are separated in a horizontal sliding mode to obtain a complete large size self-supporting GaN monocrystal substrate by utilizing the fact that the van der Waals force of the film of layered structure between the substrate and the GaN monocrystal thick film is weak and easy to slip. According to the method of preparation GaN monocrystal substrate in a mechanical removal way, a low-cost preparation method is utilized to obtain the self-supporting GaN monocrystal substrate which is smooth in surface without cracks and high-quality in crystal, the controllable separation of the GaN monocrystal thick film and the heterogeneous substrate is achieved with simple device with no need of other complex technology devices like the laser lift-off and the lithography etching nanometer graphics and no need of in situ etching or laser lift-off components in the reaction chamber, and the process stability, easy control and application to industrial production can be obtained.

Owner:PEKING UNIV

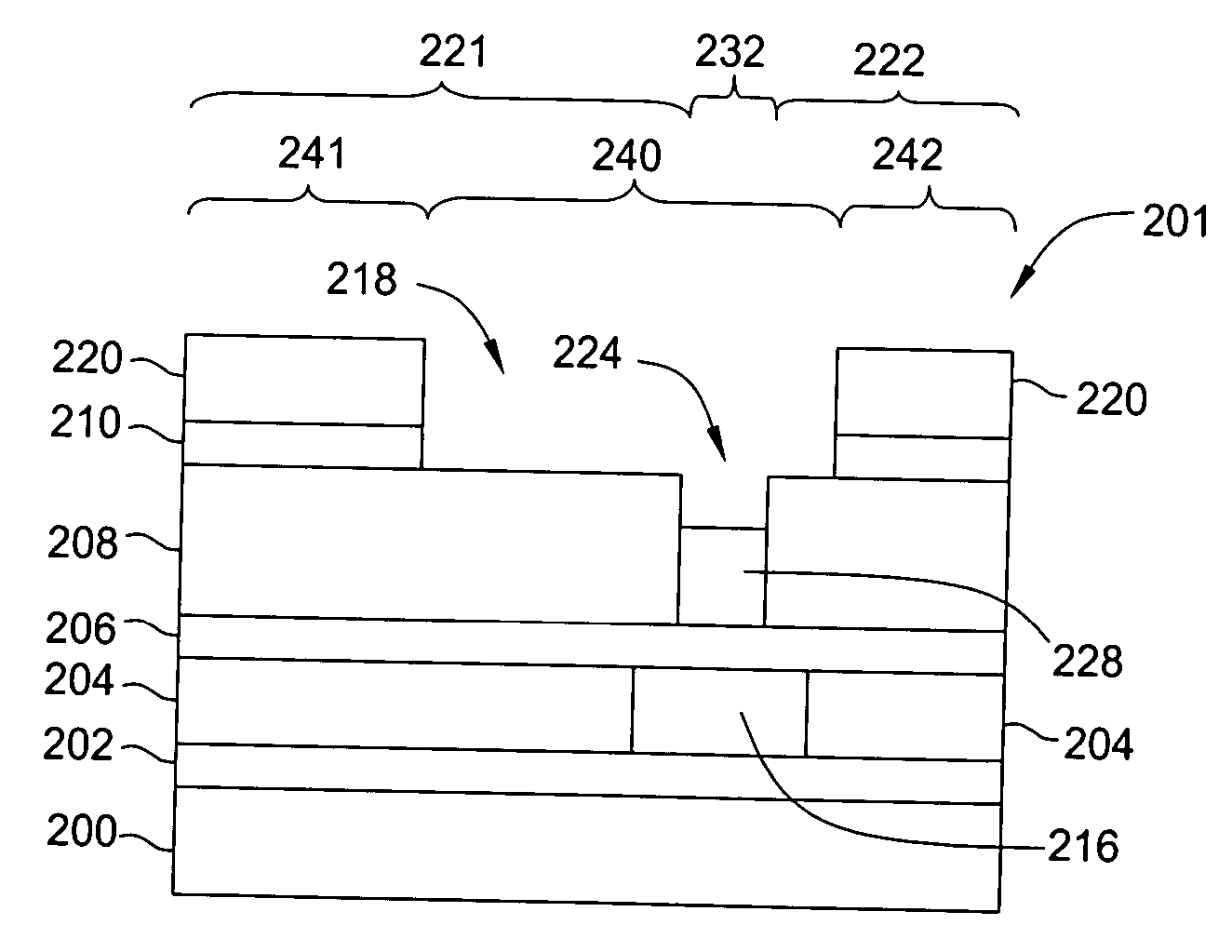

Method of fabricating a dual damascene interconnect structure

A method of fabricating a dual damascene interconnect structure uses a very high frequency high-density plasma and selectively controlled substrate bias for in-situ etching a trench above a via hole of the interconnect structure and a barrier layer between the via hole and underlying conductive layer.

Owner:APPLIED MATERIALS INC

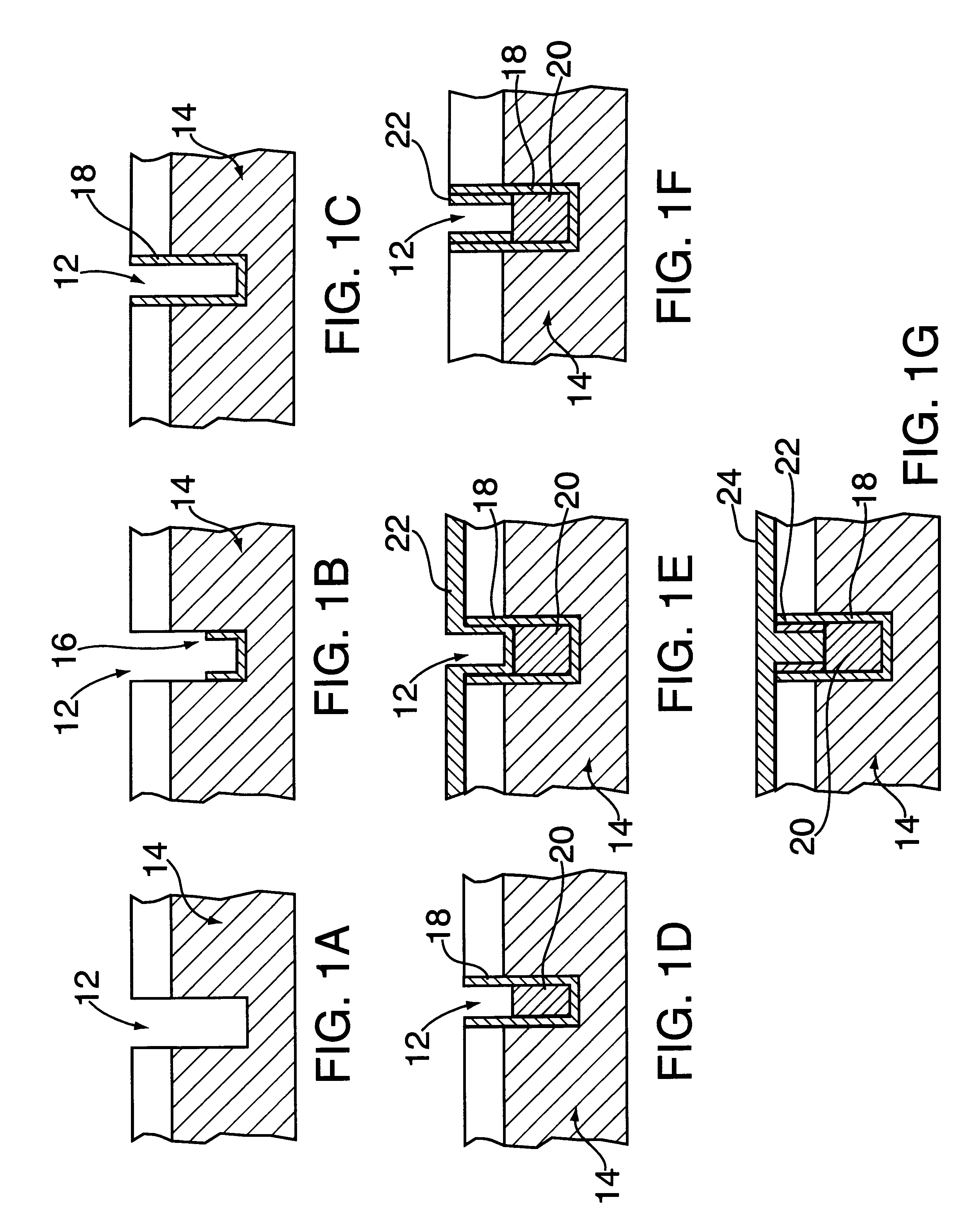

Enhancing deposition uniformity of a channel semiconductor alloy by an in situ etch process

InactiveUS20100289094A1Superior deposition conditionEfficient overall manufacturing flowTransistorSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor alloys

When forming sophisticated gate electrode structures requiring a threshold adjusting semiconductor alloy for one type of transistor, a recess is formed in the corresponding active region, thereby providing superior process uniformity during the deposition of the semiconductor material. Due to the recess, any exposed sidewall surface areas of the active region may be avoided during the selective epitaxial growth process, thereby significantly contributing to enhanced threshold stability of the resulting transistor including the high-k metal gate stack.

Owner:GLOBALFOUNDRIES INC

Method and apparatus for extending equipment uptime in ion implantation

InactiveUS20070241689A1Extended service lifeReduce downtimeVacuum evaporation coatingElectric arc lampsDopantRemote plasma

The service lifetime of an ion source is enhanced or prolonged by the source having provisions for in-situ etch cleaning of the ion source and of an extraction electrode, using reactive halogen gases, and by having features that extend the service duration between cleanings. The latter include accurate vapor flow control, accurate focusing of the ion beam optics, and thermal control of the extraction electrode that prevents formation of deposits or prevents electrode destruction. An apparatus comprised of an ion source for generating dopant ions for semiconductor wafer processing is coupled to a remote plasma source which delivers F or Cl ions to the first ion source for the purpose of cleaning deposits in the first ion source and the extraction electrode. These methods and apparatus enable long equipment uptime when running condensable feed gases such as sublimated vapor sources, and are particularly applicable for use with so-called cold ion sources. Methods and apparatus are described which enable long equipment uptime when decaborane and octadecaborane are used as feed materials, as well as when vaporized elemental arsenic and phosphorus are used, and which serve to enhance beam stability during ion implantation.

Owner:SEMEQUIP

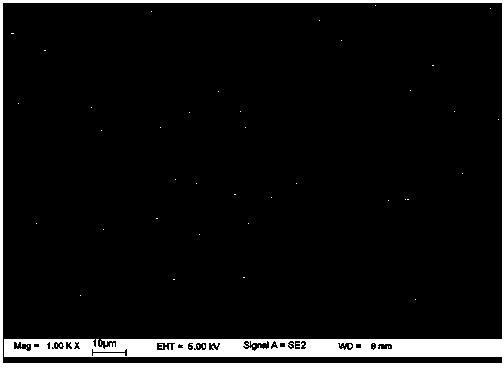

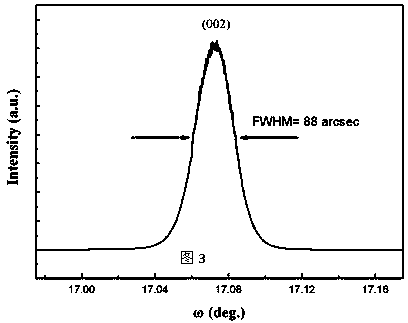

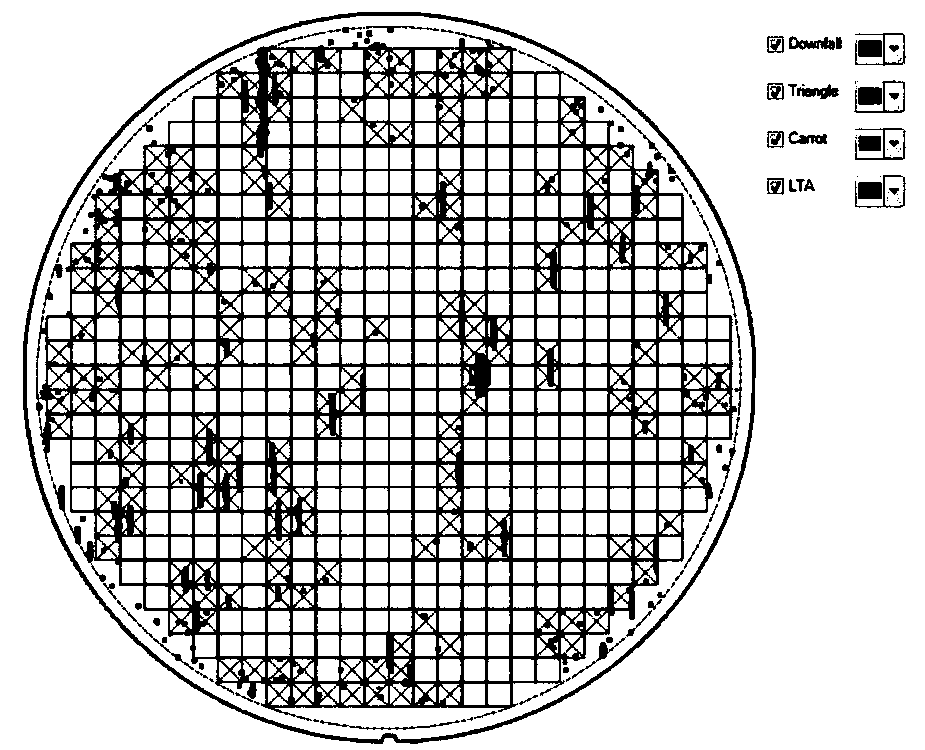

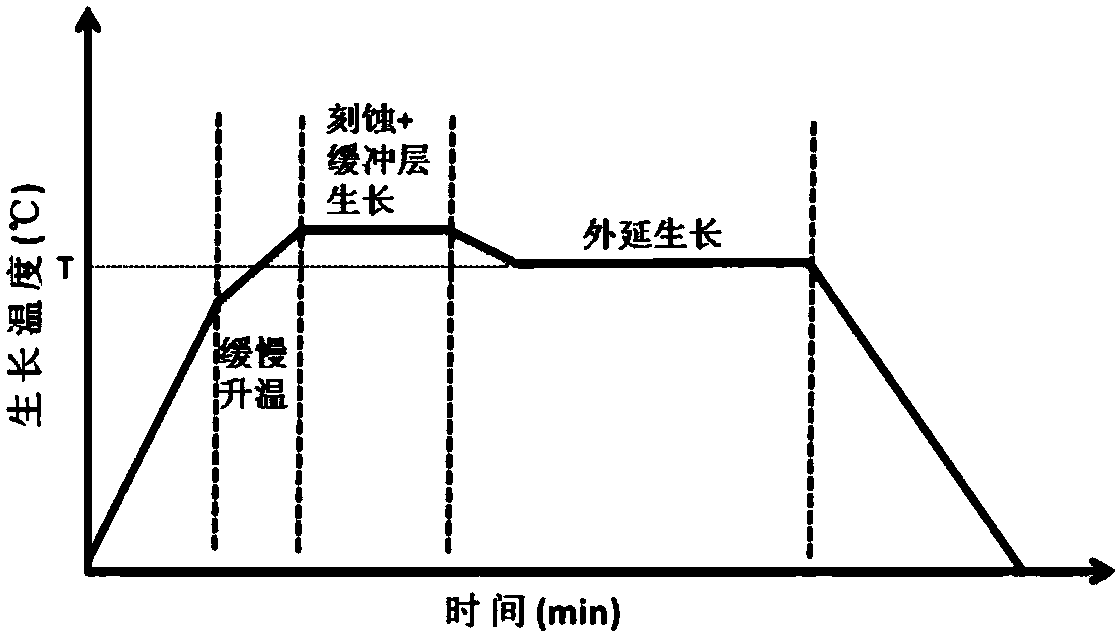

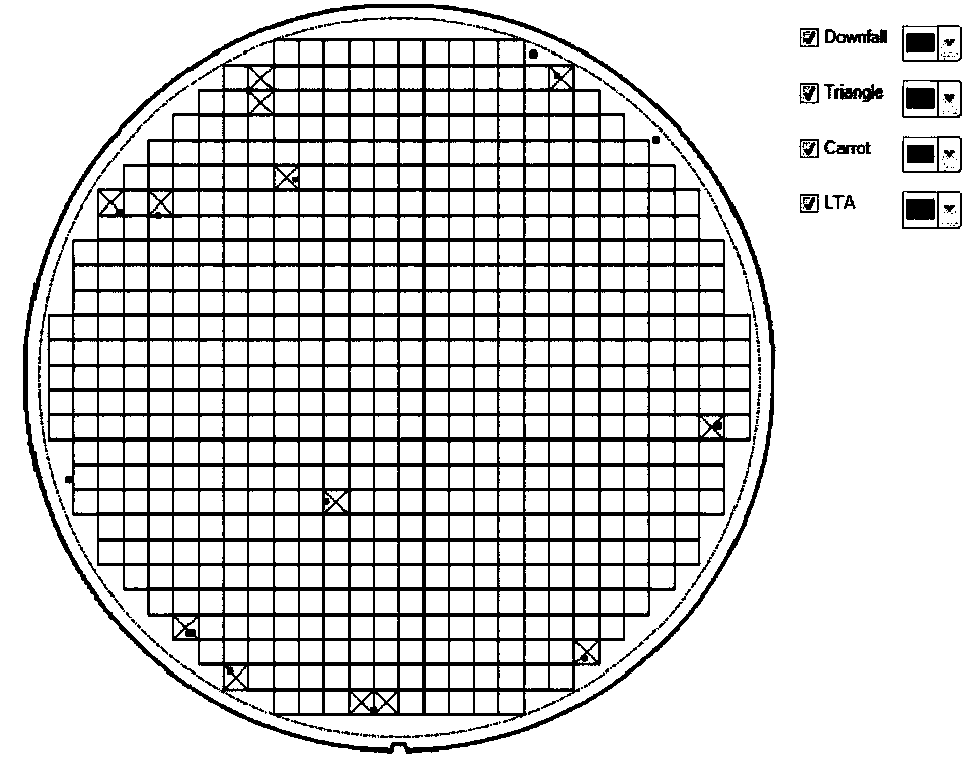

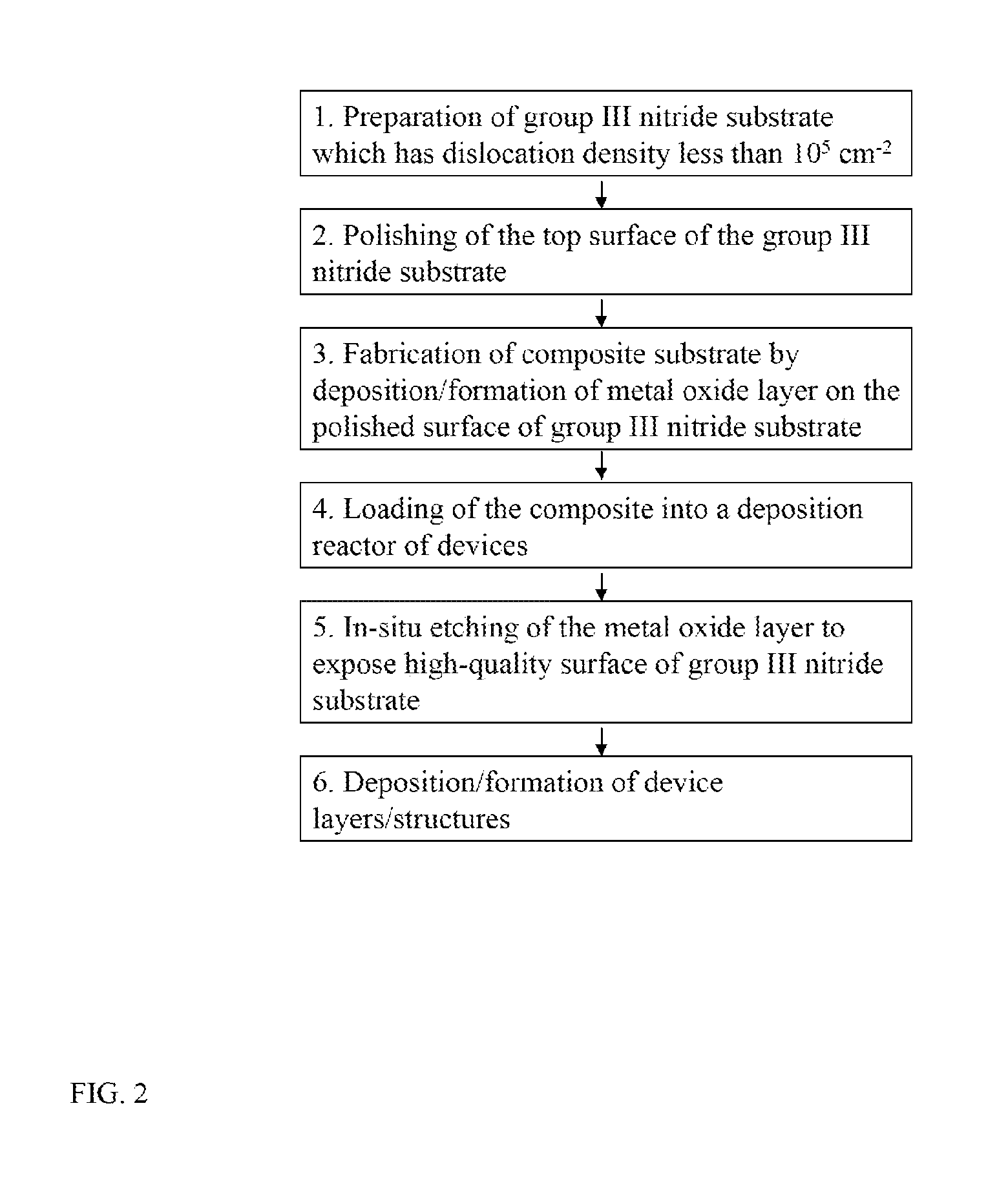

Gallium nitride homoepitaxy method based on in situ etching

ActiveCN103614769AQuality improvementEfficient removalSemiconductor/solid-state device manufacturingFrom chemically reactive gasesMicro structureEffective solution

The invention discloses a gallium nitride homoepitaxy method based on in situ etching. The method comprises the following steps: 1) selecting a gallium nitride substrate and transferring the substrate into an MOCVD system; 2) conducting fast etching on the substrate for a short time; 3) conducting long-time slow etching after the fast etching to form hexagonal pyramid micro structures on the substrate surface; 4) laterally growing to merge the hexagonal pyramid micro structures; and 5) continuing to grow a high-quality GaN epitaxial layer on the merged film. The invention has the following advantages: through the control of components of in situ etching gas, impurities on the surface of the substrate are removed, while the hexagonal pyramid micro structures are formed on the surface of the substrate; and the micro structures are merged in a lateral epitaxial stage, so as to reduce the dislocation density of the epitaxial layer and finally obtain the gallium nitride epitaxial thin film with high quality. Formation of hexagonal pyramid micro structures on the surface of the substrate does not need additional process equipment; the method is economical, simple and practicable; and the epitaxial material has good performance. Therefore, the method provided by the invention is an effective solution for realizing high-quality and low-cost growth of GaN epitaxial thin film.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

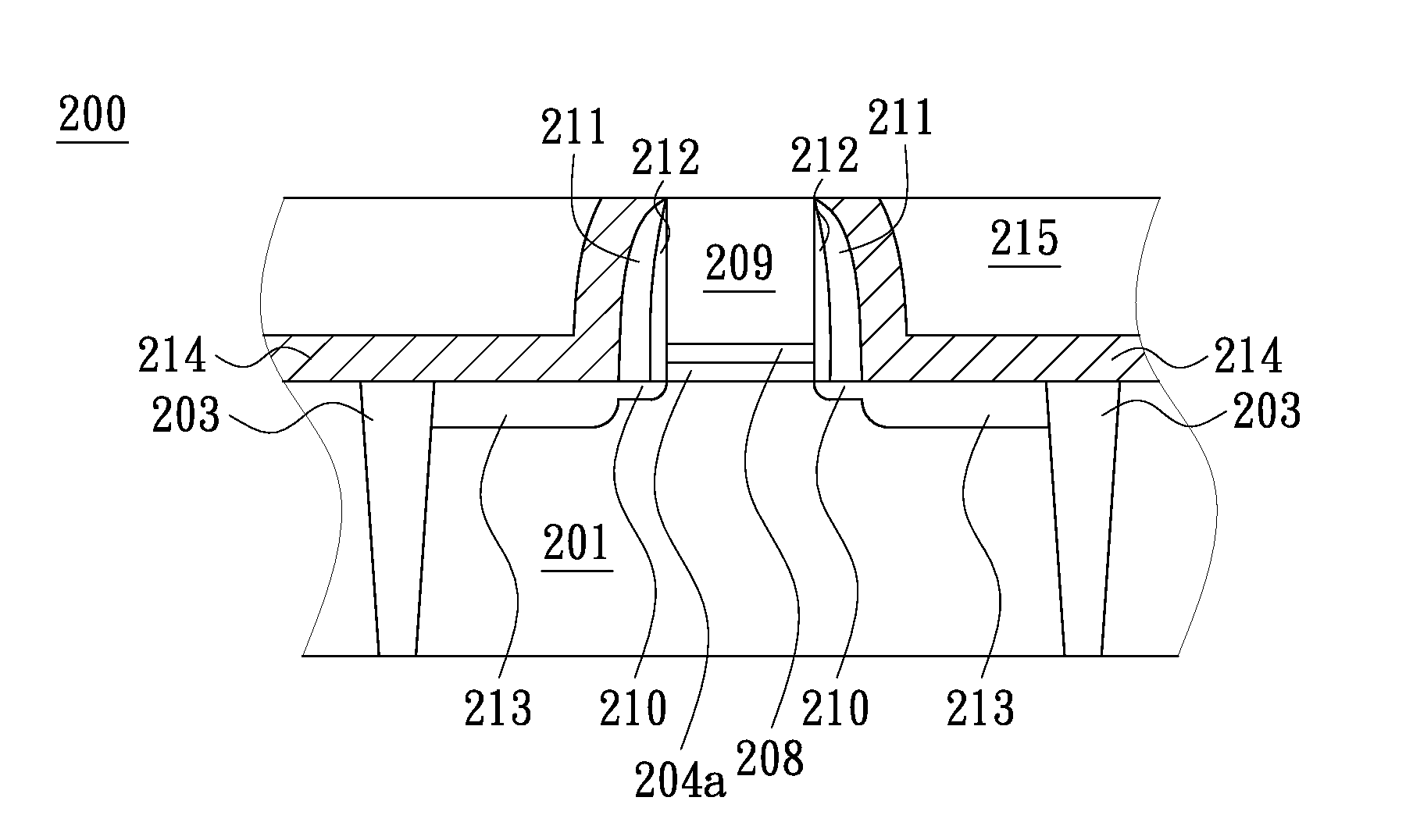

Method for fabricating semiconductor device

InactiveUS20120264279A1Low etch selectivityResidue reductionTransistorSemiconductor/solid-state device manufacturingInter layerSemiconductor structure

A method for fabricating a semiconductor device, wherein the method comprises steps as follows: a semiconductor structure comprising a substrate, a dummy gate structure having a dielectric layer disposed over the substrate and a silicon layer disposed over the dielectric layer, and an etching stop layer (ESL) and an inter-layer dielectric (ILD) layer both of which are sequentially disposed over the substrate and the dummy gate structure is first provided. Then, a chemical mechanical polishing (CMP) is performed to planrizing the ILD layer and expose the ESL. Subsequently, an in-situ etching process is conducted to remove portions of the ESL and the silicon layer to form an opening in the dummy gate structure. Next, metal material is filled into the opening.

Owner:UNITED MICROELECTRONICS CORP

Method for manufacturing gratings in semiconductor materials that readily oxidise

InactiveUS20050208768A1Easy to oxidizeOptical wave guidanceLaser detailsSemiconductor materialsSemiconductor structure

The present invention is a combination of in-situ etching with a grating mask pattern comprised only of semiconductor material, together with the fabrication of a protective layer beneath the semiconductor grating mask that protects the semiconductor material that readily oxidises. As such the present invention is based on a two-stage process. First the grating pattern is defined in a semiconductor material, wherein this pattern is called the semiconductor grating mask. The semiconductor grating mask sits on top of a layer of protective material, which in turn is on top of the semiconductor material that readily oxidises, wherein the protective layer prevents oxidation of the material below. The semiconductor structure is then moved to a reactor, where, in the second stage, the mask pattern is transferred into the underlying protective layer and the semiconductor material that readily oxidises, by in-situ etching. The grating is then overgrown in the same reactor without exposing the etched grating to the atmosphere. The overgrown material protects the underlying semiconductor material from oxidation when the structure is removed from the reactor.

Owner:FINLAY RICHARD +3

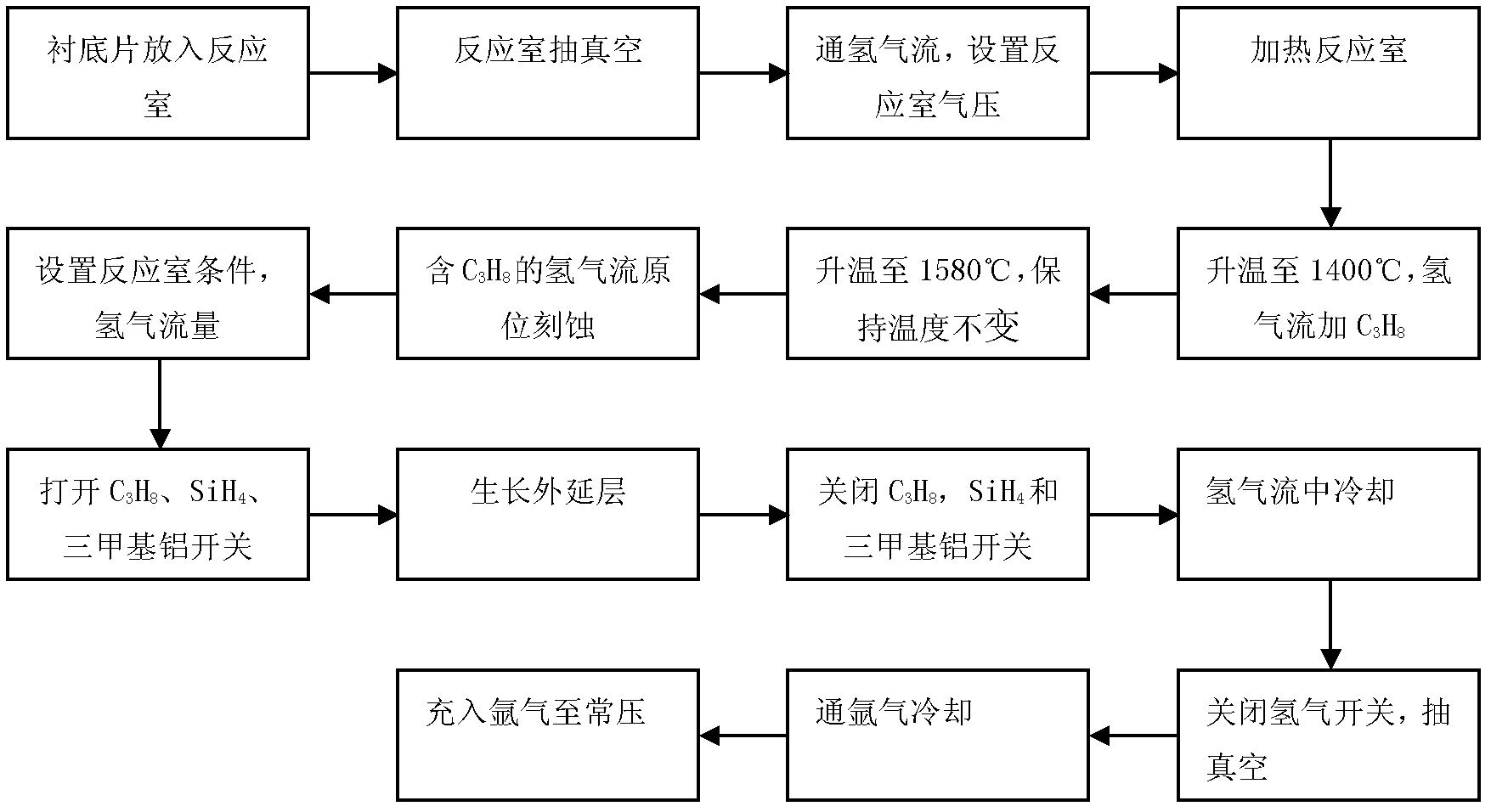

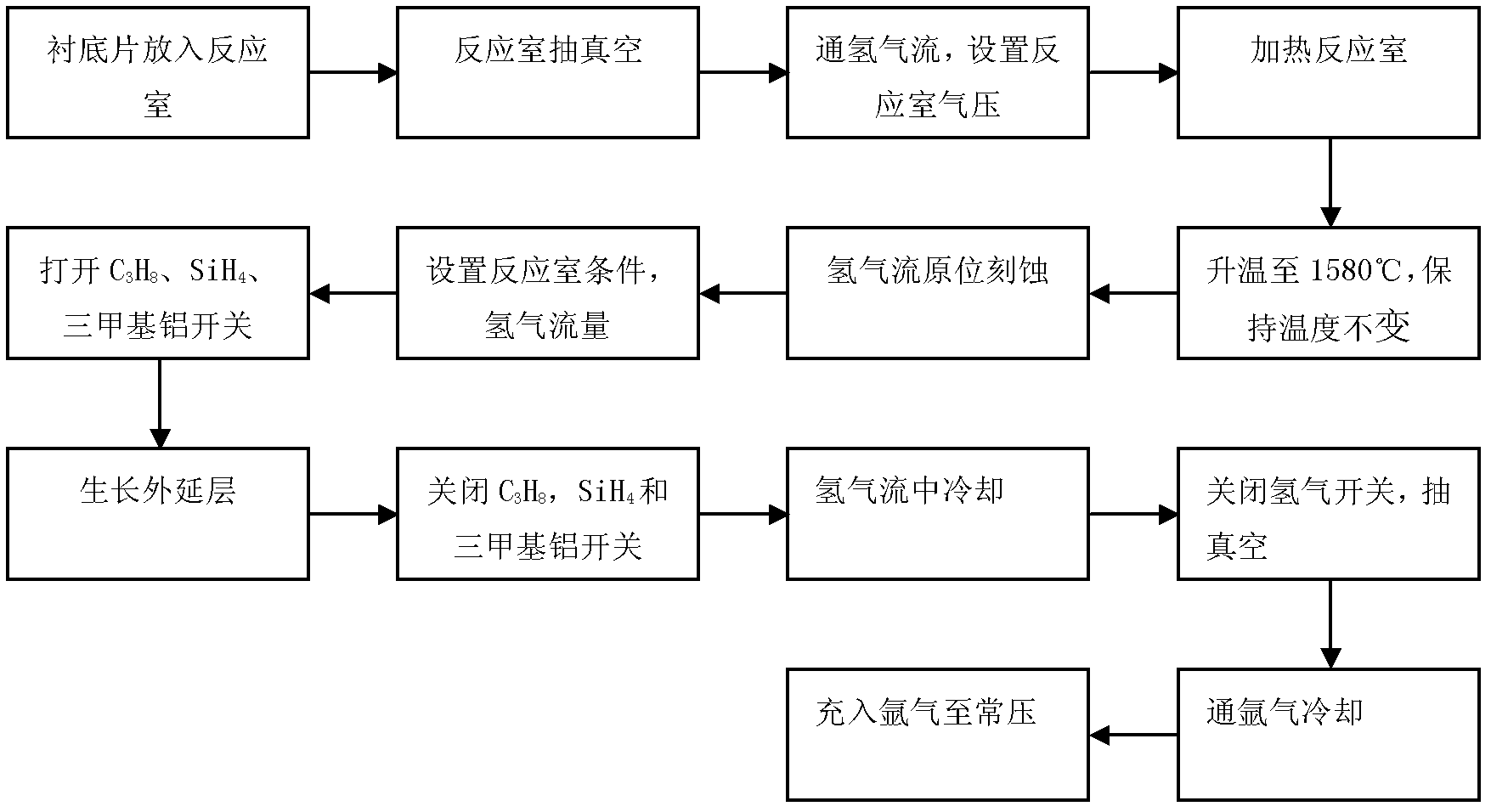

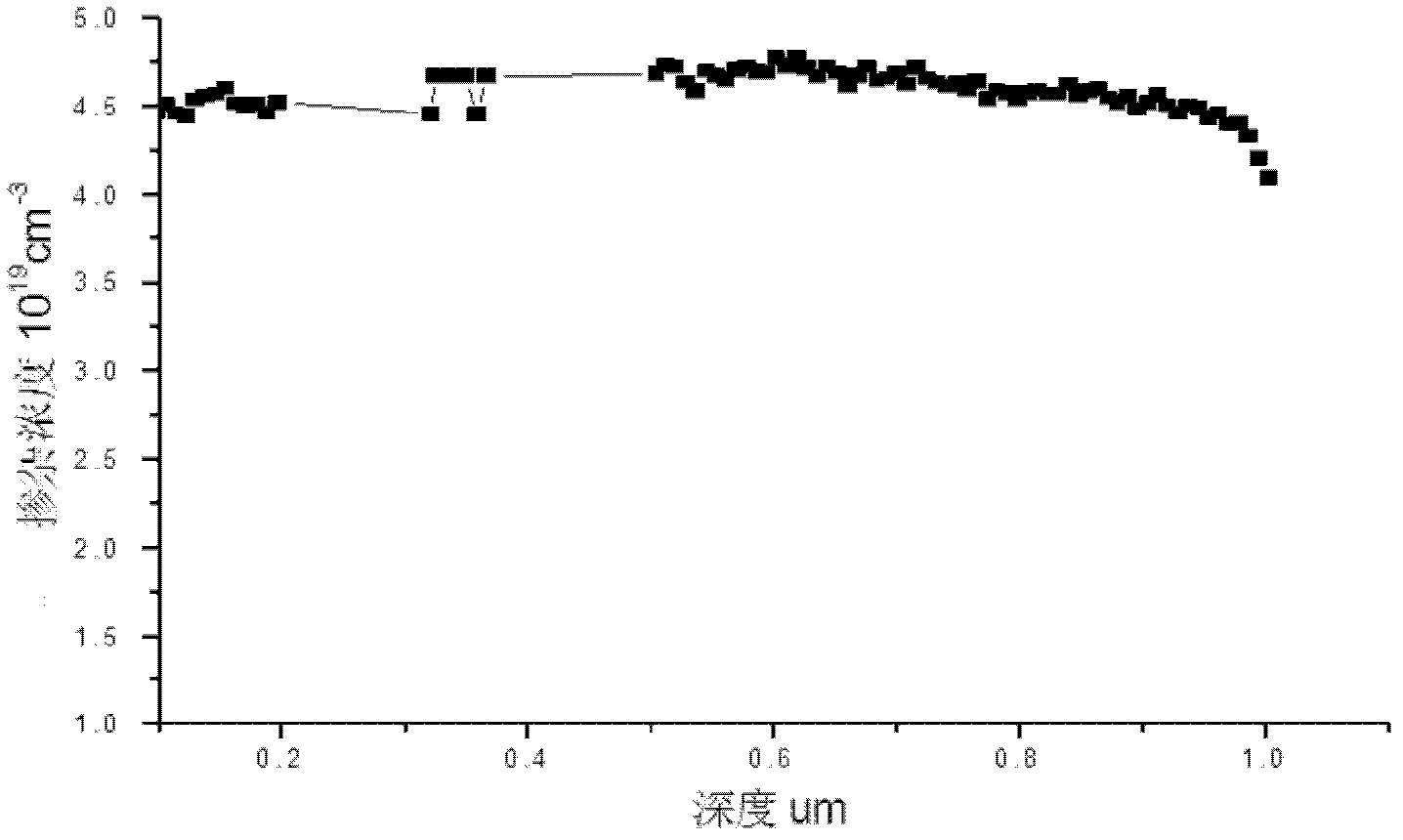

P-type heavily-doped silicon carbide film extension preparation method

ActiveCN102592976ASimple manufacturing processLattice integritySemiconductor/solid-state device manufacturingHydrogenSilanes

The invention discloses a P-type heavily-doped silicon carbide film extension preparation method, which mainly solves the problem that in the prior art, high-quality heavy doping of silicon carbide cannot be realized. The method comprises the following steps that: a silicon carbide underlay is firstly placed into a reaction chamber; the reaction chamber is heated in the hydrogen stream, and after the temperature reaches 1,400 DEG C, propane (C3H8) is added into the hydrogen stream; after the temperature reaches 1,580 DEG C, in-situ etching is performed on the underlay for 10 to 30 minutes; then the temperature of the reaction chamber is maintained at 1,580 DEG C, the air pressure is maintained at 100mbar, silane (SiH4) with a flow rate of 15 to 24 mL / min, C3H8 with a flow rate of 5 to 10 mL / min and trimethyl aluminium with a flow rate of 3.2*10<minus 5 mol / min) are added into the hydrogen stream of 20L / min to grow an extension layer; after the growth is completed, the extension layer is cooled in the hydrogen stream; and finally, argon is charged into the reaction chamber to the normal pressure. The doping concentration of the prepared silicon carbide extension layer is 4*1019cm<-3> to 4.6*1019cm<-3>, the doping is uniform, the surface is smooth, and the prepared silicon carbide extension layer can be used for producing a silicon carbide device.

Owner:陕西半导体先导技术中心有限公司

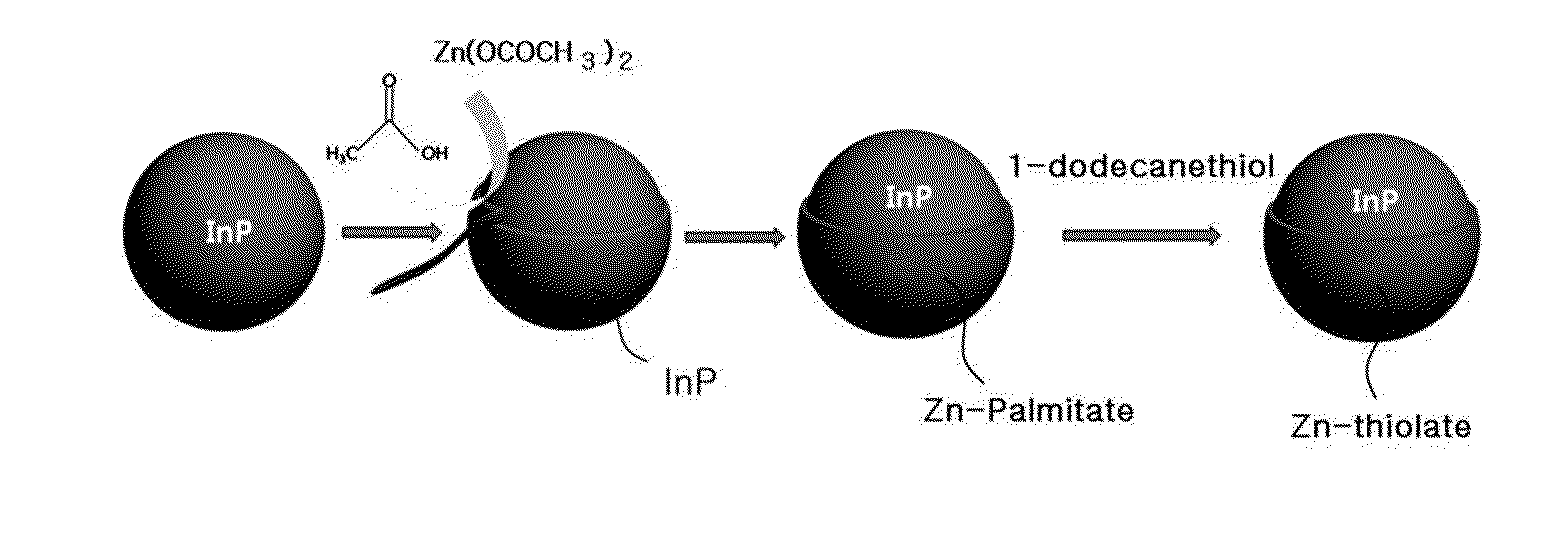

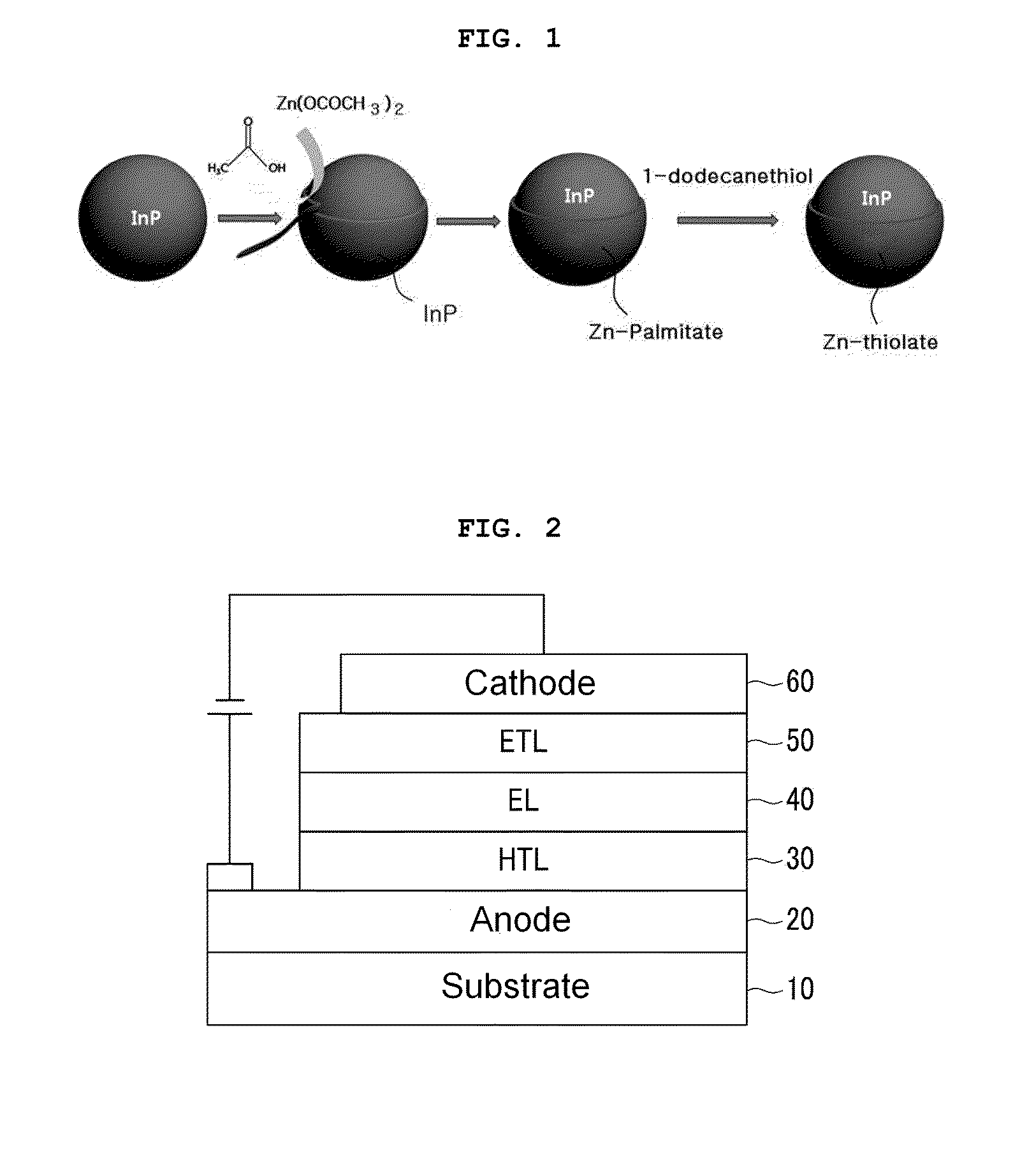

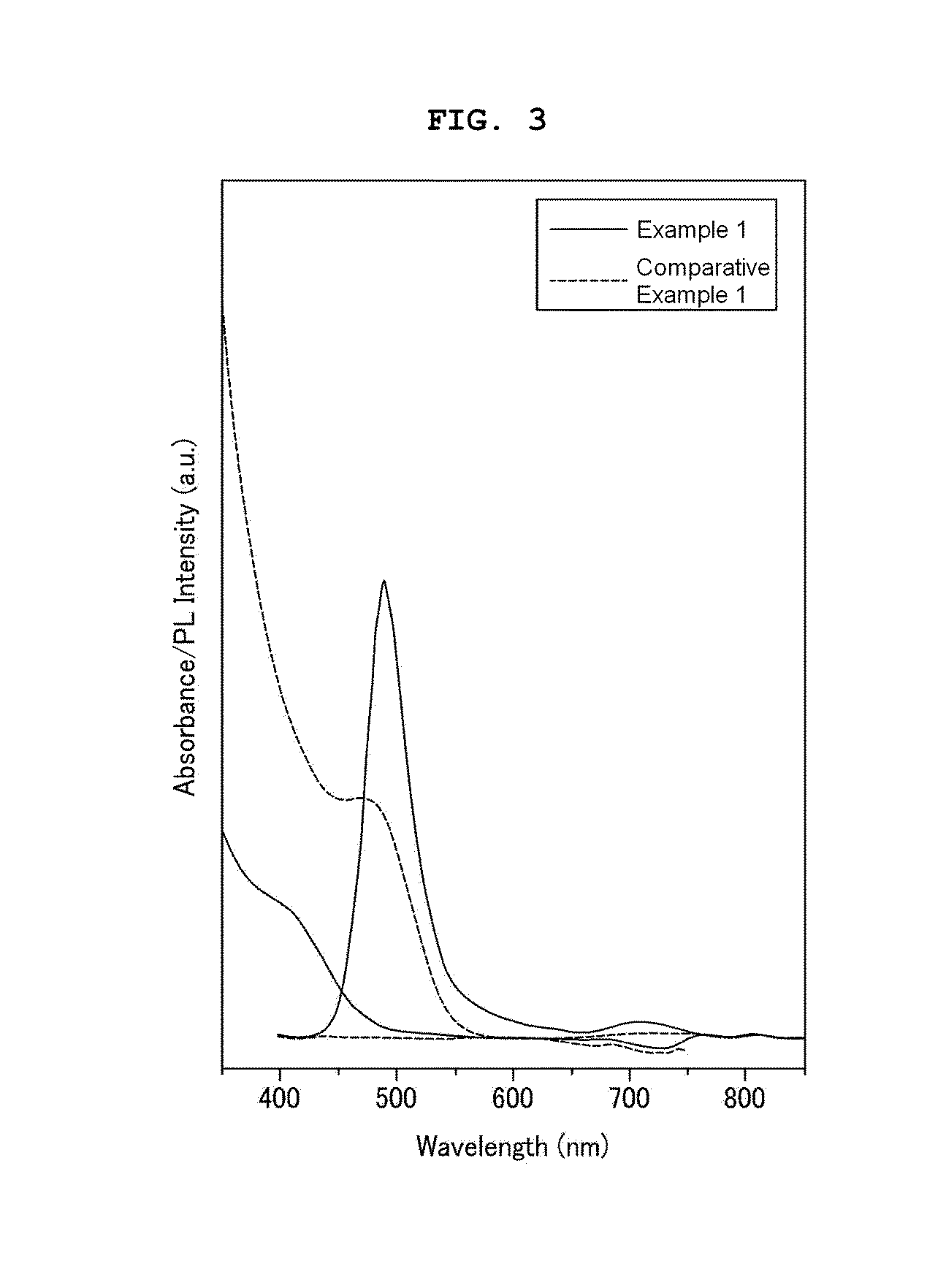

Preparation method of nanocrystals coated with metal-surfactant layers

A method for preparing nanocrystals is disclosed. The method includes synthesizing colloidal semiconductor nanocrystal cores, and adding a metal salt to the colloidal semiconductor nanocrystal cores and heating the mixture while maintaining the reaction temperature constant. During the reaction, the surfaces of the semiconductor nanocrystal cores are etched (‘in-situ etching’) and metal-surfactant layers are formed on the etched surface portions of the semiconductor nanocrystal cores. The metal-surfactant layers are derived from the metal salt. Nanocrystals prepared by the method have minimal surface defects and exhibit high luminescence efficiency and good stability.

Owner:SAMSUNG ELECTRONICS CO LTD

Growth method capable of effectively reducing silicon carbide epitaxial surface defects

InactiveCN108166056AReduce epitaxial surface defectsReduce surface defectsPolycrystalline material growthFrom chemically reactive gasesGas phaseChemical vapor deposition

The invention mainly solves the technical problem, and provides a growth method capable of effectively reducing silicon carbide epitaxial surface defects. A buffer layer grows under the condition thata temperature is higher than an epitaxial growth temperature by adopting a low temperature and high temperature combined on-line in-situ substrate etching process. Based on a conventional chemical vapor deposition epitaxial furnace at the present, extension and evolution growth of defects on a silicon carbide substrate are reduced by improving the on-line in-situ etching process and a buffer layer growth process, so that surface defects of an epitaxial layer are effectively reduced, and a high-quality silicon carbide homoepitaxial wafer is obtained. As compatible with a conventional silicon carbide epitaxy process, the process disclosed by the invention is applicable to the conventional commercial single-wafer and multi-wafer type epitaxial furnaces, and is relatively high in popularization value.

Owner:李哲洋

Dislocation-specific dielectric mask deposition and lateral epitaxial overgrowth to reduce dislocation density of nitride films

InactiveUS7459380B2Inhibit threading of the lattice mismatchSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEtching

In accordance with the present invention, improved methods for reducing the dislocation density of nitride epitaxial films are provided. Specifically, an in-situ etch treatment is provided to preferentially etch the dislocations of the nitride epitaxial layer to prevent threading of the dislocations through the nitride epitaxial layer. Subsequent to etching of the dislocations, an epitaxial layer overgrowth is performed. In certain embodiments, the etching of the dislocations occurs simultaneously with growth of the epitaxial layer. In other embodiments, a dielectric mask is deposited within the etch pits formed at the dislocations prior to the epitaxial layer overgrowth.

Owner:APPLIED MATERIALS INC

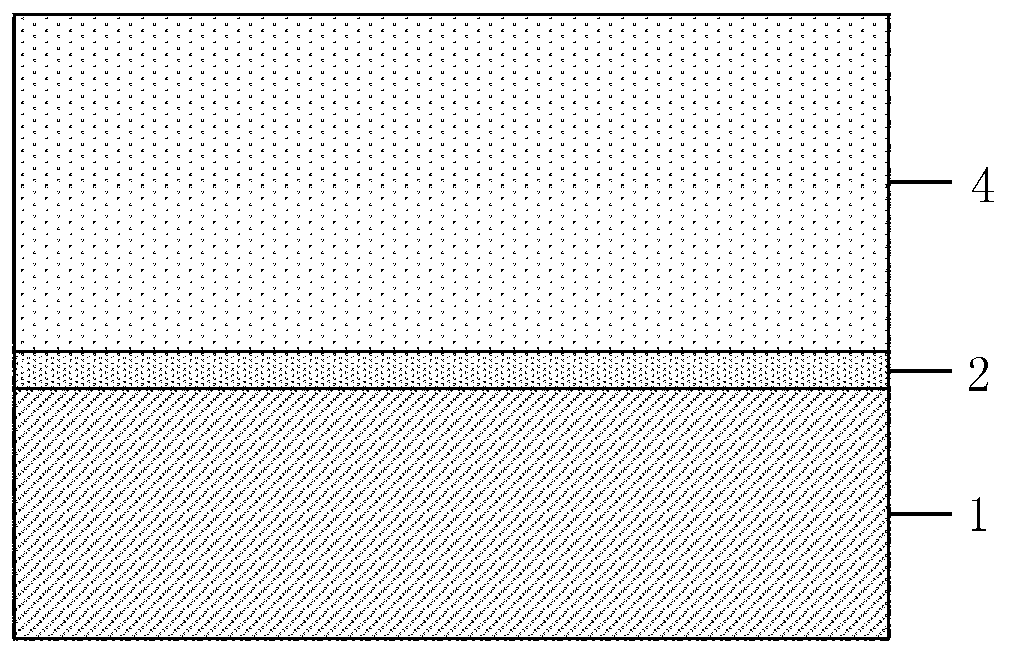

Composite substrate of gallium nitride and metal oxide

ActiveUS20140054595A1Solve the real problemSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingReactive gasGas phase

The present invention discloses a novel composite substrate which solves the problem associated with the quality of substrate surface. The composite substrate has at least two layers comprising the first layer composed of GaxAlyIn1-x-yN (0≦x≦1, 0≦x+y≦1) and the second layer composed of metal oxide wherein the second layer can be removed with in-situ etching at elevated temperature. The metal oxide layer is designed to act as a protective layer of the first layer until the fabrication of devices. The metal oxide layer is designed so that it can be removed in a fabrication reactor of the devices through gas-phase etching by reactive gas such as ammonia.

Owner:SEOUL SEMICONDUCTOR

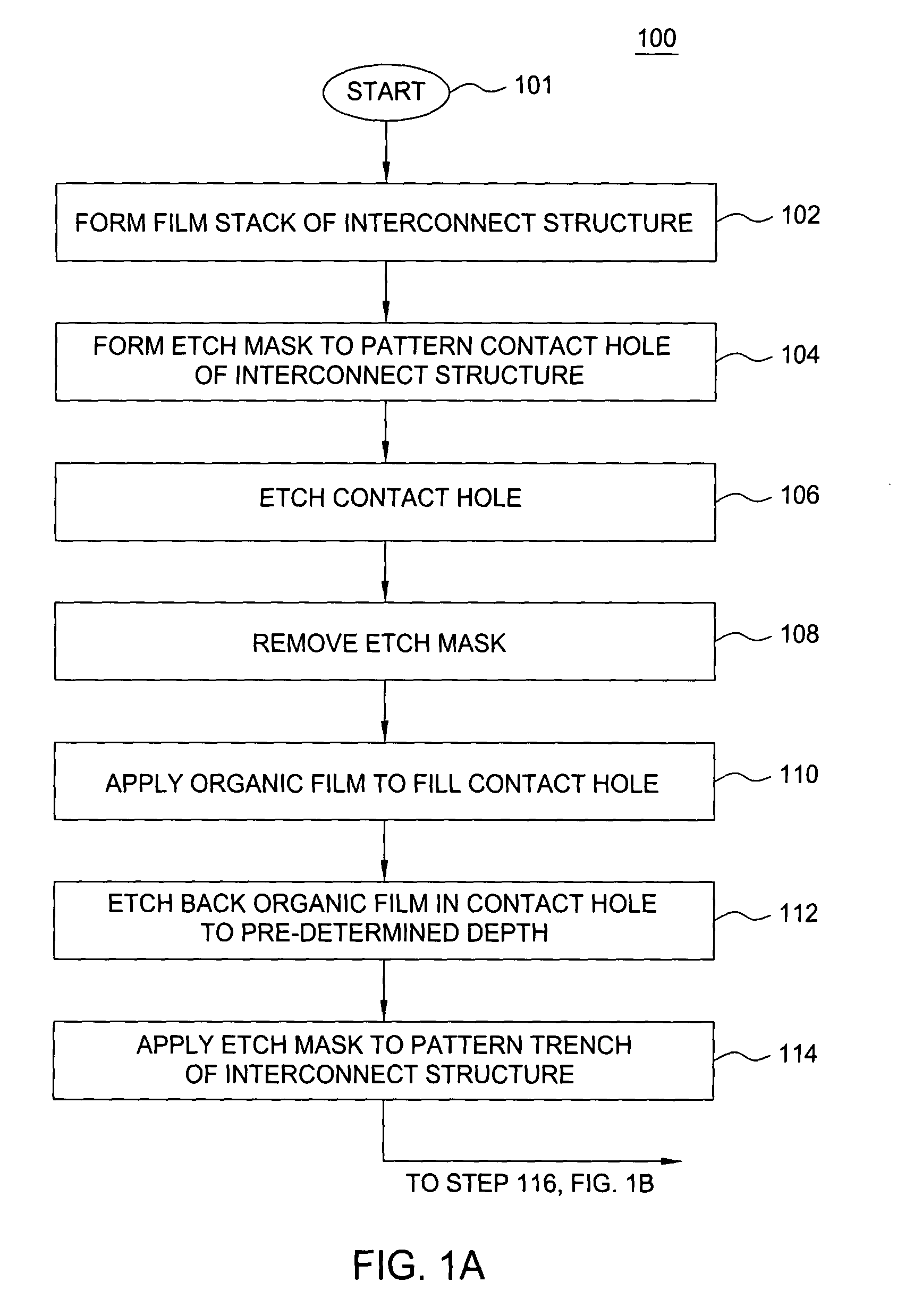

In-situ etch-stop etch and ashing in association with damascene processing in forming semiconductor interconnect structures

InactiveUS20050245074A1Facilitate via critical dimension (CD) controlHigh selectivitySemiconductor/solid-state device manufacturingDielectricInter layer

One or more aspects of the subject disclosure pertain to forming single or dual damascene interconnect structures in the fabrication of semiconductor devices. The interconnect structures are formed in manners that mitigate one or more adverse effects associated with conventional techniques. One or more aspects of the invention may be employed, for example, to facilitate better via critical dimension (CD) control, improve selectivity of etch-stop layer to inter layer dielectric (ILD) and / or intra-metal dielectric (IMD) material, and / or to simplify and make the fabrication process more efficient and / or cost effective.

Owner:TEXAS INSTR INC

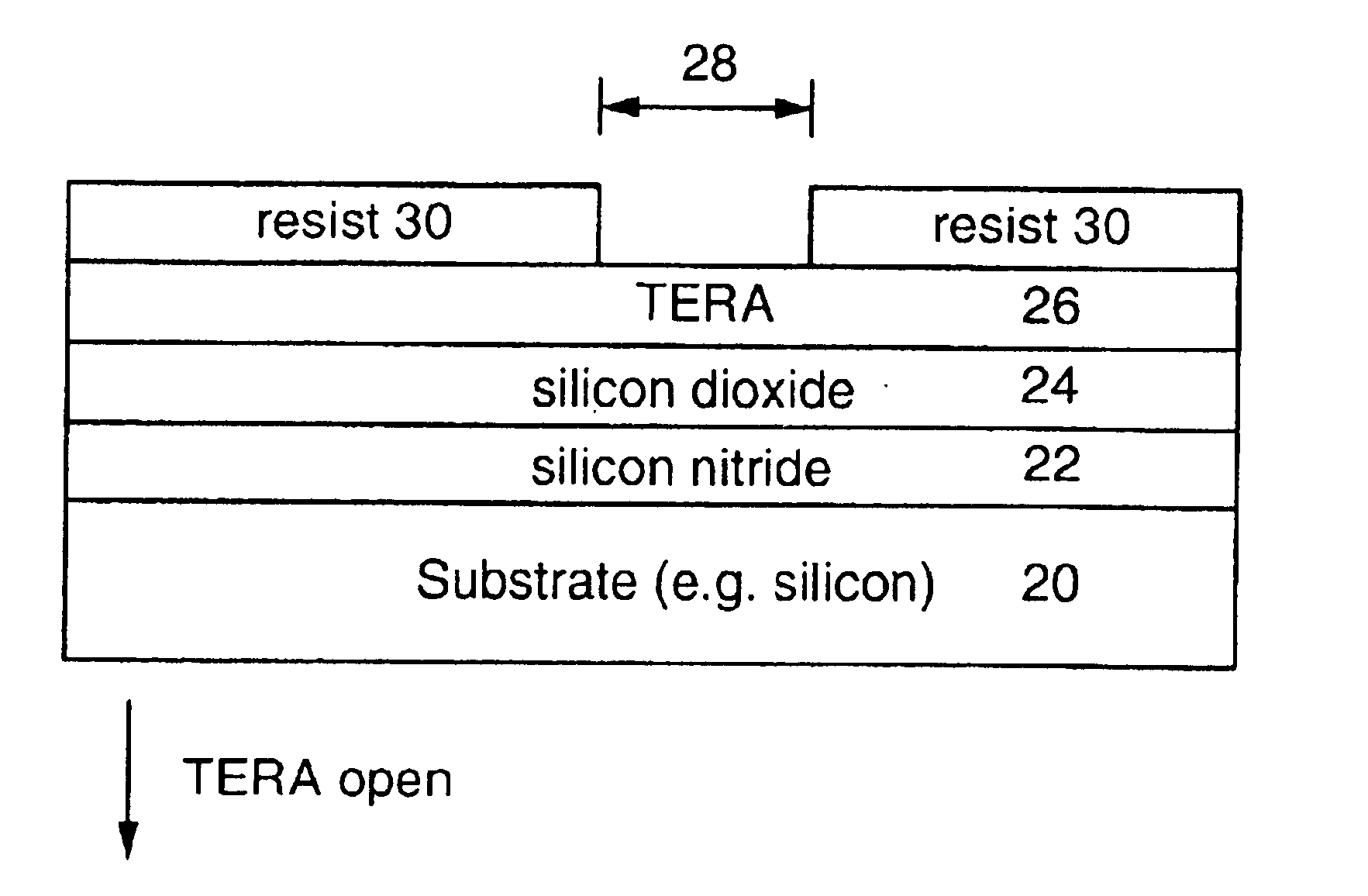

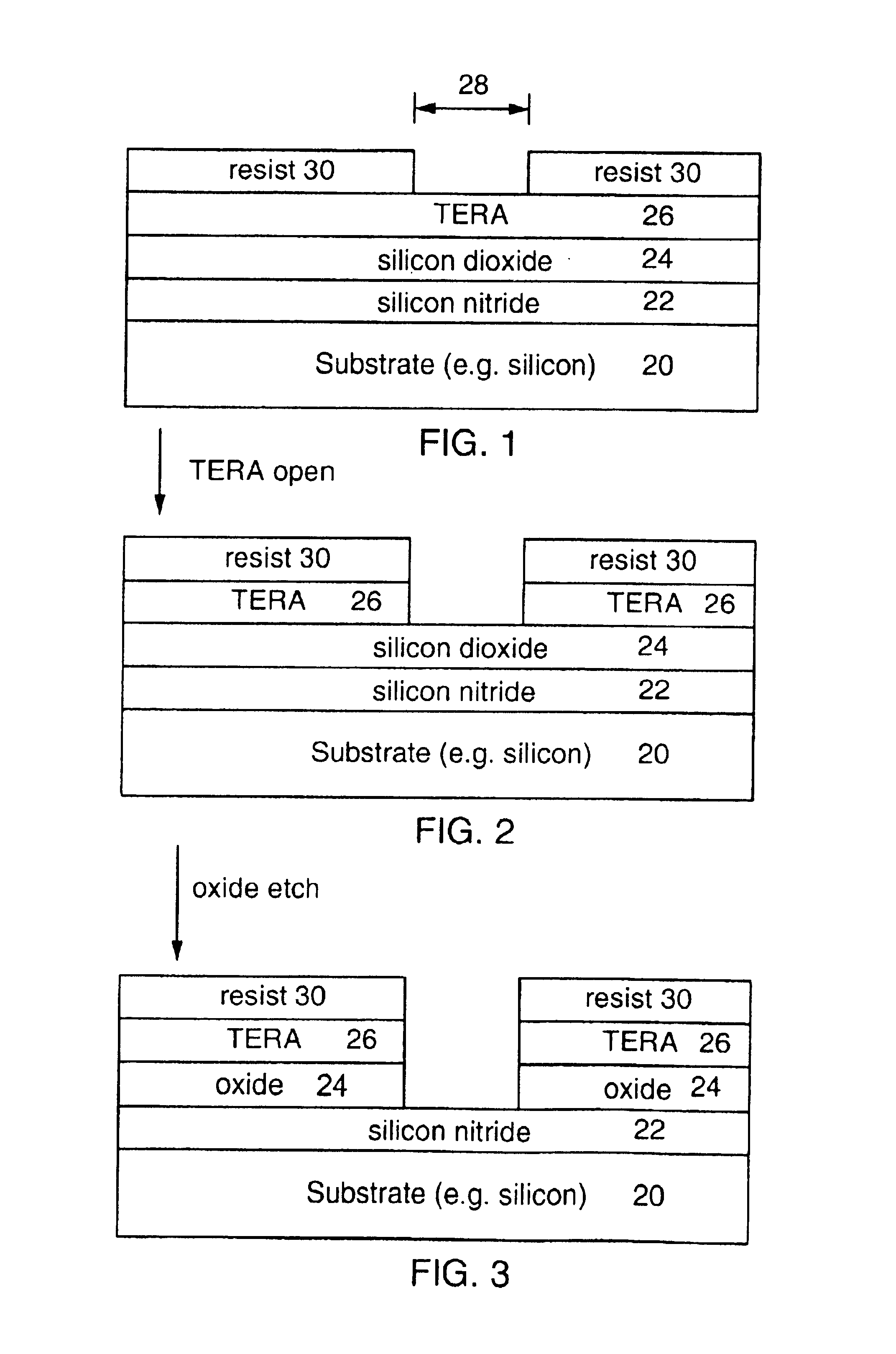

In-situ plasma etch for TERA hard mask materials

InactiveUS6903023B2Semiconductor/solid-state device manufacturingPhotosensitive materials for photomechanical apparatusNitrogenOxygen

A method for removing carbon from or stripping a TERA layer. The method includes exposing the TERA layer to a plasma containing an effective amount of nitrogen, and, optionally, oxygen or fluorine. The method is compatible with fluorine based etching systems, and may thus be performed in the same etching system as other etching steps. For example, the method may be performed in the same system as a fluorine based plasma etch for oxide or nitride. The invention includes the method of stripping a TERA layer, etching an oxide layer, and etching a nitride layer in situ in the same etching system. The method is performed at low ion energies to avoid damaging oxide or nitride layers under the TERA film and to provide good selectivity.

Owner:IBM CORP