Semiconductor device structure and manufacturing method thereof

A technology of device structure and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as discharge phenomenon excitation, test failure, etc., to avoid lattice defects and device damage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] Figures 6 to 9 It is a schematic diagram of a first embodiment of forming an interconnection structure using the present invention. like Image 6 As shown, a semiconductor substrate 100 is provided, and the semiconductor substrate 100 may be a logic structure with multiple layers of metal lines, or may be a metal line layer on the surface of a logic structure; wherein the semiconductor substrate 100 is divided into device regions II and dummy region I at the edge of the semiconductor substrate. A first insulating layer 102 with a thickness of less than 10,000 angstroms is formed on the surface of the semiconductor substrate 100 by chemical vapor deposition, and the first insulating layer 102 acts as an electrical isolation to ensure that the current of the formed semiconductor product only flows through the interconnection lines .

[0028] In this embodiment, the material of the first insulating layer 102 may be silicon oxide.

[0029] continue to refer to Image ...

Embodiment 2

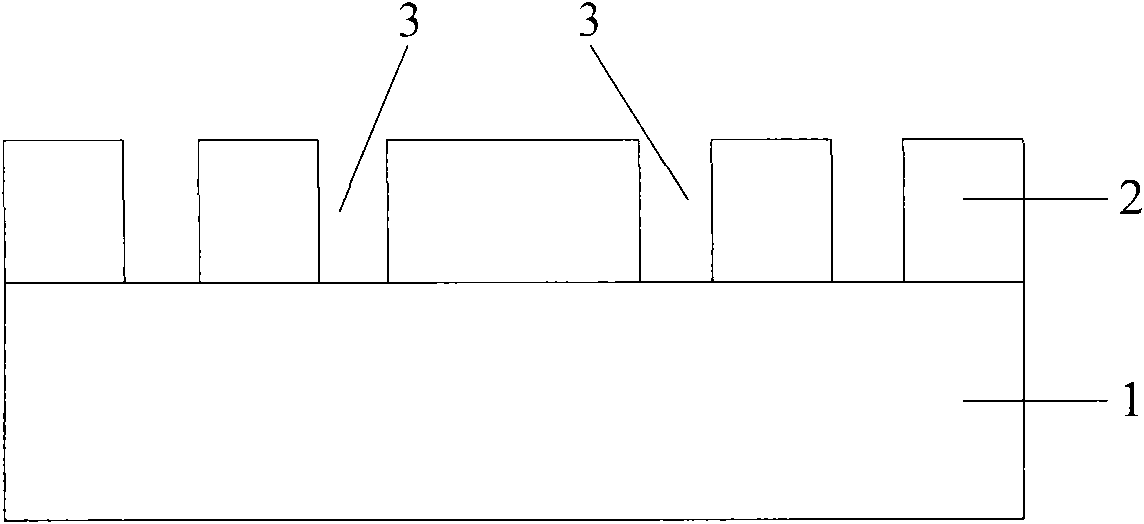

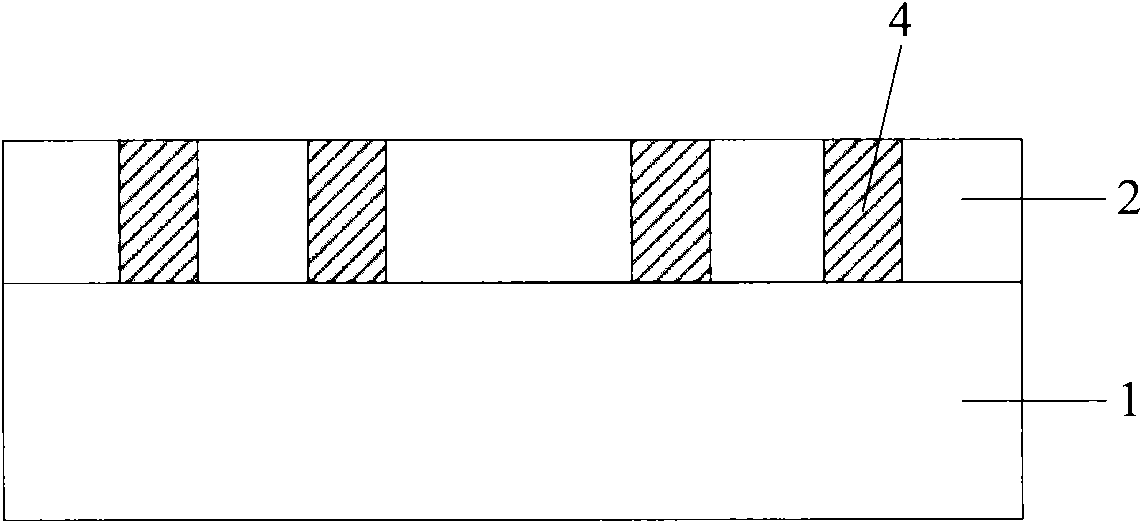

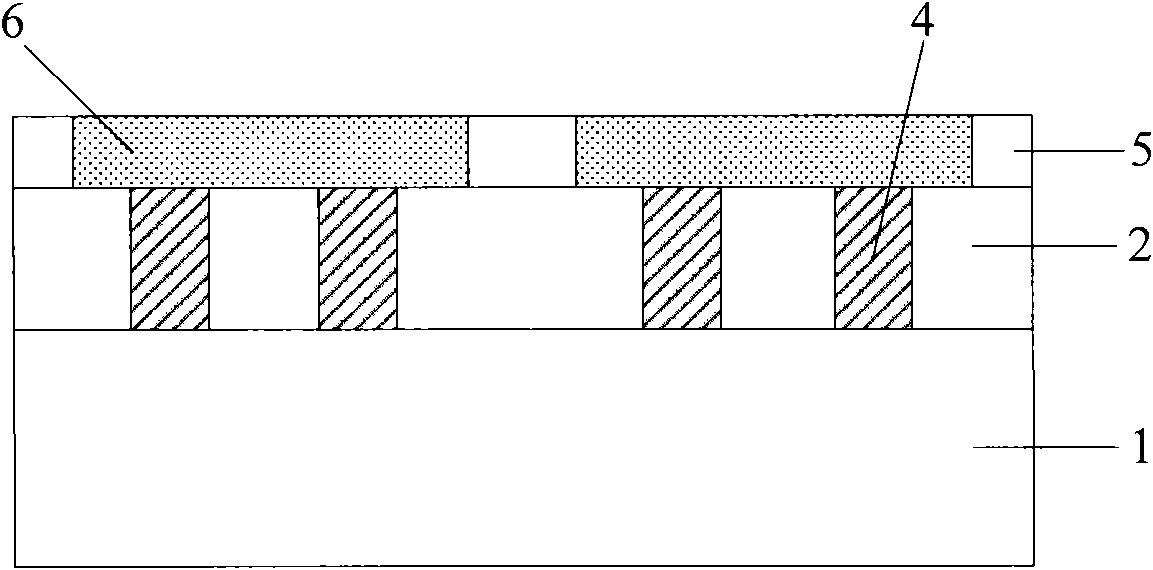

[0044] Figures 10 to 13 It is a schematic diagram of a second embodiment of forming an interconnection structure using the present invention. like Figure 10 As shown, a semiconductor substrate 200 is provided, and the semiconductor substrate 200 may be a logic structure with multiple layers of metal lines, or may be a metal line layer on the surface of a certain layer of logic structure; wherein the semiconductor substrate 200 is divided into device regions II and dummy region I at the edge of the semiconductor substrate. A first insulating layer 202 with a thickness of less than 10,000 angstroms is formed on the surface of the semiconductor substrate 200 by chemical vapor deposition, and the first insulating layer 202 acts as an electrical isolation to ensure that the current of the formed semiconductor product only flows through the interconnection lines .

[0045] In this embodiment, the material of the first insulating layer 202 may be silicon oxide.

[0046] continu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More