DDR SDRAM physical layer interface circuit and DDR SDRAM control device

A physical layer interface, physical layer technology, applied in the direction of electrical digital data processing, data processing input/output process, static memory, etc., can solve the problems of long delay of the clock tree and difficult timing convergence.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The invention discloses a double data rate synchronous dynamic random access memory (DDR SDRAM) physical layer interface circuit and a DDR SDRAM control device. Compared with the invention of the applicant's patent (US 9,570,130B2), the DDR SDRAM physical layer interface circuit and the DDR SDRAM control device of the present invention have the advantages of smaller circuit area and / or less power consumption. It should be noted that those skilled in the art can refer to this US patent (US 9,570,130B2) to understand the background knowledge of the present invention.

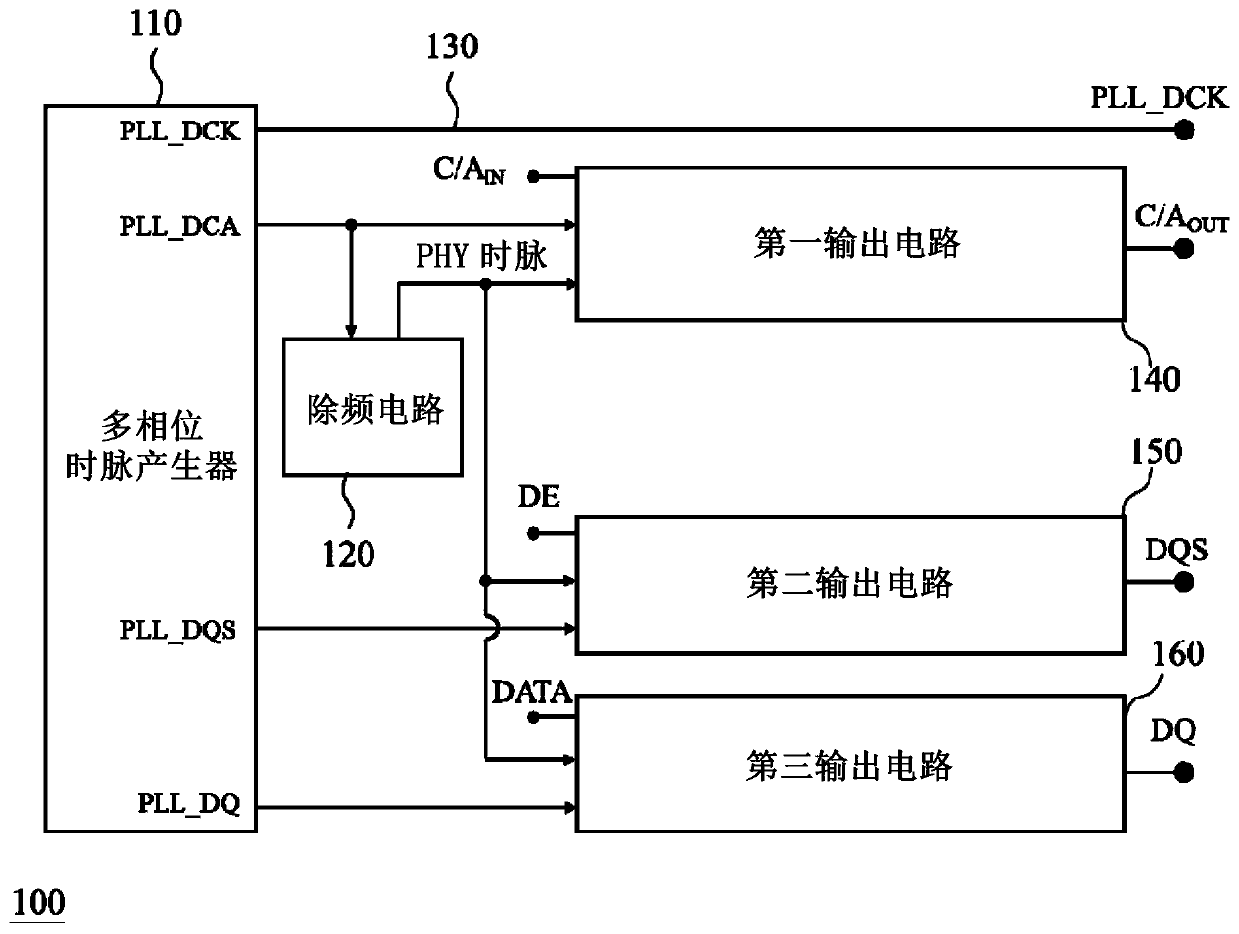

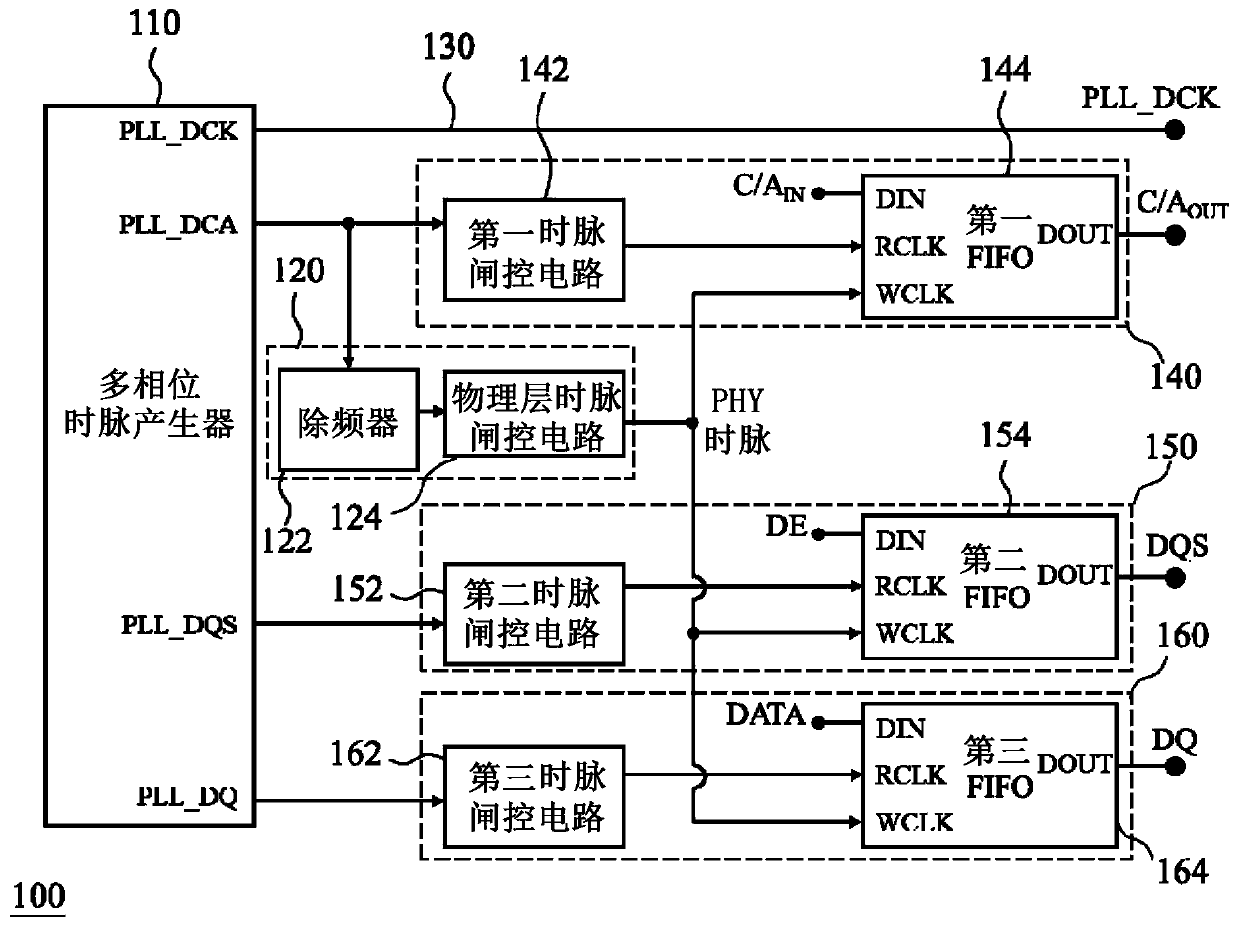

[0020] figure 1 An embodiment of the DDR SDRAM physical layer interface circuit of the present invention is shown, which can be used to adjust the phase of a signal between a memory controller and a storage circuit without using a delay locked loop that consumes a large amount of circuit area. figure 1 The DDR SDRAM physical layer interface circuit 100 comprises a multi-phase clock generator 110, a frequen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More