Electrostatic discharge immunity test method for processor chip

An electrostatic discharge and immunity technology, applied in the field of electrostatic discharge immunity test components, can solve the problems of no electrostatic discharge test standard, no standard for high-speed signal injection of integrated circuits, etc., to improve convenience and test efficiency. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

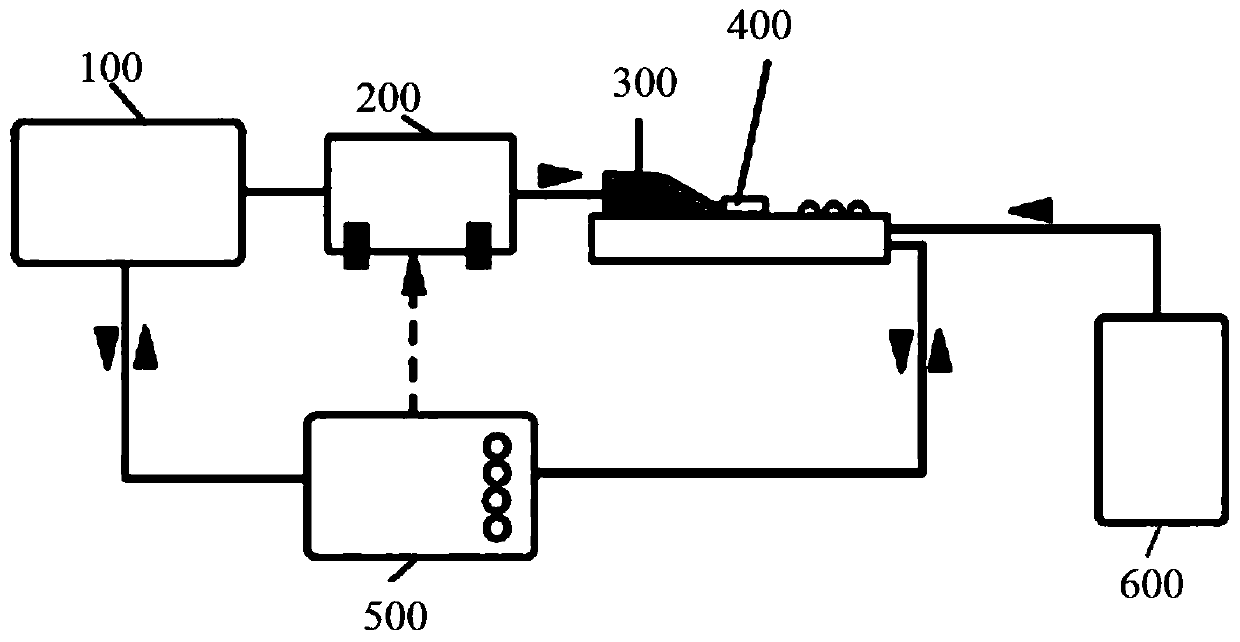

[0024] The present embodiment discloses a kind of ESD immunity testing assembly for processor chips, including: non-capacitance probes and capacitive probes respectively used to test the immunity of different pins of IC chips; and also including probe connections One end is used to connect the output end of the electrostatic discharge generator, and the other end is used to detachably connect the non-capacitive probe or the capacitive probe.

[0025] In this embodiment, the capacitance carried by the probe with capacitance is a coupling capacitance that can be connected in series between the probe connector and the single-ended signal pin of the high-speed DDR chip under test.

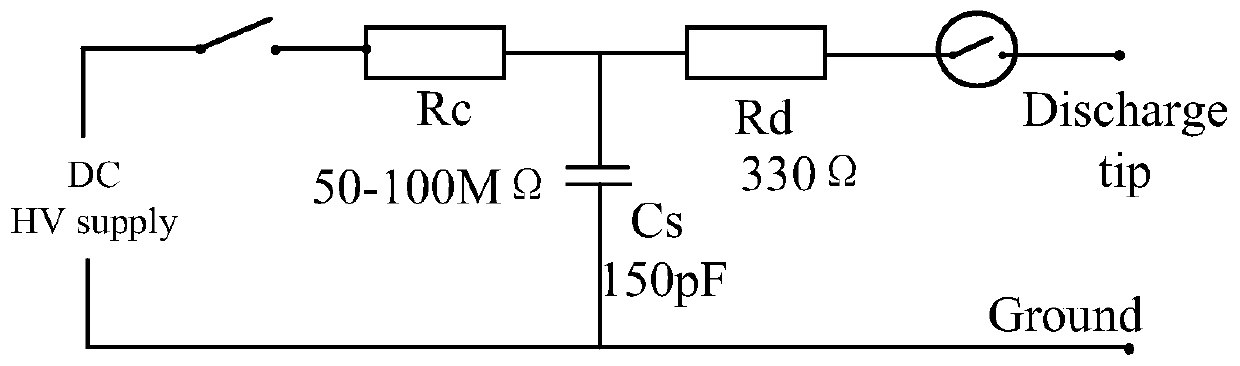

[0026] In this embodiment, it is equivalent to splitting the traditional system-level non-detachable probe into a probe connector and a non-capacitance probe. The circuit structure of the probe connector can be as follows: figure 1 circuit shown.

[0027] In the traditional IC ESD test, the ESD probe ...

Embodiment 2

[0042] Corresponding to the above component embodiments, this embodiment discloses an electrostatic discharge immunity test method for processor chips, including:

[0043] Step S1. Divide the pins of the tested IC chip into two types; one type is based on the non-capacitance probe for immunity test, and the other type is based on the capacitive probe for immunity test.

[0044] Step S2: Determine the type of the pin to be tested, and select the corresponding non-capacitance probe or probe with capacitance to connect to the electrostatic discharge generator via the probe connector for testing.

[0045] Preferably, the present embodiment method also includes:

[0046] Step S3, when measuring the single-ended signal of the high-speed DDR chip, select the probe with capacitance for testing, the capacitance carried by the probe with capacitance can be connected in series between the probe connector and the high-speed DDR chip under test Coupling capacitance between single-ended si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More