Chip and capacitive isolation circuit

An isolated circuit and capacitive technology, applied in the direction of logic circuit interface device, logic circuit connection/interface layout, etc., can solve the problem of high circuit cost, achieve strong suppression ability, reduce circuit cost, and reduce the number of effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0054] The present invention will be described in detail below in conjunction with various embodiments shown in the drawings. However, these embodiments do not limit the present invention, and structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

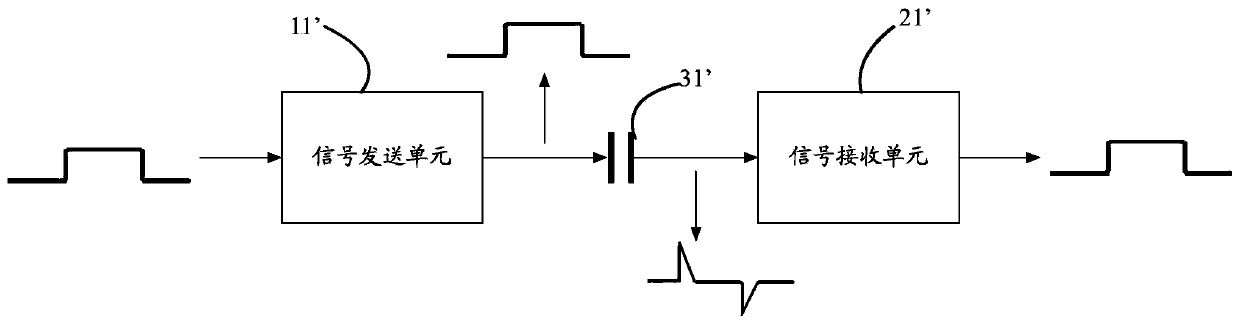

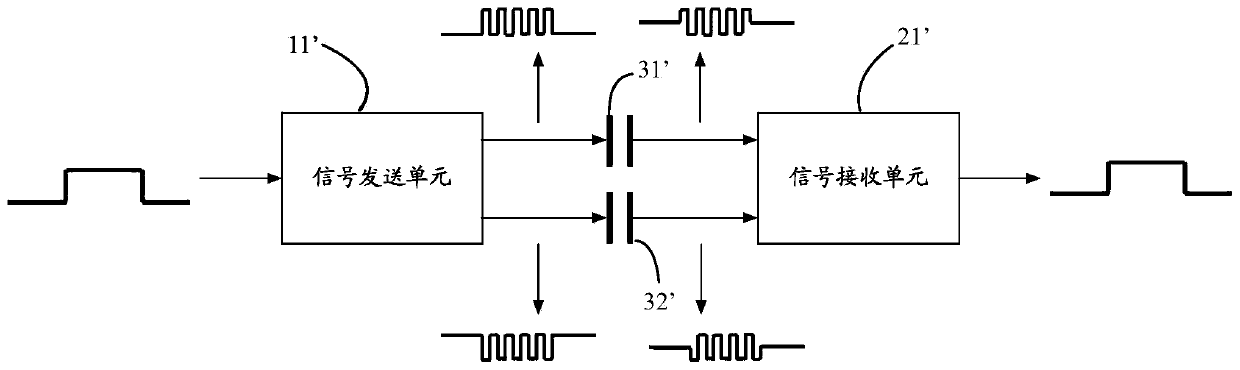

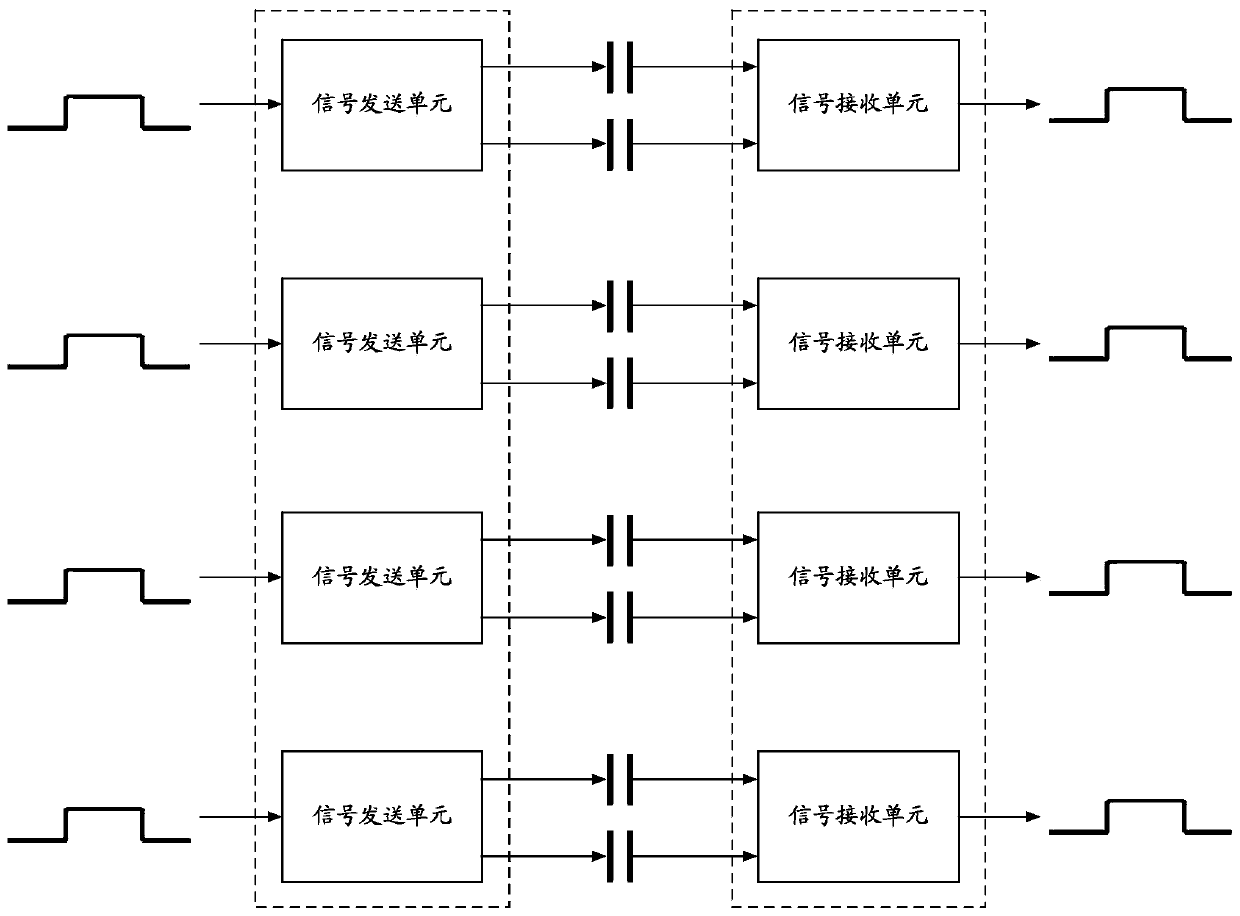

[0055] The invention discloses a chip. The chip includes several signal sending units and / or signal receiving units, and several clock generating units and / or clock receiving units. The channel, the clock generating unit and the clock receiving unit are used to generate or receive clock signals to modulate or demodulate signals transmitted in the signal channel.

[0056] The invention also discloses a capacitive isolation circuit, comprising:

[0057] The first chip includes several signal sending units and / or signal receiving units, and several clock generating units and / or clock receiving units;

[0058] The second ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com