NOR FLASH chip and method for eliminating over-erasing in erasing process of NOR FLASH chip

An over-erasing and chip technology, which is applied in the field of NORFLASH chip and eliminates over-erasing in its erasing process, can solve the problem of non-volatile memory such as long time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

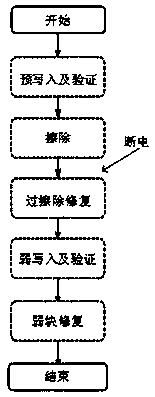

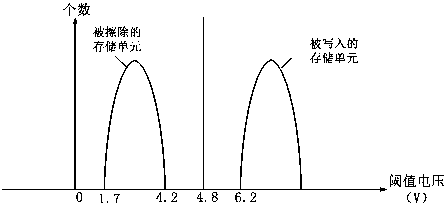

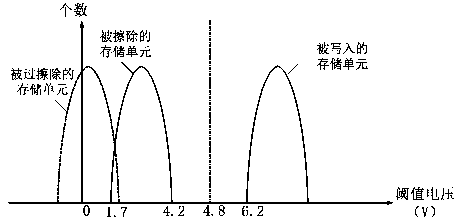

[0034] refer to figure 2 , figure 2 It is a schematic diagram of the relationship between the erased and written memory cells and the threshold voltage in the NOR FLASH chip. Such as figure 2 As shown, under normal circumstances, the memory cells in the NOR FLASH chip include erased memory cells (threshold voltage 1.7v~4.2v) and written memory cells (threshold voltage above 6.2v). When the chip is power-off during the erasing process, for example, the power-off occurs at the stage before erasing and repairing the target block after erasing the target block, and some memory cells will be erased. The phenomenon of over-erasing will occur, and the threshold voltage of some of these over-erased memory cells will be less than 0v, which will cause the read operation after NOR FLASH is powered on again, because of the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com