Semiconductor structure and forming method thereof

A semiconductor and pattern area technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as device performance and performance uniformity to be improved, avoid etching load effects, increase pattern density, and uniformity. good effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] It can be seen from the background art that the performance and performance uniformity of devices formed by existing processes still need to be improved. The reason why the performance of the device needs to be improved is analyzed in combination with a method of forming a semiconductor structure.

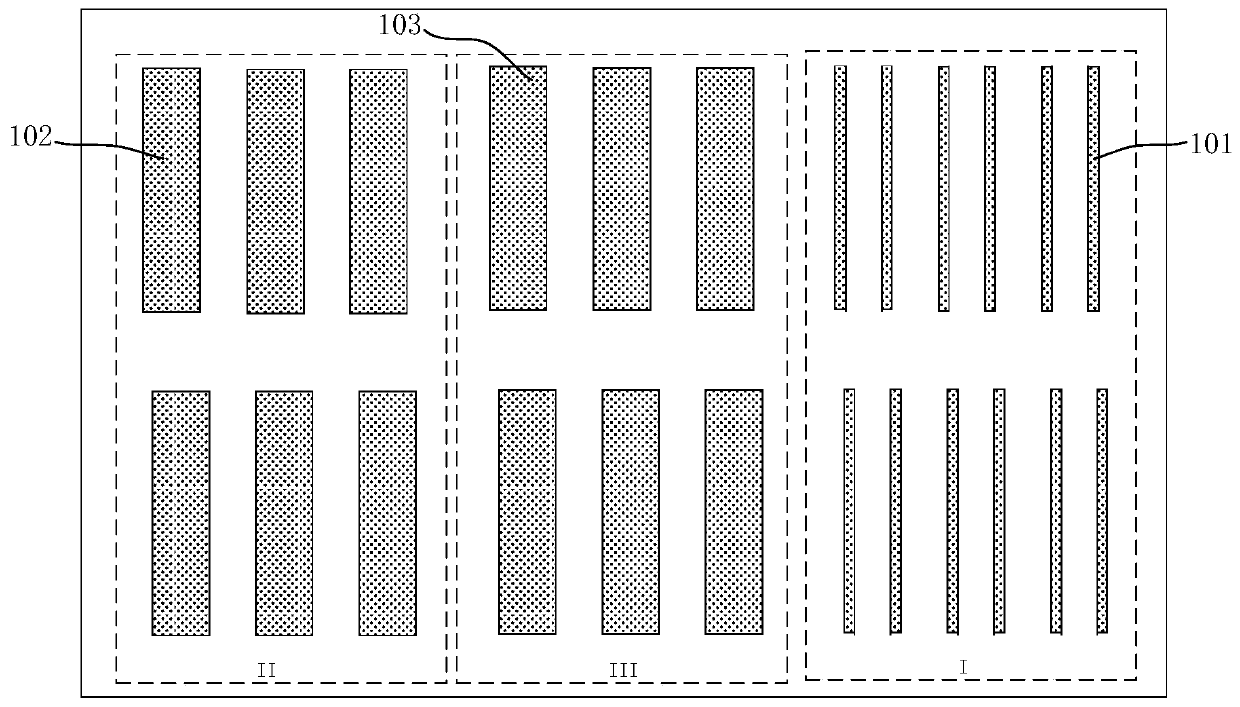

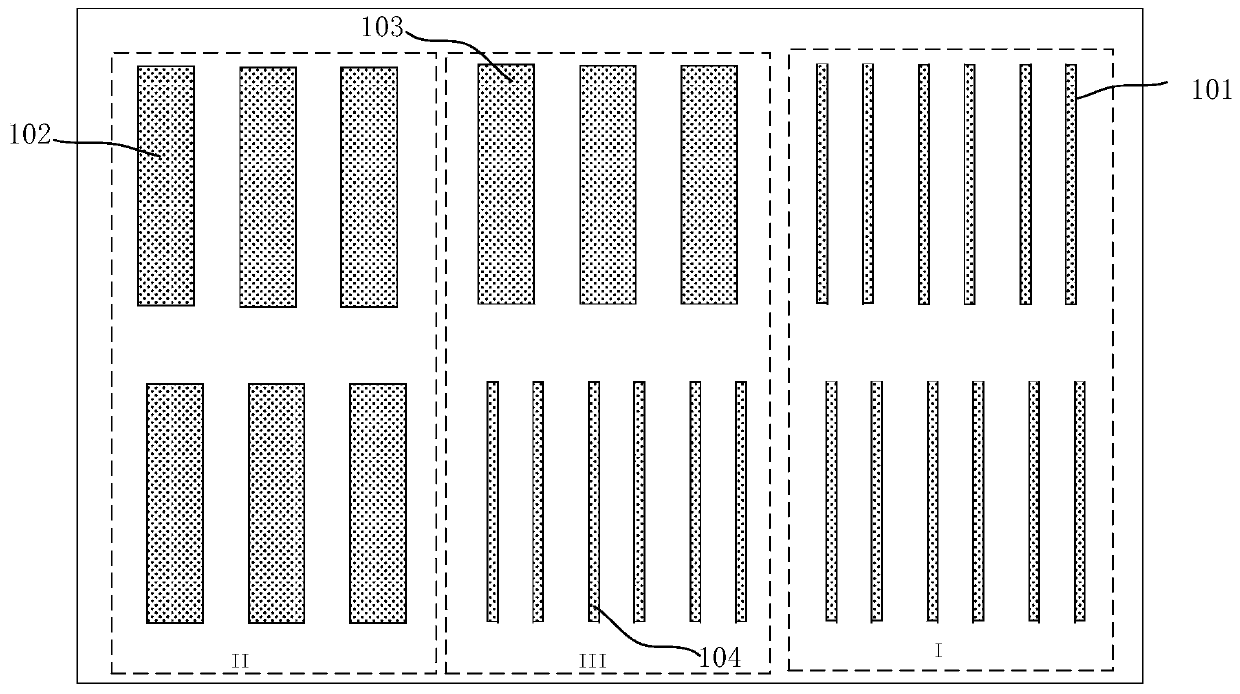

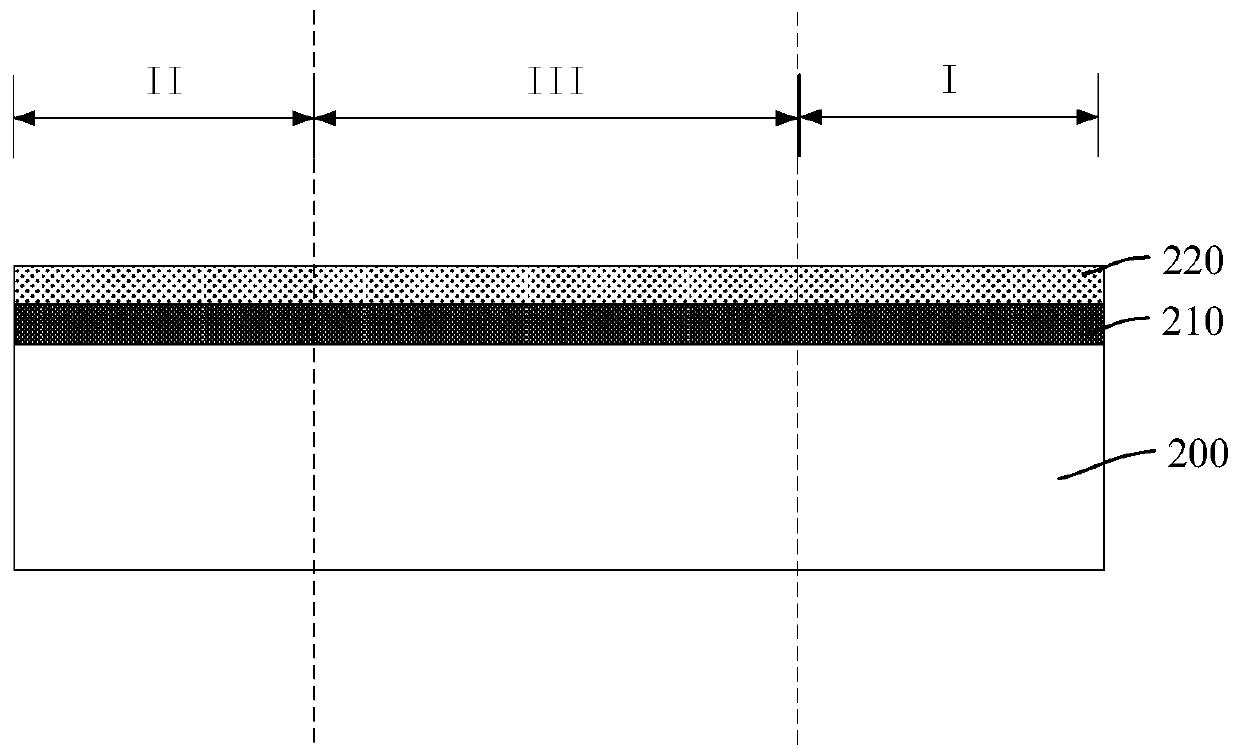

[0013] Specifically, in the process of forming the gate structure, mask patterns of different sizes are formed through different processes, for example, refer to figure 1 A mask pattern layout structure diagram shown in , a small-size mask pattern 101 is formed in the GM region I by a self-aligned double patterning (self-aligned double patterning, SADP) process, and a photolithography and etching process A large-size mask pattern 102 is formed in the GT region II, and then a gate structure of a corresponding size is formed by etching using the two mask patterns as a mask. However, in the process of forming mask patterns of different sizes, due to the low pattern density, th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More