Target system and method of determining alignment error in electronic substrates

A technique for measuring tools and alignment errors, applied in the photoengraving process, circuits, electrical components, etc. of the pattern surface

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

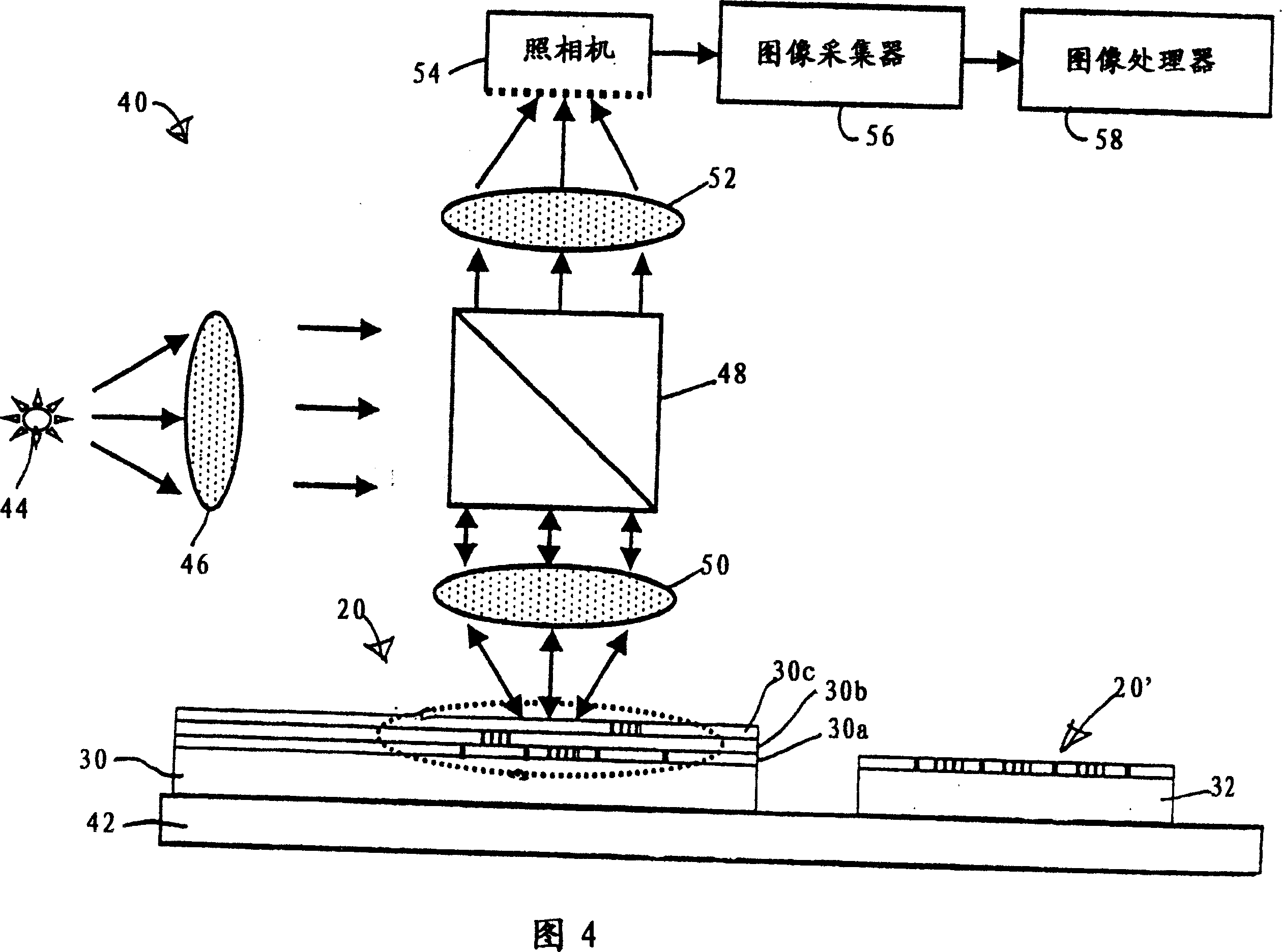

[0039] In describing the preferred embodiment of the invention, reference will be made to the accompanying drawings 2-14, wherein like numerals indicate like parts of the invention.

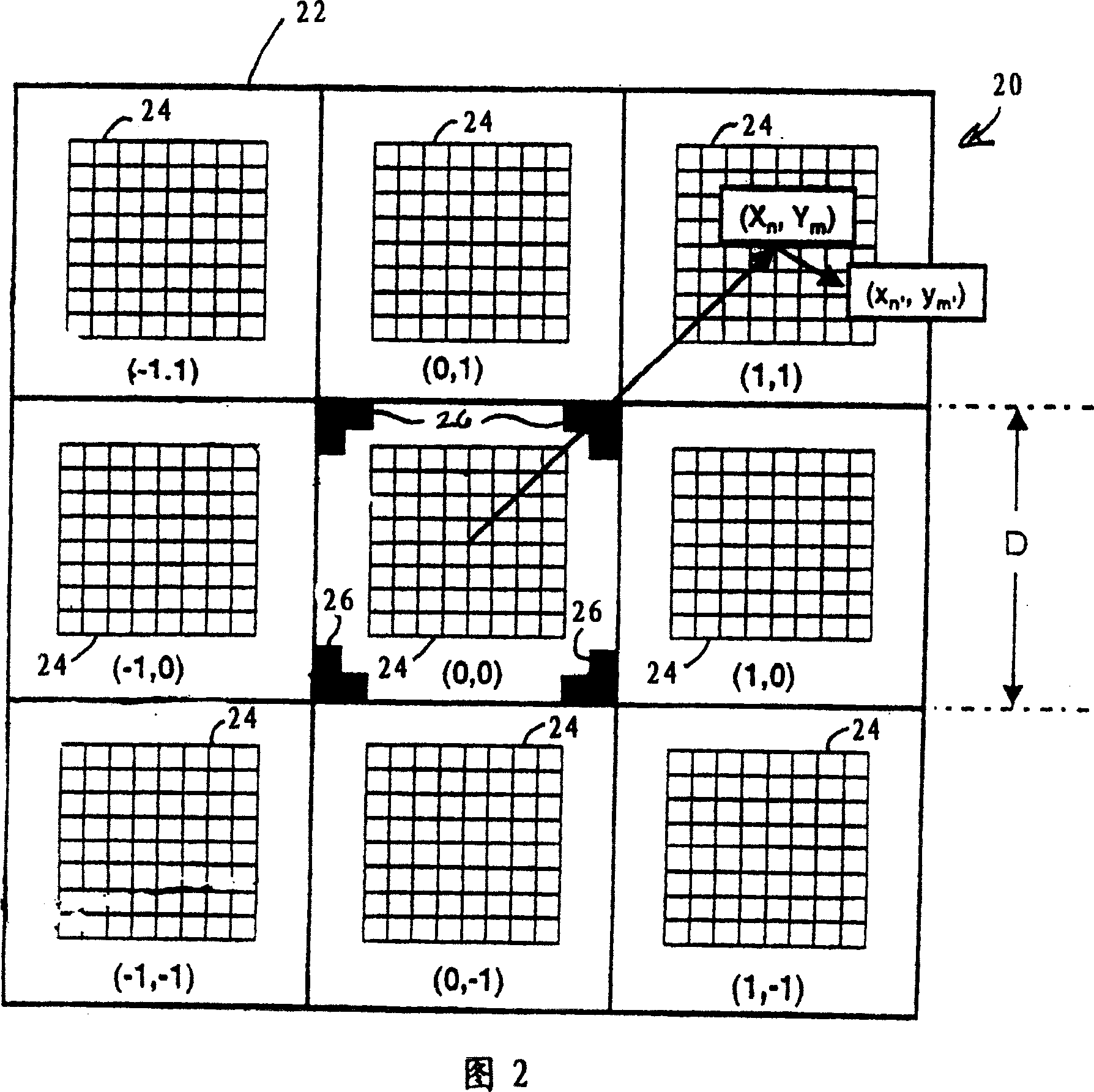

[0040] Figure 2 shows an example of overlapping targets of the present invention. The overlay target 20 is composed of nested grid patterns, with the outer pattern 22 serving as a reference grid and the plurality of sub-patterns 24 serving as sub-grids. The area of reference grid portions of overlapping targets is divided into an N x M array of preferably equal area grid portions, called boxes, represented by a reference grid pattern of period D printed on the first layer of the patterning sequence. The reference grid includes at least one row of connected boxes, ie a plurality of grid segments in at least one direction of x and y, such that N is greater than or equal to one and M is greater than one. Preferably, the array has a plurality of grid segments in both the x and y directions such th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More