Semiconductor process chamber, wafer edge protection method and semiconductor equipment

A process chamber and edge protection technology, applied in discharge tubes, electrical components, circuits, etc., can solve the problems of edge protection ring failure, poor etching process uniformity, and low etching rate, etc., to facilitate switching and improve the angle. The effect of tilting, improving uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] In order for those skilled in the art to better understand the technical solutions of the present invention, the semiconductor process chamber, wafer edge protection method and semiconductor equipment provided by the present invention will be described in detail below with reference to the accompanying drawings.

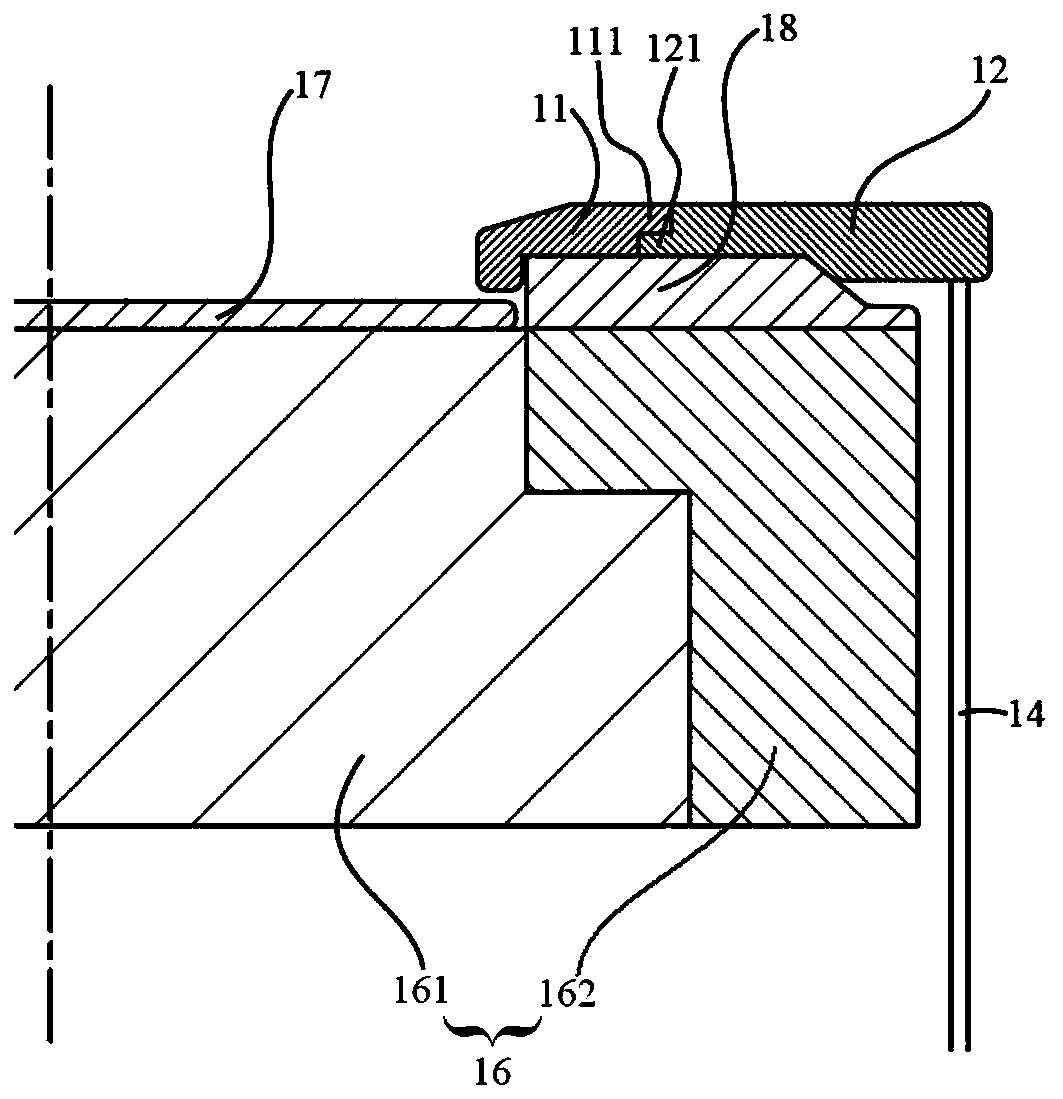

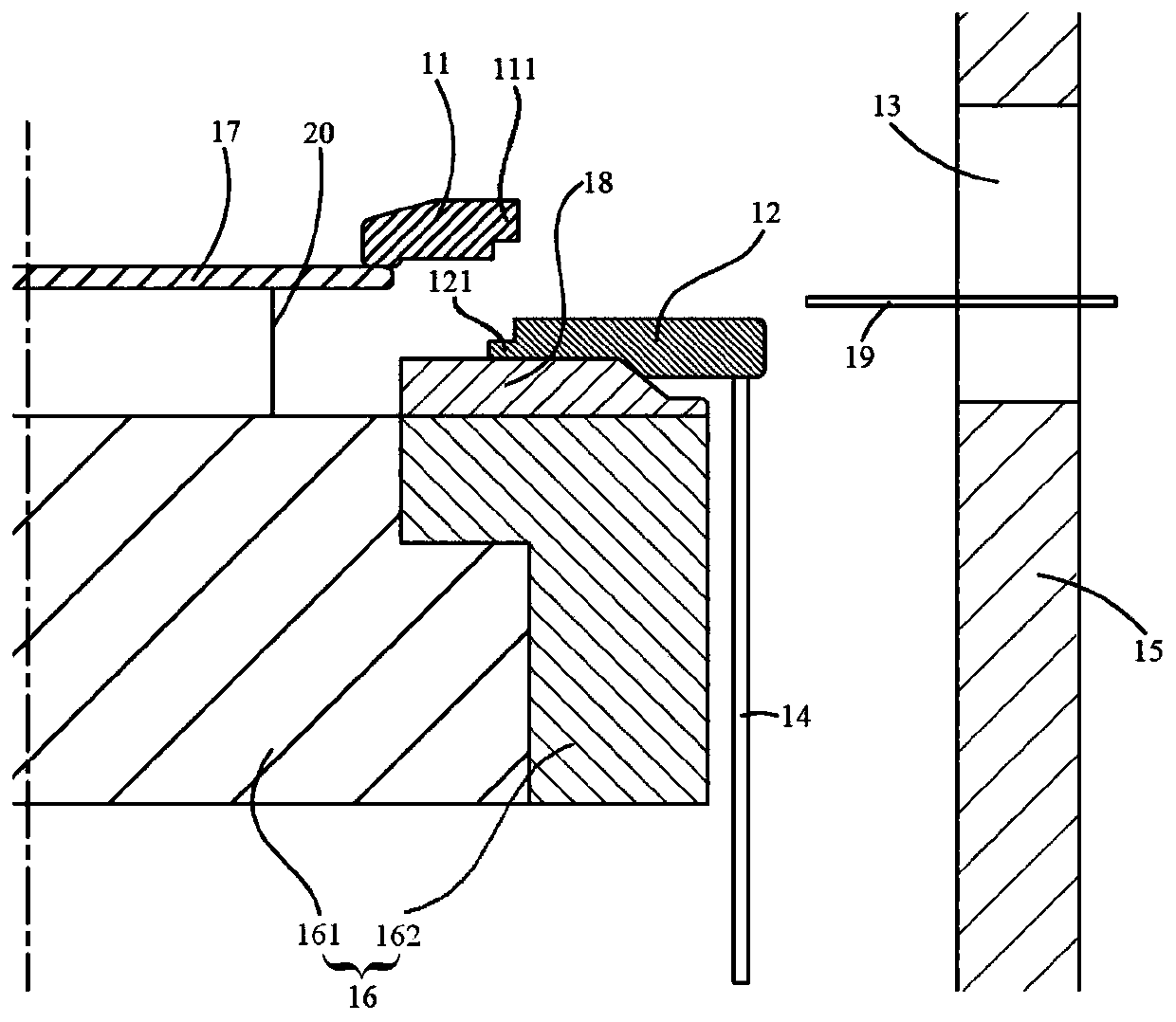

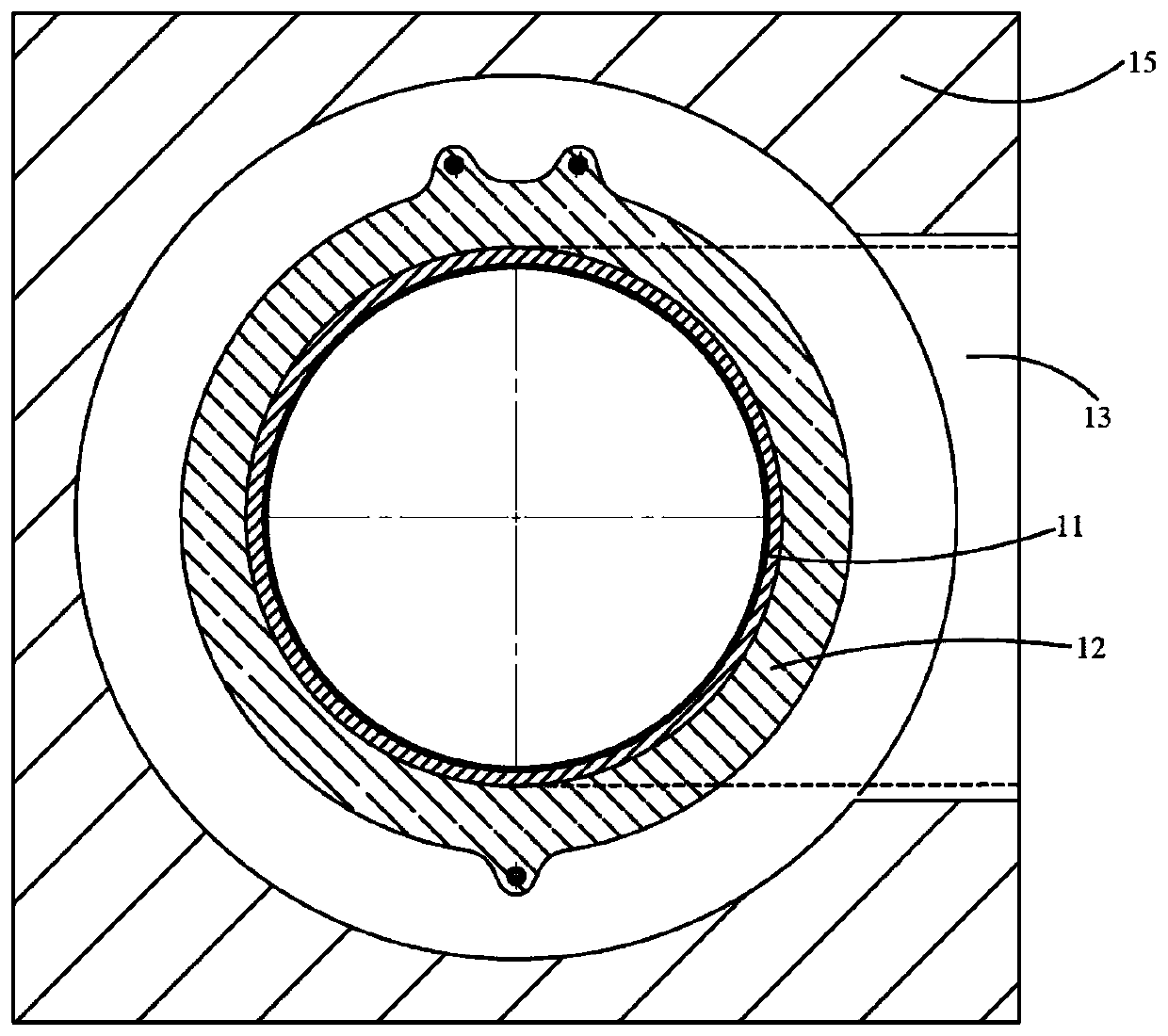

[0033] Such as Figure 1-Figure 3 As shown, the present embodiment provides a semiconductor process chamber. The semiconductor process chamber includes a base 16 and a wafer edge protection device, and the wafer edge protection device is arranged on the base 16. The wafer edge protection device includes an inner protection ring 11 and a wafer edge protection device. The outer protective ring 12; the outer protective ring 12 is arranged around the outer side of the inner protective ring 11, and is overlapped with the inner protective ring 11, and the outer protective ring 12 can drive the inner protective ring 11 to rise and fall synchronously; the inner diamete...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More