Super-large-scale integrated circuit layout method considering atomization and proximity effects

A large-scale integrated circuit and proximity effect technology, which is applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as long running time and no consideration of proximity effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0090] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

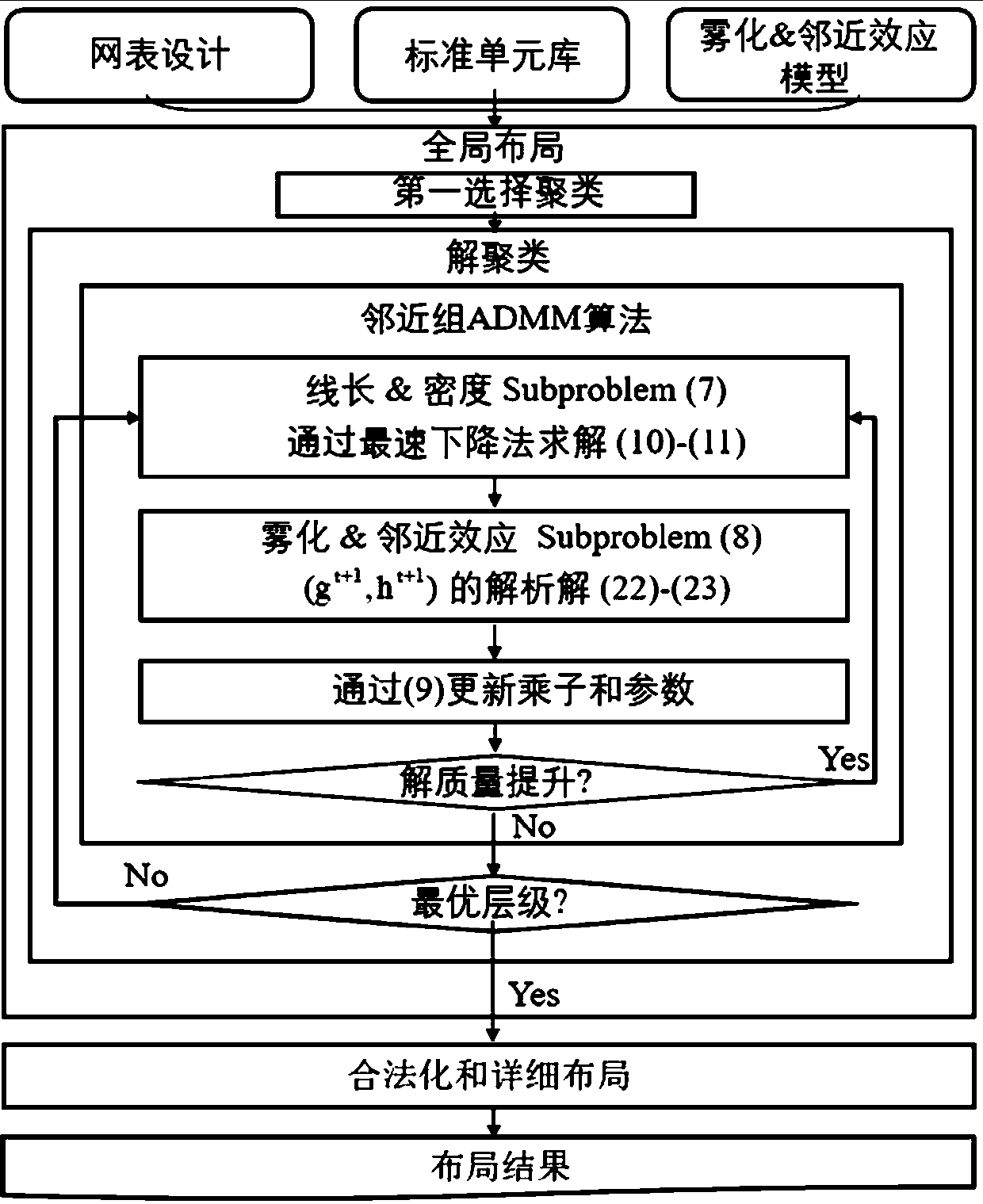

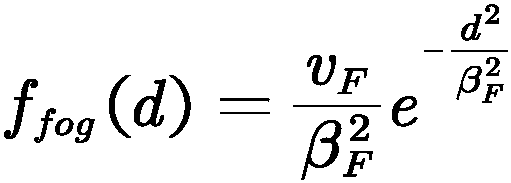

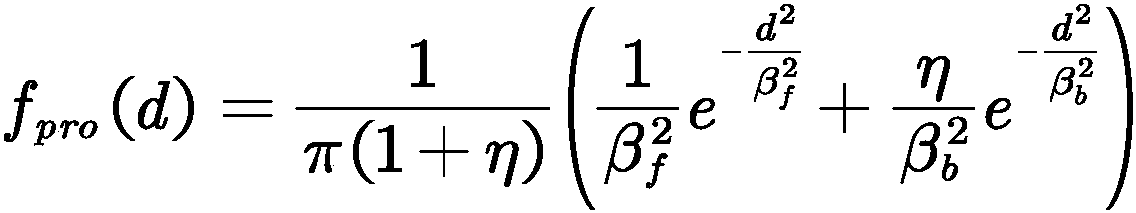

[0091] The present invention provides a VLSI layout method considering atomization and proximity effect to solve the VLSI layout problem considering atomization and proximity effect, thereby reducing the adverse effects caused by atomization and proximity effect, thereby improving layout efficiency . The basic idea of this method is to formulate the global layout problem as a separable linear constraint minimization problem. According to the energy model of atomization and proximity effect, solving the targets one by one in an alternating manner, writing out the proximity group and solving it also greatly reduces the complexity of the optimization problem and reduces the computational cost, thus effectively reducing the The effects of fogging and proximity effects are eliminated. In each iteration of the method, two subproblems are solved w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More