DC transient step response delay test method, system and device

A step-response and time-delay testing technology, applied in measuring devices, measuring electrical variables, instruments, etc., can solve problems such as large test errors, and achieve the effect of avoiding errors and simplifying test loops

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The present invention will be further described below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, but not to limit the protection scope of the present invention.

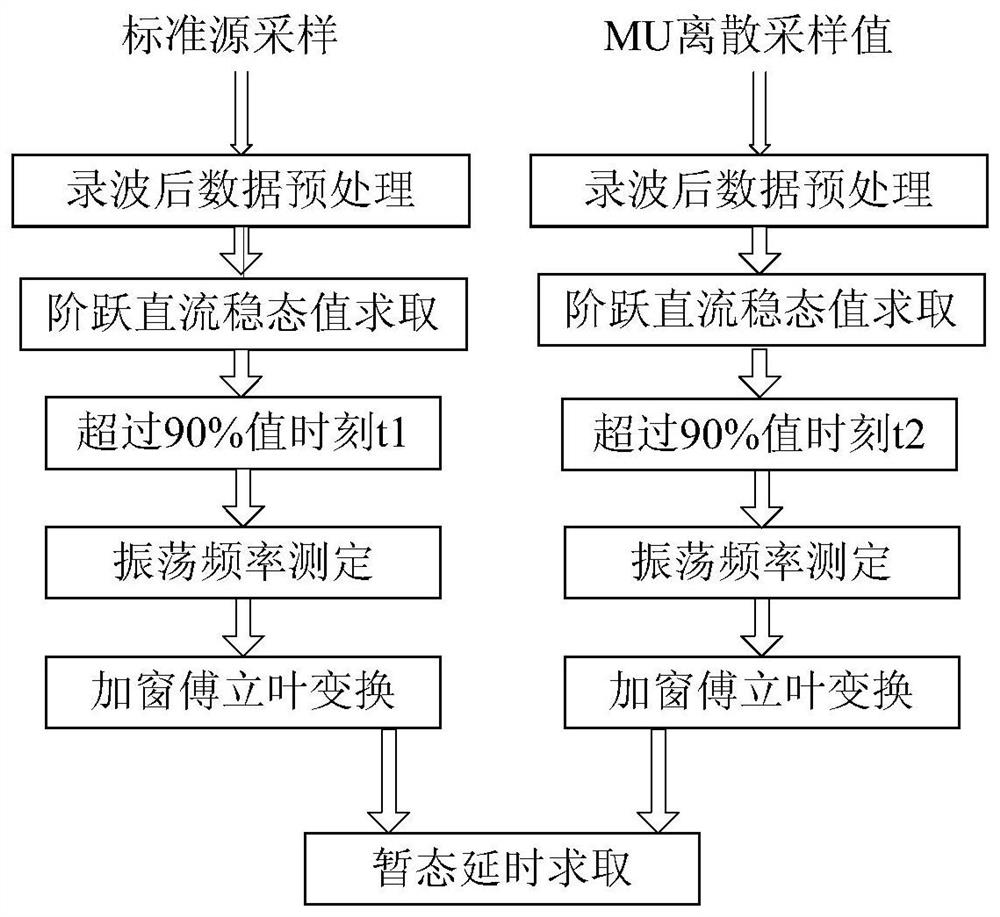

[0040] like figure 1 As shown, a DC transient step response delay test method includes the following steps:

[0041] Step 1, recording and sampling the standard source signal and the second-order step oscillation attenuation current signal and performing preprocessing.

[0042] The sudden change is recorded and sampled, and the sudden change algorithm is as follows:

[0043] Δi=|[i(t)-i(t-T)]-[i(t-T)-i(t-2T)]|

[0044] Among them, i is the instantaneous value of the current, t is the current moment, and T is a power frequency cycle. When Δi is greater than the preset startup customization, the wave recording and sampling will be started.

[0045] Step 2, use generalized polynomial fitting to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More