Chip metal bump forming method

A metal bump and molding method technology, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc. The effect of repairing damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

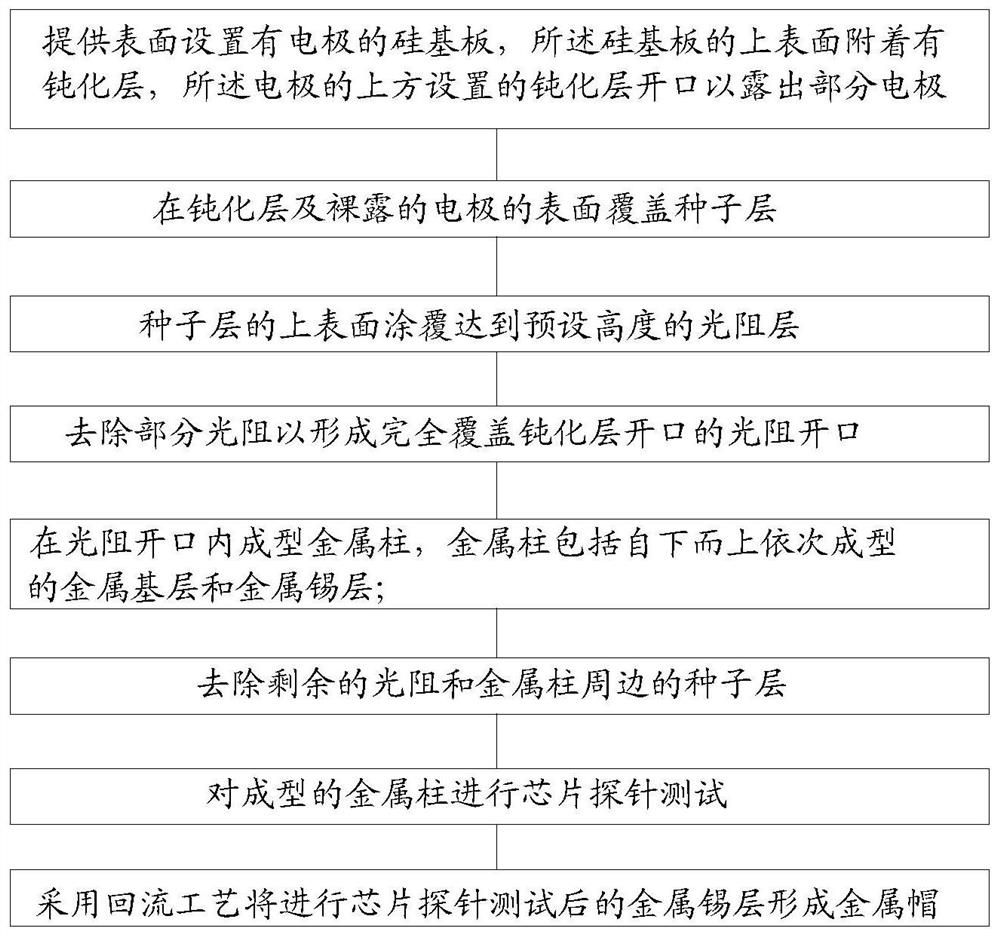

[0039] Embodiments of the present invention: as figure 1 As shown, a chip metal bump forming method is disclosed, comprising the steps of:

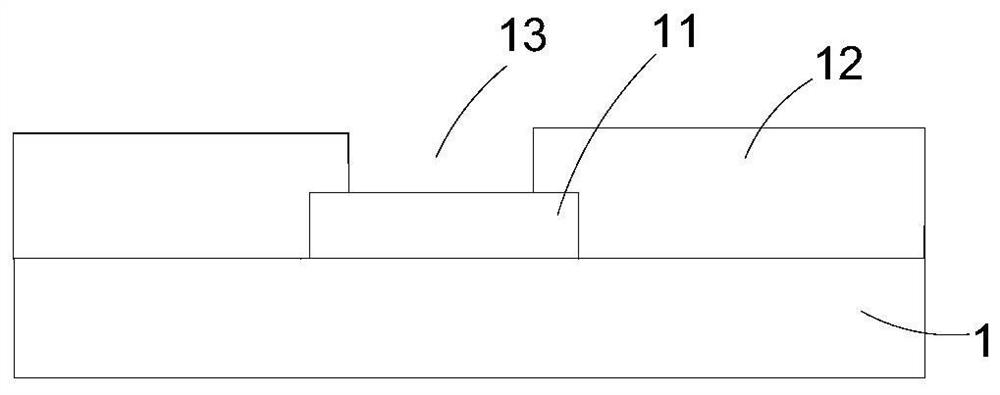

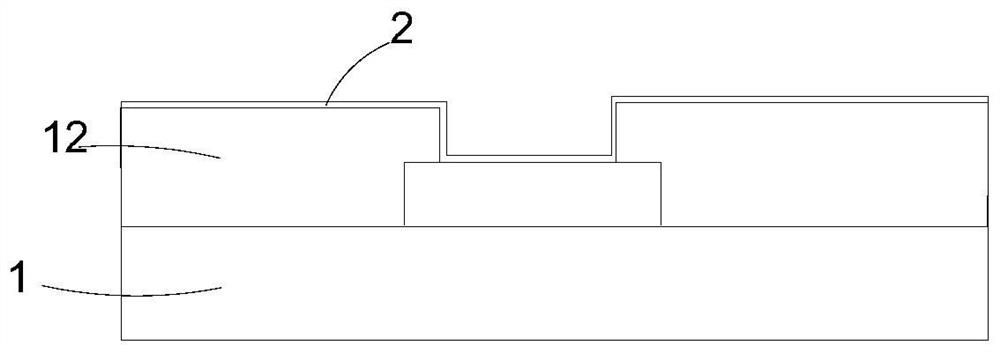

[0040] Step 101 : providing a silicon substrate 1 , an electrode 11 and a passivation layer 12 are formed on the upper surface of the silicon substrate 1 , and the electrode 11 is exposed from a passivation layer opening 13 on the passivation layer 12 . An electrode 11 is formed on the silicon substrate 1, a passivation layer 12 covers the silicon substrate 1 and part of the electrode 11, the passivation layer 12 overlaps the edge position of the part of the electrode 11, and the area of the electrode 11 not covered by the passivation layer 12 exposed outwards to form passivation layer openings 13, such as figure 2 shown.

[0041] S103: if image ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Wavelength | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap