Semiconductor structure and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem that the planar process and manufacturing technology cannot meet the growing and changing needs of semiconductor devices, etc. The effect of improving performance, simplifying process, reducing cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

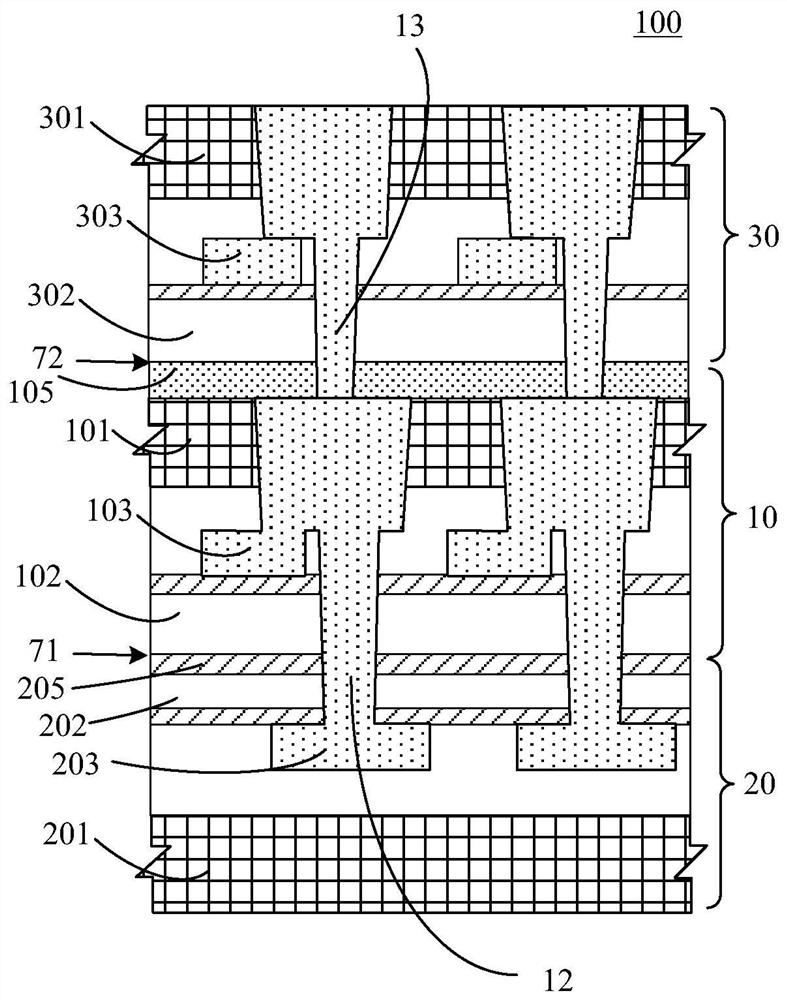

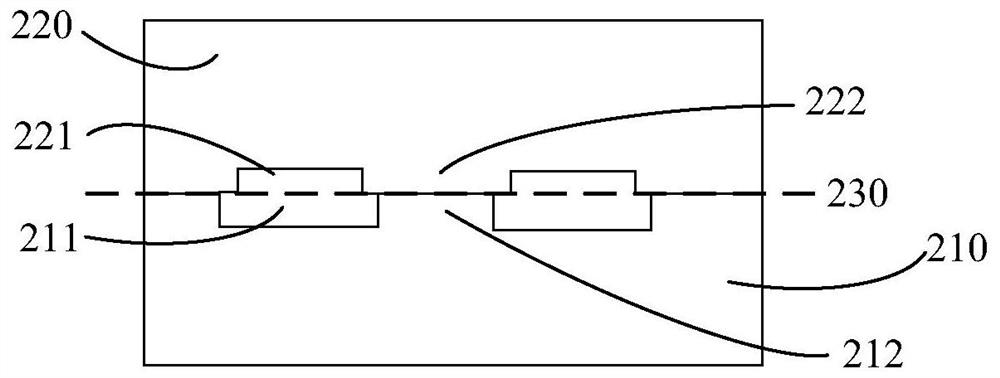

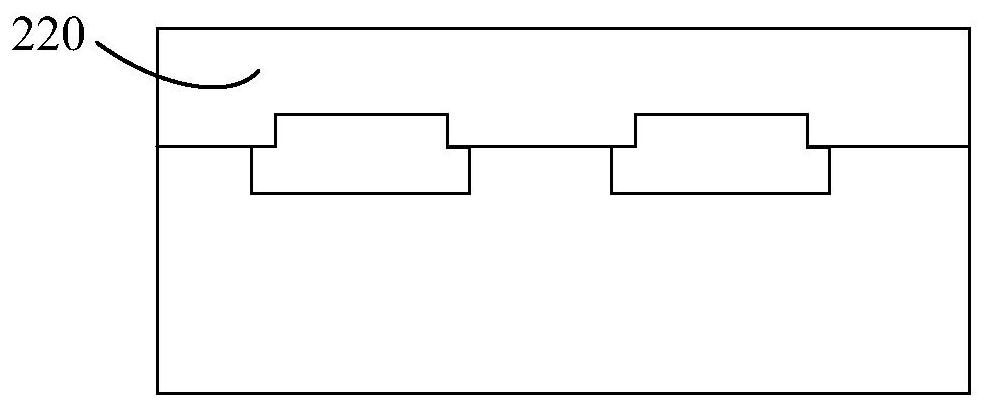

[0032] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0033] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways than those described here, so the present invention is not limited by the specific embodiments disclosed below.

[0034] As indicated in this application and claims, the terms "a", "an", "an" and / or "the" do not refer to the singular and may include the plural unless the context clearly indicates an exception. Generally speaking, the terms "comprising" and "comprising" only suggest the inclusion of clearly identified steps and elements, and these steps and elements do not constitute an exclusive list, and the method or device may also contain other st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More