Manufacturing method of semiconductor device

A manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as short circuit of devices, large difference in etching thickness, poor interface flatness, etc., and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

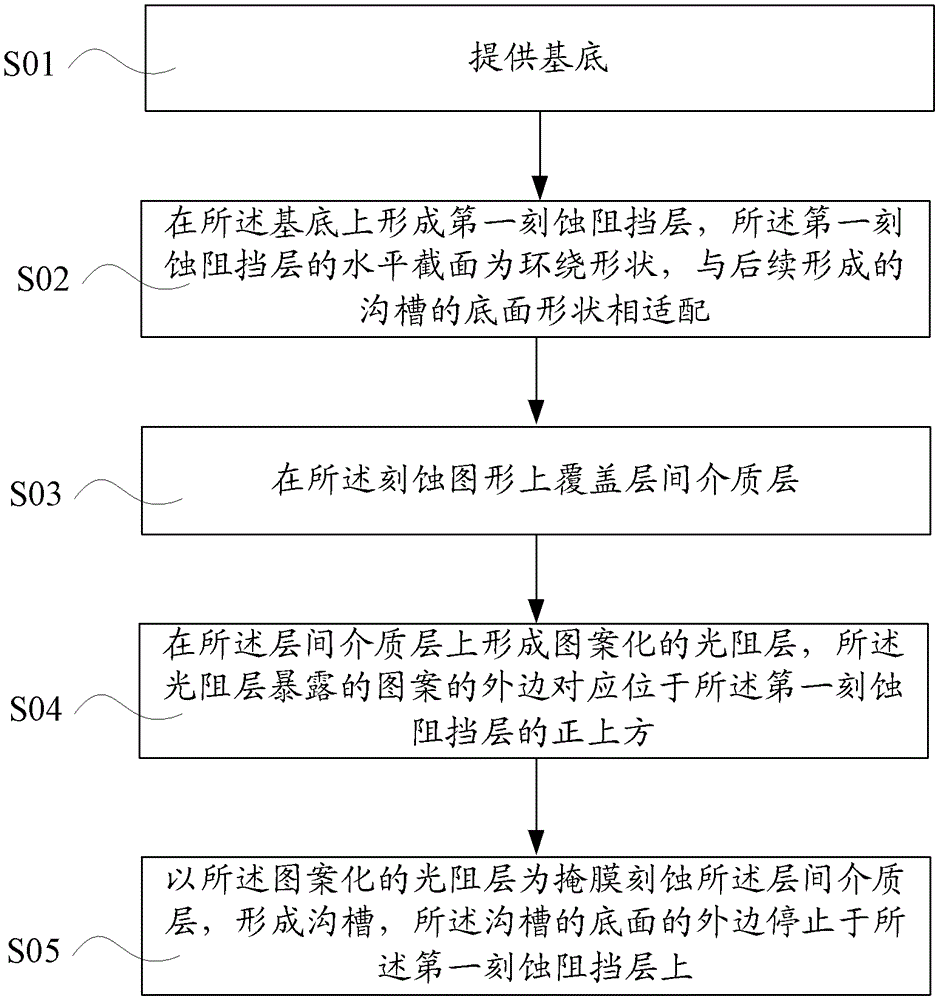

[0041] combine Figure 4 and Figure 5 , in step S01, a substrate 100 is provided, and the substrate 100 may be a semiconductor substrate with active circuits, or may be a previous metal interconnection layer.

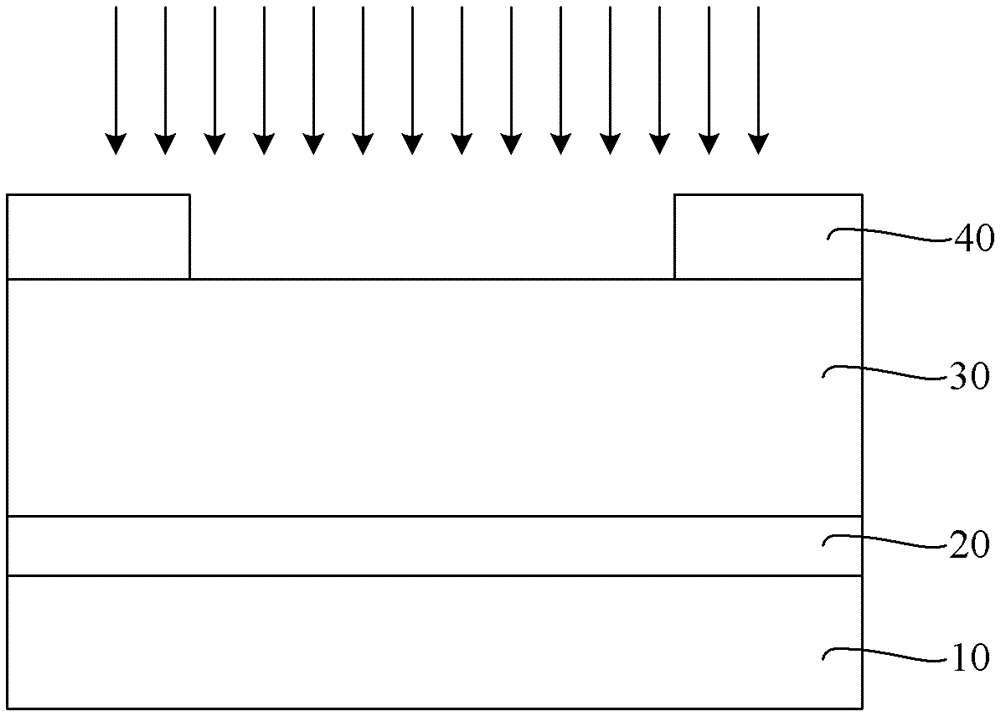

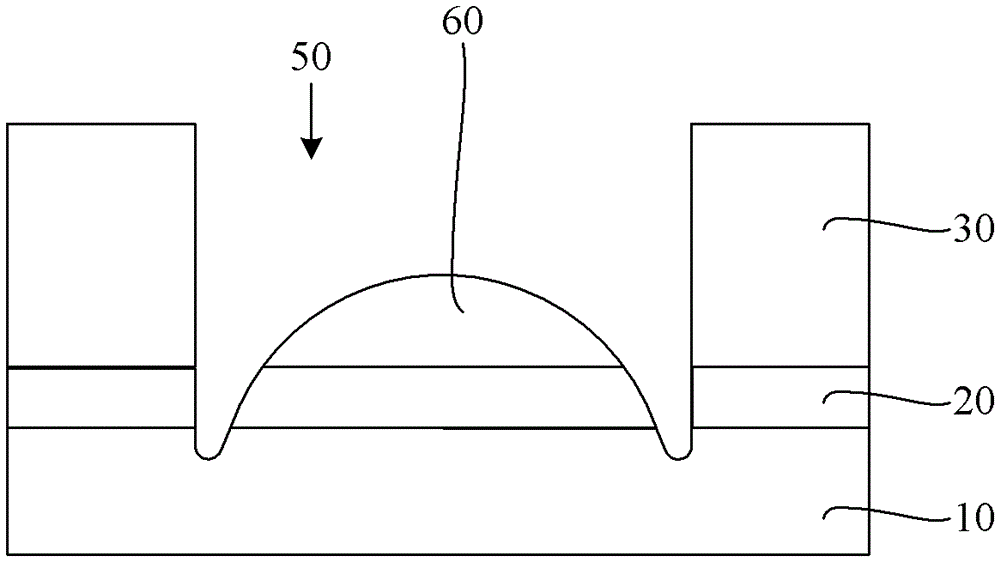

[0042] continue to refer Figure 4 and Figure 5 , in step S02, first form a first etch barrier film (not shown in the figure) on the substrate 100, and use photolithography and etching processes to pattern the etch barrier film to form a first etch barrier layer 201, the horizontal cross-section of the first etch barrier layer 201 is in the shape of a circle, and the pattern formed around the first etch barrier layer 201 is adapted to the shape of the bottom surface of the subsequently formed trench, and the specific shape is formed according to needs The shape of the groove is determined, such as a circular ring or a "mouth", such as Figure 5 As shown, in this embodiment, taking the bottom of the groove as a rectangle as an example, the horizontal section of the...

Embodiment 2

[0050] combine Figure 9 ~ Figure 11 , on the basis of Embodiment 1, in step S02, the sequence of forming the first etch barrier layer 202 and the second etch barrier layer 202 is changed; specifically, in this embodiment, the substrate 100 is first covered with the second The barrier layer 202, and then the first etch barrier film (not shown in the figure) is formed on the second etch barrier layer 202, and the first etch barrier film is patterned by photolithography and etching processes to form the first etch barrier film. layer 201, the first etch barrier layer 201 and the underlying second barrier layer 202 together form an etch barrier pattern 203; in this embodiment, the first etch barrier layer 201 is located at the second etch barrier On the layer 202, the thickness of the etch stop at the outer edge of the bottom surface of the trench is also thickened, so that when the trench 500 is formed by etching, it overcomes the problem that the etching removal rate near the o...

Embodiment 3

[0052] On the basis of Embodiment 2, in this embodiment, in step S02, a relatively thick etch stop film (not shown) is deposited first, and then the etch stop film is patterned to form a first etch stop layer 201 and The etching pattern of the second barrier layer 202 under it, the structure formed is the same as that described in Embodiment 2 Figure 11 The structure is the same. Specifically, combined with Figure 9 to Figure 11 Firstly, a thicker etching stopper film is formed on the substrate 100, and then part of the thickness of the etching stopper film is etched by photolithography and etching processes, and the etching time is controlled so that the etching stopper film is formed by the first etching process. The etch barrier layer 201 and the barrier pattern 203 formed by the second etch barrier layer 202 below it, the etch barrier pattern 203 formed by the covering deposition process combined with the etching process can also thicken the outer edge of the bottom sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More