A latch-type amplifier offset elimination method and offset elimination circuit

A technology for eliminating circuits and amplifiers. It is applied in the direction of improving amplifiers to improve efficiency and improving amplifiers to reduce noise effects. It can solve problems such as limited application range, charge loss, and limited actual effect, and achieves improved application range, improved amplification accuracy, The effect of eliminating dissonance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

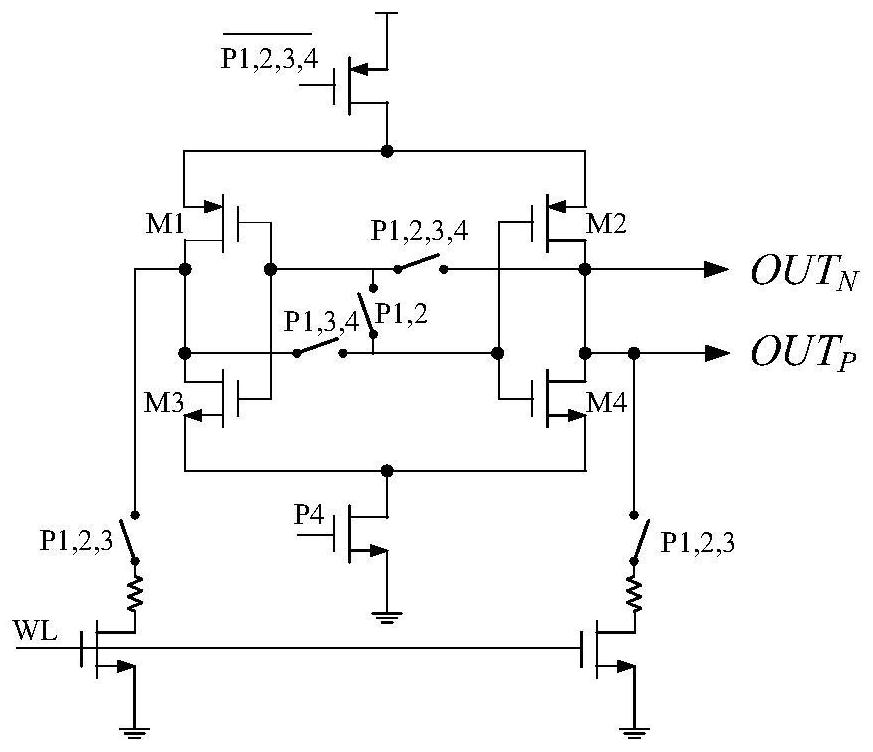

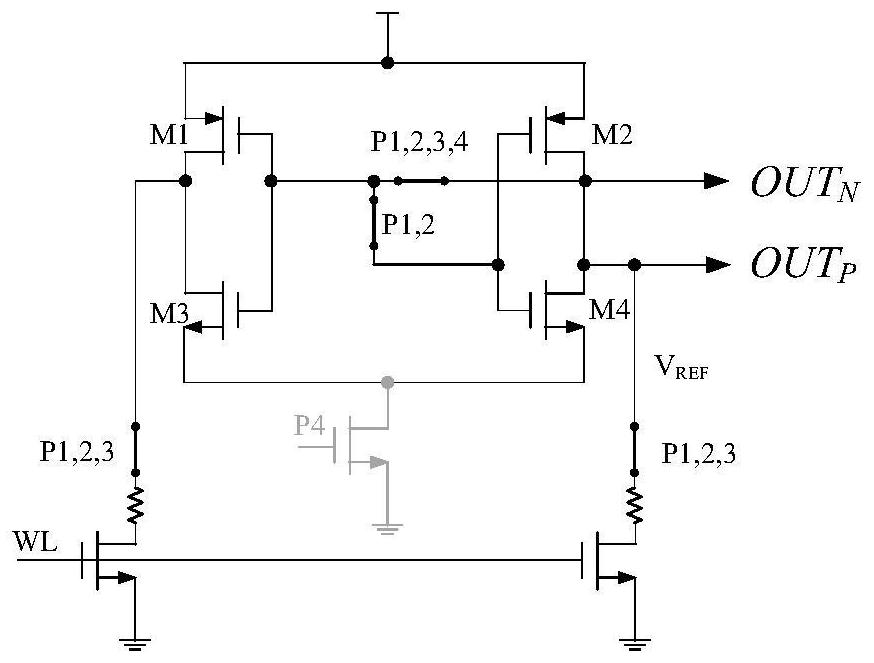

[0039] Implementation example: Figure 5 Shown is an implementation example of a latch-type amplifier offset cancellation circuit of the present invention. Input A and output B of the first inverter INV1 are connected to one end of C0 and C1 respectively, and input C and output D of the second inverter INV2 are connected to one end of C3 and C2 respectively. The specific circuit includes:

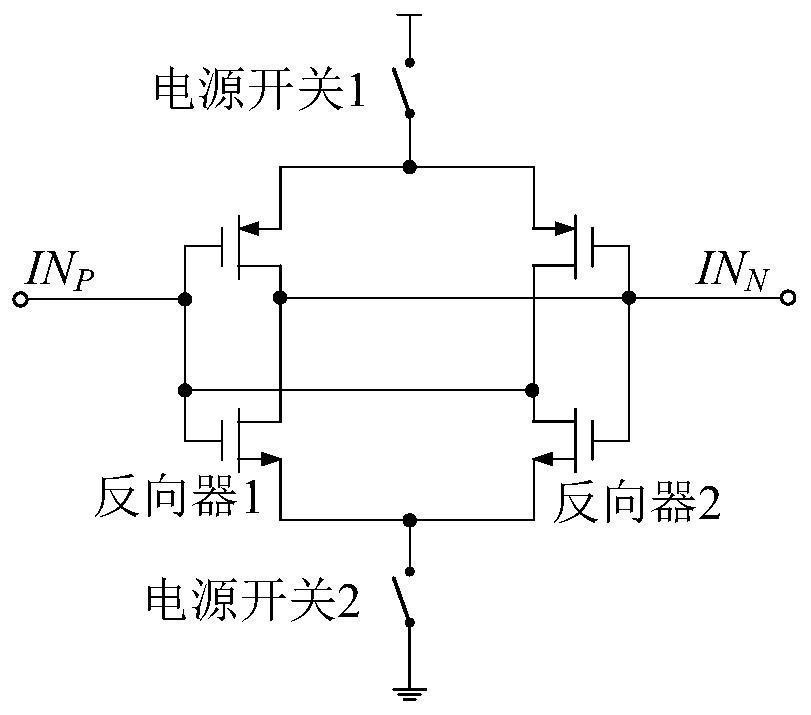

[0040] The first inverter INV1 and the second inverter INV2, four capacitors C0-C3, and twelve switches S1-S12, further include: a third inverter INV3 and a fourth inverter INV4; the first inverter INV3 and the fourth inverter INV4; The inverter INV1 and the second inverter INV2 are both amplifying inverters, the third inverter INV3 and the fourth inverter INV4 are two shaping inverters; the first inverter INV1 includes: a first transistor PMOS1 and the second transistor NMOS1, the gates of the input terminals of the first transistor PMOS1 and the second transistor NMOS1 are connected in ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More