Neural network hardware accelerator

A hardware accelerator and neural network technology, applied in the field of artificial intelligence, can solve problems such as poor computing power ratio, no advantage in power consumption efficiency of neural network hardware accelerators, and less optimization of RNN neural network calculations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The following will clearly and completely describe the technical solutions in the embodiments of the application with reference to the drawings in the embodiments of the application. Apparently, the described embodiments are only some of the embodiments of the application, not all of them. Based on the embodiments in this application, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the scope of protection of this application.

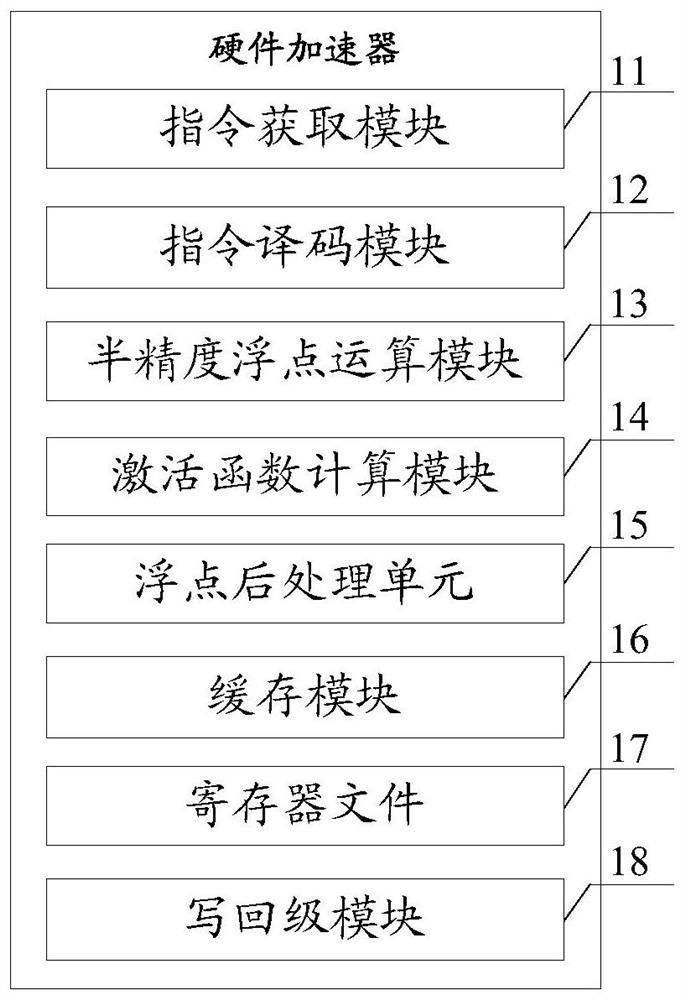

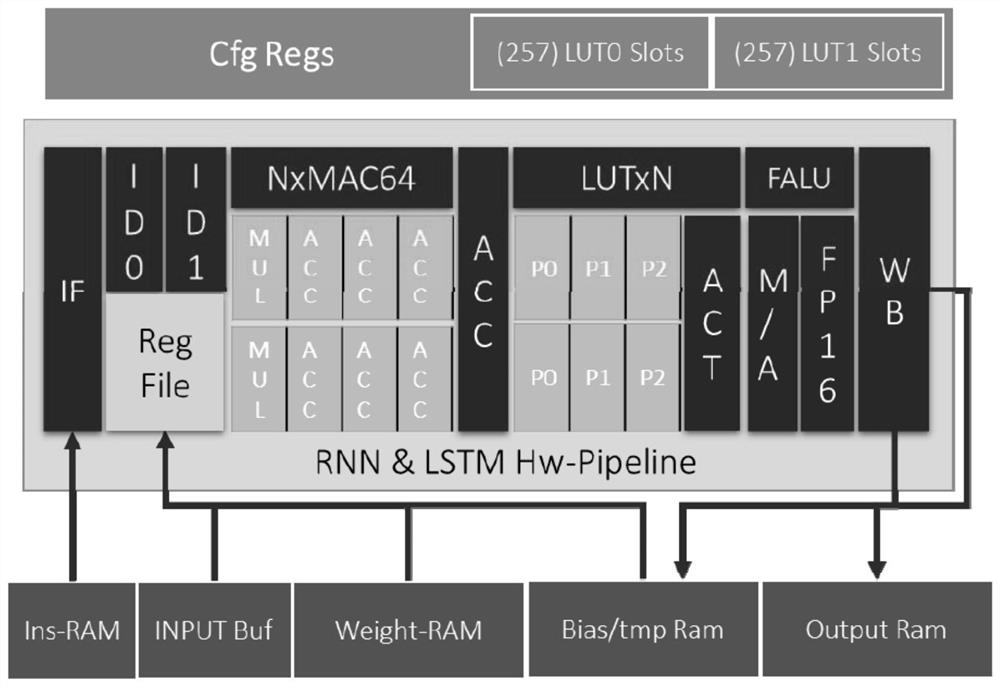

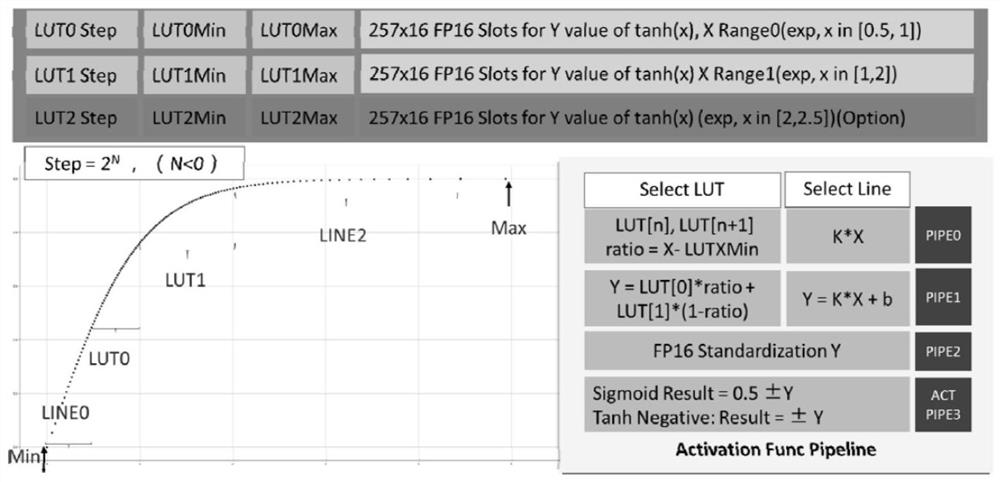

[0045] Currently, the architecture of neural network hardware accelerators is biased towards CNN optimization. Although these neural network hardware accelerators can also be used for RNN neural networks, there is little calculation optimization for RNN neural networks, and the calculation efficiency ratio is too poor, resulting in a lot of waste of resources. More waste of resources means lower power consumption and computing power. In this way, the architecture of neural network h...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More