A kind of power semiconductor device and its manufacturing method

A technology for power semiconductors and manufacturing methods, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only a part of the embodiments of the present invention, but not all of the embodiments. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

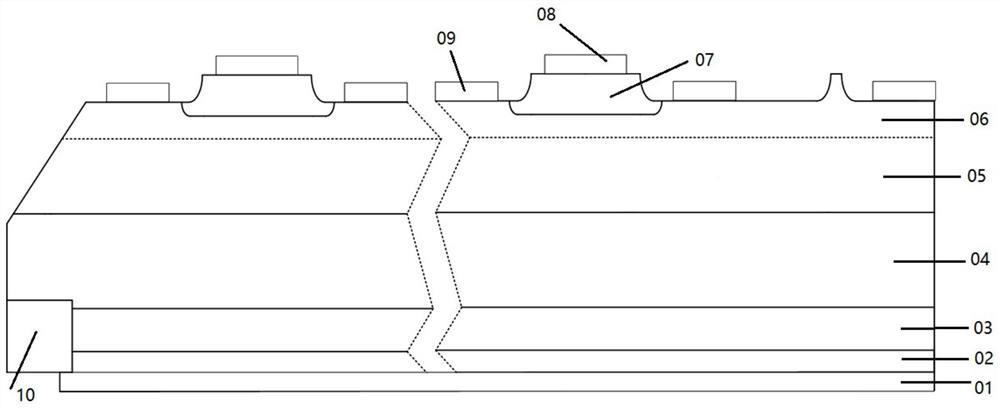

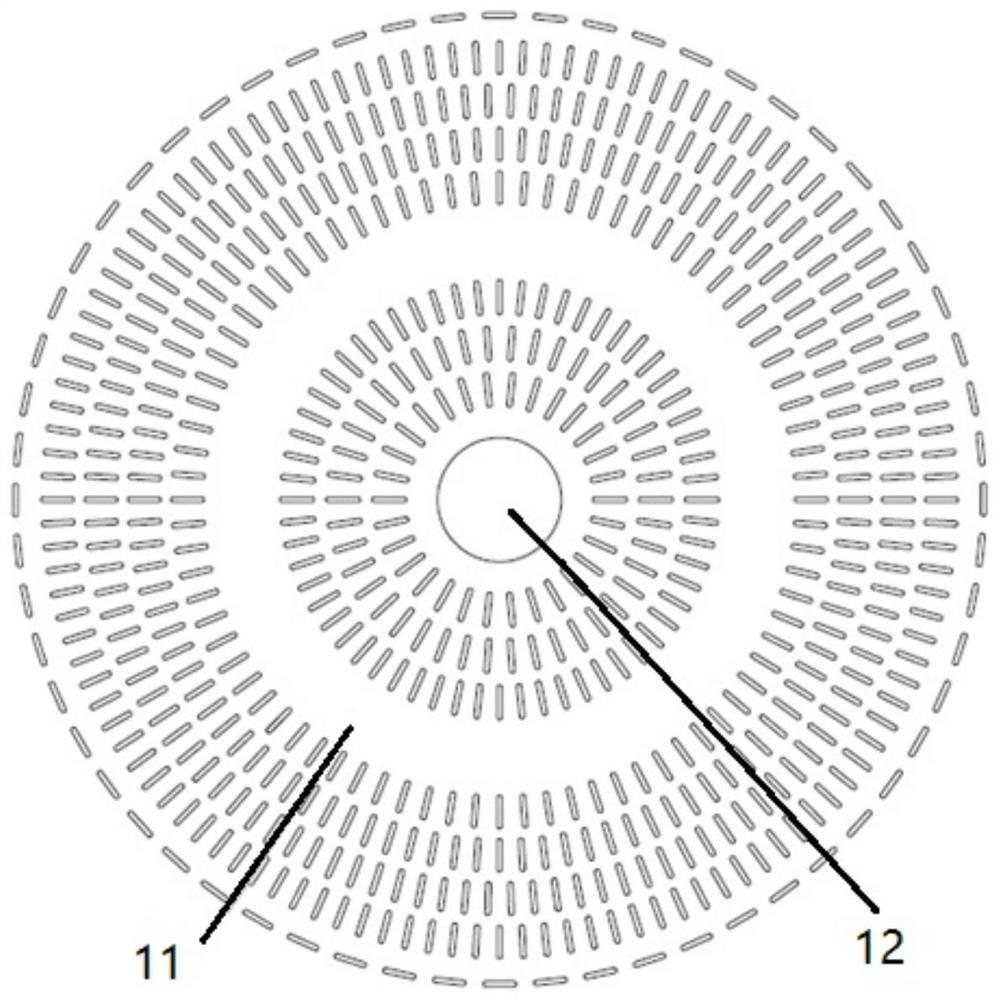

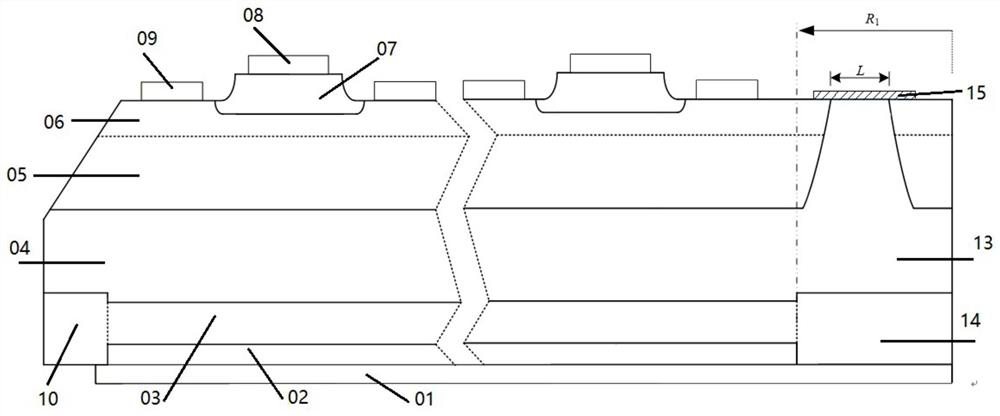

[0027] The power semiconductor device described in the present invention may be a GCT. like figure 1 As shown, the existing GCT mainly includes a PNPN four-layer structure in the longitudinal direction. According to the degree of doping, it can be subdivided into P+ transparent emission anode 02, N' buffer layer, N - Base 04, P Base 05, P + Base 06 and N + Emitter region 07 (also called cathode bar). In addition, GCT can also inc...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More