DDR3 controller based on DFI standard

A controller and standard technology, applied in instruments, electrical digital data processing, etc., can solve the problems of command aging, command suspension, bandwidth waste, etc., to increase the probability of fast hit, prevent command aging, and reduce bandwidth waste.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be described in further detail below in conjunction with the accompanying drawings.

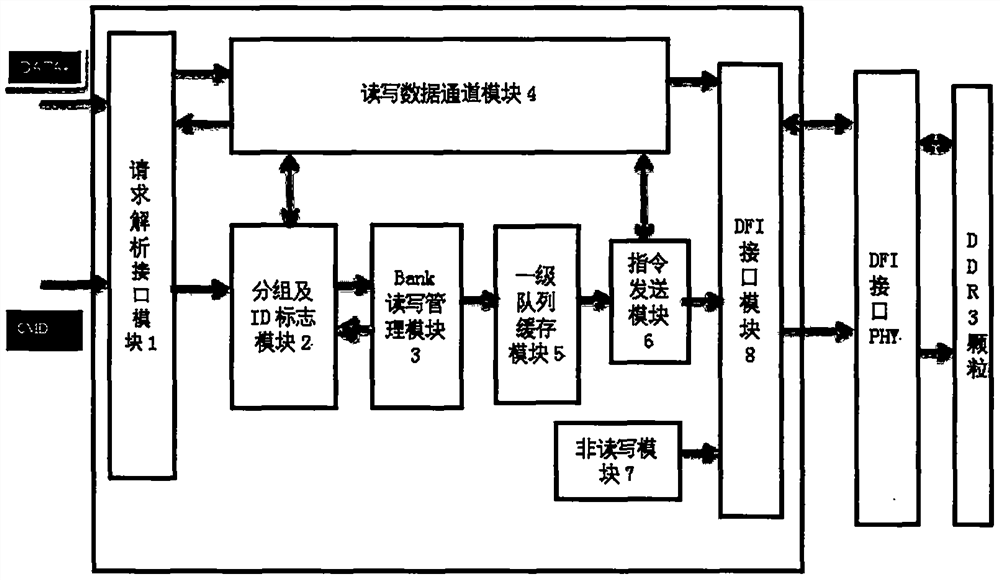

[0032] Such as figure 1 As shown, a reliable and efficient DDR3 controller based on the DFI standard includes a request parsing interface module 1, a packet and ID flag module 2, a Bank read and write management module 3, a read and write data channel module 4, and a first-level queue cache Module 5, instruction sending module 6, non-reading and writing module 7 and DFI interface module 8.

[0033]The request parsing interface module 1 is used to receive commands and data on the user bus; and split the commands and data requested by the user into DDR3 particles with a length that can be processed by a burst, and buffer the commands and data into FIFO asynchronously.

[0034] The grouping and ID mark module 2 is used to give the group order to the command after splitting according to the grouping strategy, to give the corresponding ID attribute to the read an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com