Mixed order finite element method and device for triangular prism mesh generation of integrated circuit

An integrated circuit and grid subdivision technology, applied in special data processing applications, image data processing, 3D modeling, etc., can solve problems such as low computational efficiency, low computational efficiency, and no implementation method for transition units

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

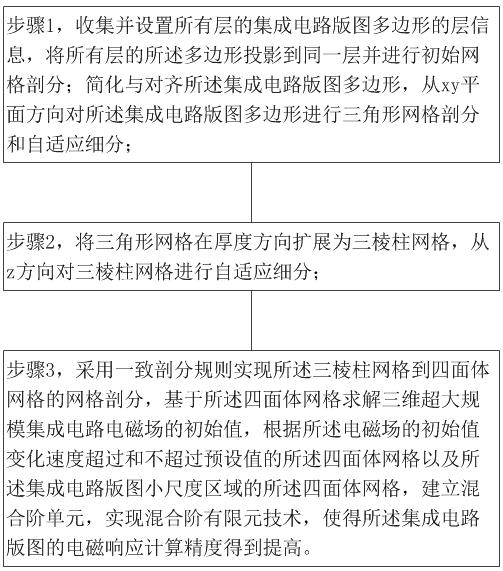

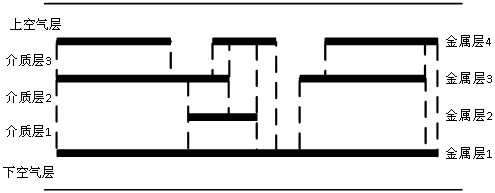

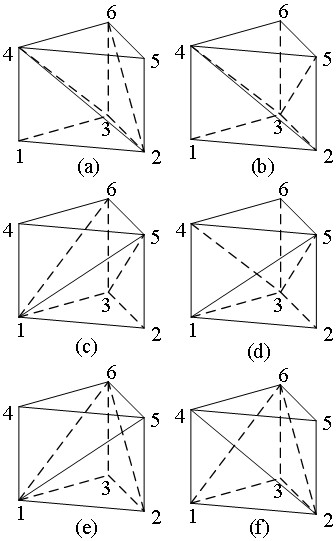

Method used

Image

Examples

Embodiment Construction

[0077] In order to make the objectives, technical solutions and advantages of the present invention clearer, the technical solutions in the embodiments of the present invention will be described in more detail below in conjunction with the drawings in the embodiments of the present invention.

[0078] It should be noted that: in the drawings, the same or similar symbols represent the same or similar elements or elements with the same or similar functions. The described embodiments are part of the embodiments of the present invention, but not all of the embodiments. In the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined with each other. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0079] In describing the present invention, it is to be understood that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More