Method for manufacturing semiconductor device using planarization technique

A technology for semiconductors and devices, applied in the field of manufacturing semiconductor devices, can solve the problems of transistor characteristics degradation, affecting the properties of diffusion layers, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The present invention will be described in detail below with reference to the accompanying drawings, wherein like components are indicated by the same or related reference numerals.

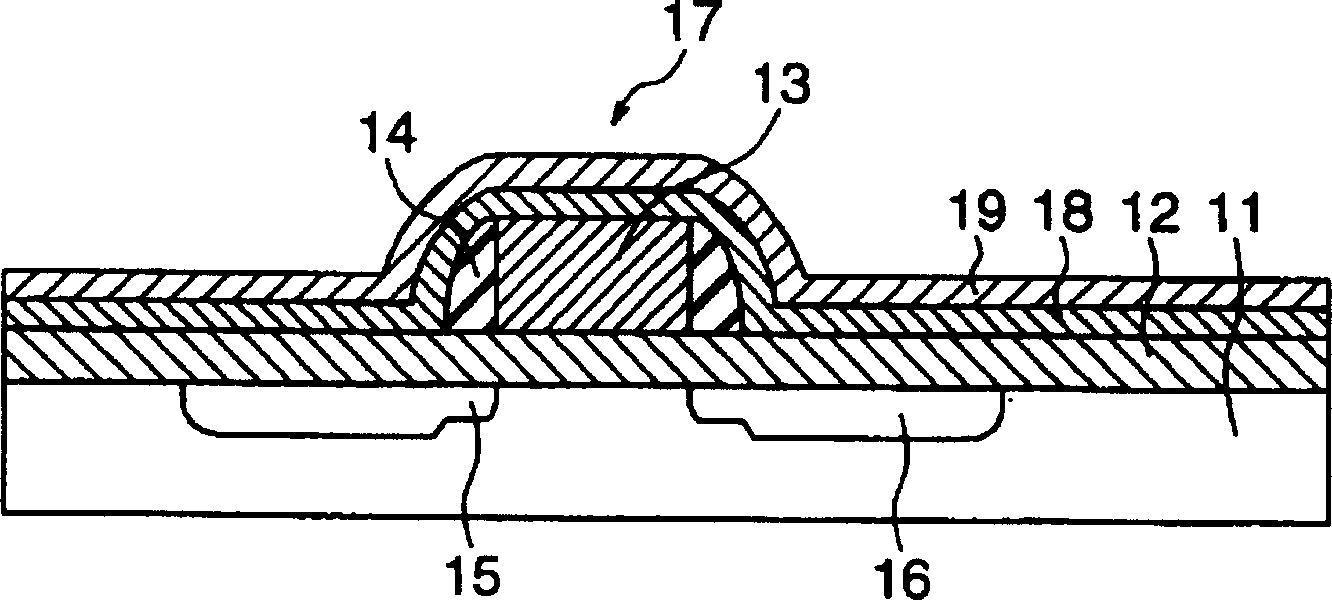

[0015] Figures 1A-1E A semiconductor device in various sequential manufacturing steps according to the first embodiment of the present invention is shown. see Figure 1A A MOSFET 17 having a gate insulating film 12 , a gate 13 connected to a sidewall film 14 , and a source / drain region 16 connected to a lightly doped drain (LDD) region 15 is formed on a silicon substrate 11 . Then, chemical vapor deposition (CVD) is performed in an atmospheric pressure atmosphere to form a silicon oxide film 18 thereon, followed by depositing a silicon nitride film 19 thereon, which serves to make the transistor 17 waterproof or protected from moisture. Floor. It is sufficient that the silicon nitride film 19 has a thickness of 50-200 angstroms.

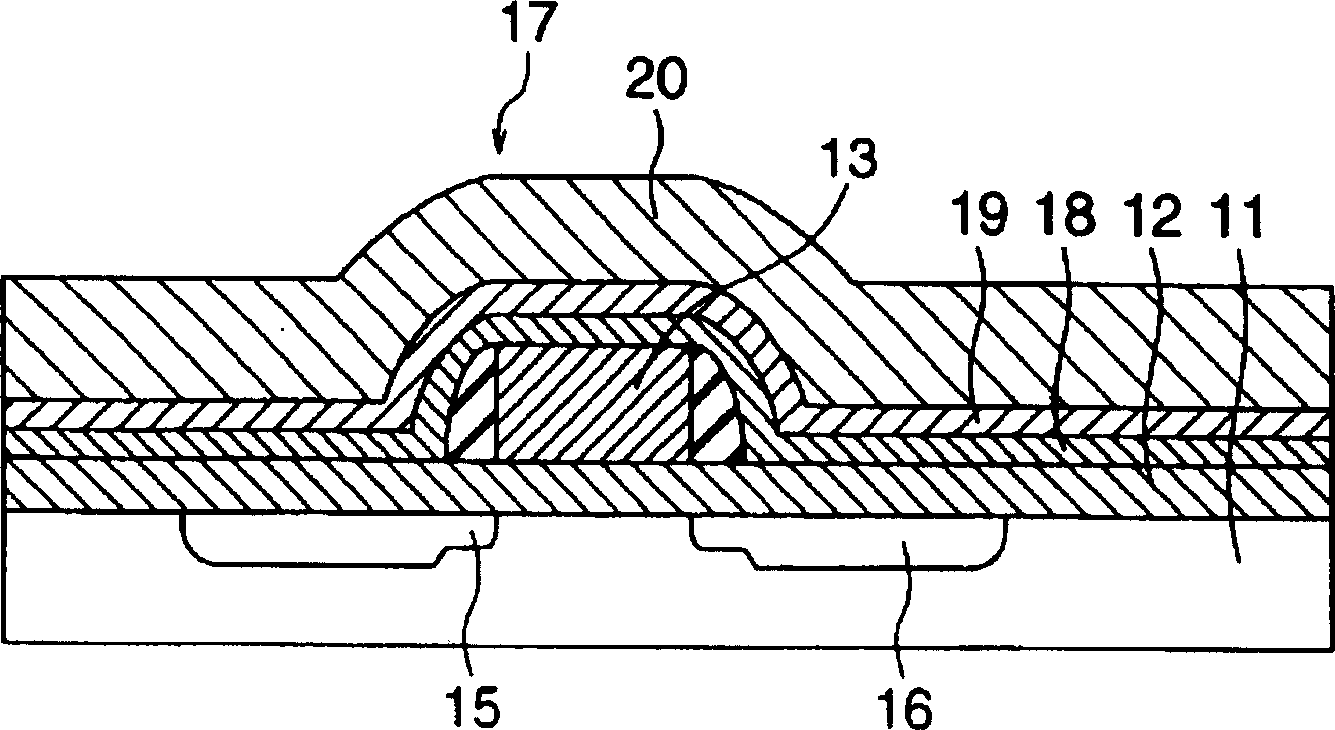

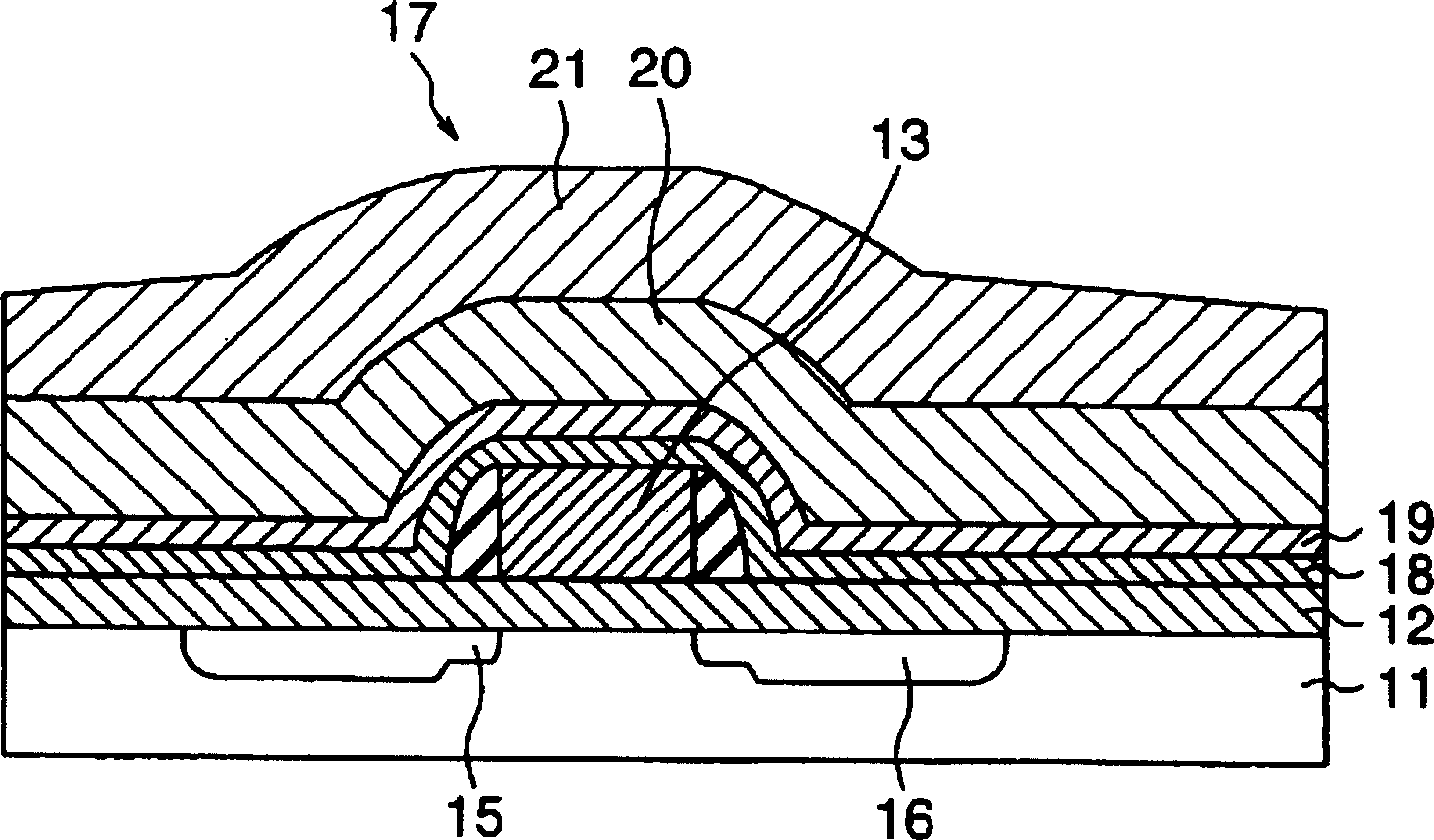

[0016] Then, on the silicon nitride film 19, a BPSG fil...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More