A method, device, CPU chip and server for reducing on-chip network power consumption

An on-chip network and power consumption technology, applied in the computer field, can solve problems such as long time, achieve the effect of optimizing energy efficiency ratio, reducing invalid power consumption, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0113] The embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0114] It should be understood that the described embodiments are only some, but not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

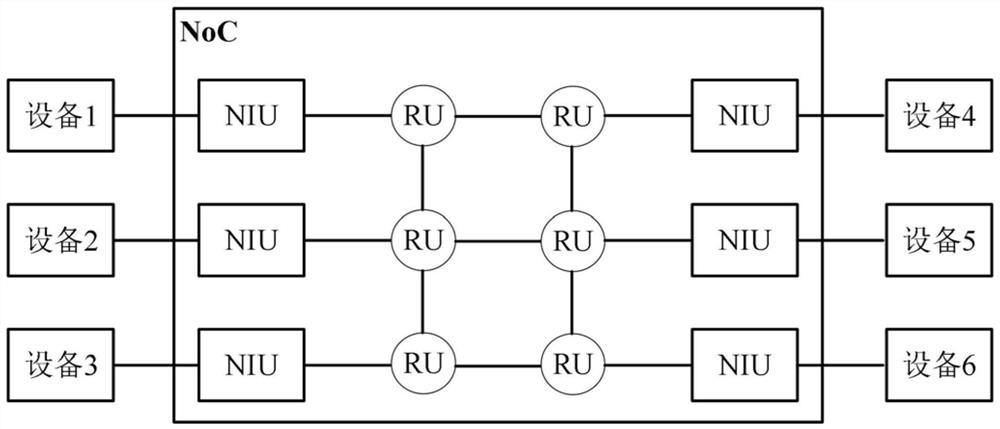

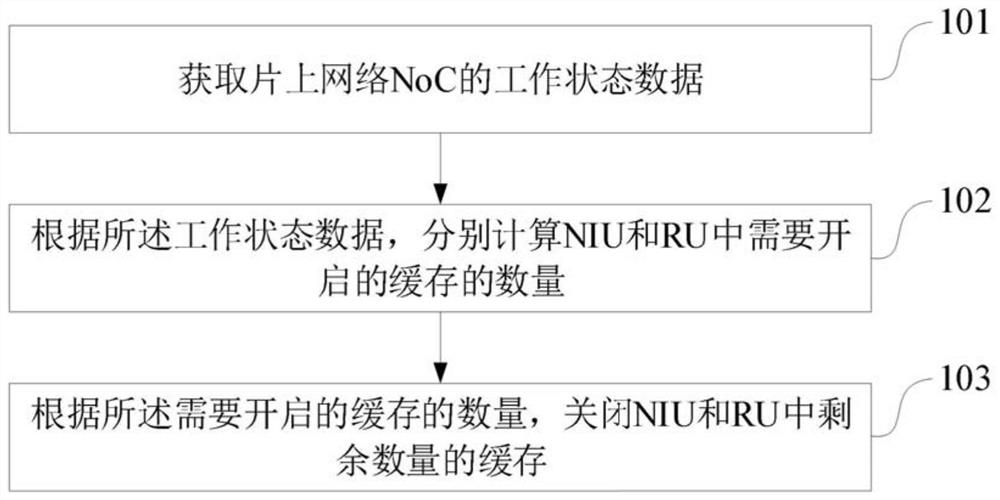

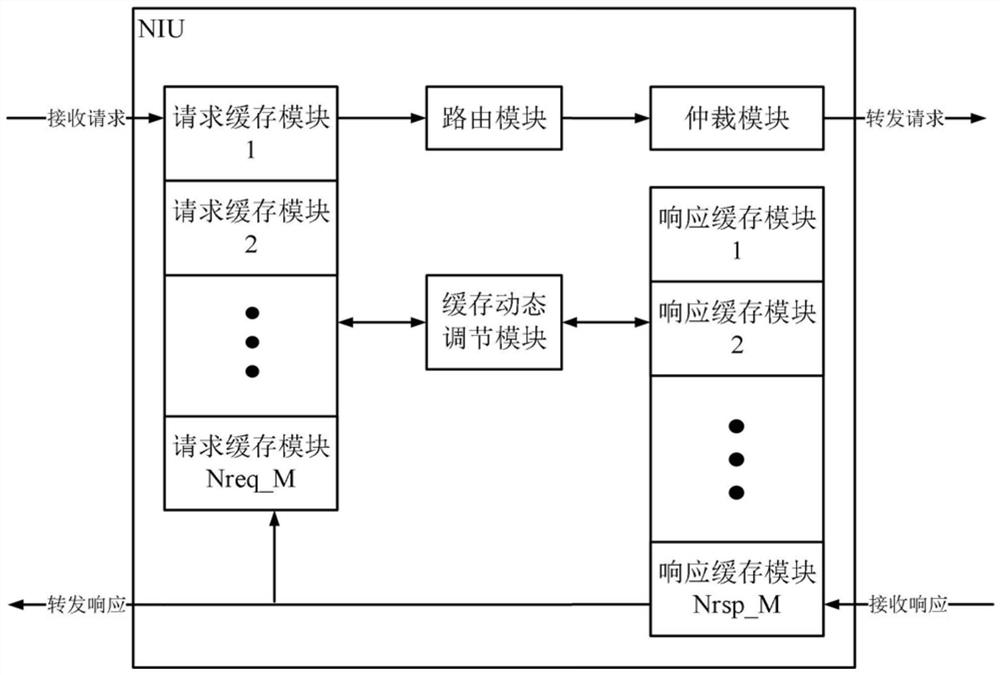

[0115] In one aspect, an embodiment of the present invention provides a method for reducing power consumption of an on-chip network. The on-chip network NoC includes at least two network interface units (NIUs) and at least two routing units (RUs), and the NIUs and RUs each have at least two caches. , the caches in the NIU and RU are independently controlled, such as figure 2 As shown, the method of this embodiment may include:

[0116] Step 101: Obtain the working state data of the NoC, the working state data incl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More