Multi-chip package structure having chip interconnection bridge which provides power connections between chip and package substrate

A packaging substrate and packaging structure technology, applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of increasing the voltage drop of the packaging substrate and IR heating

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

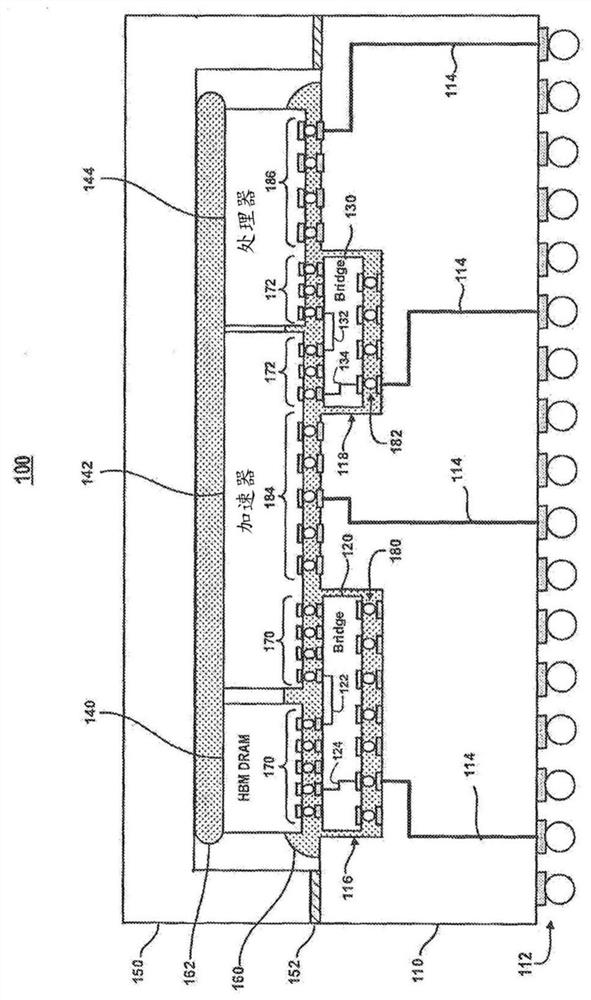

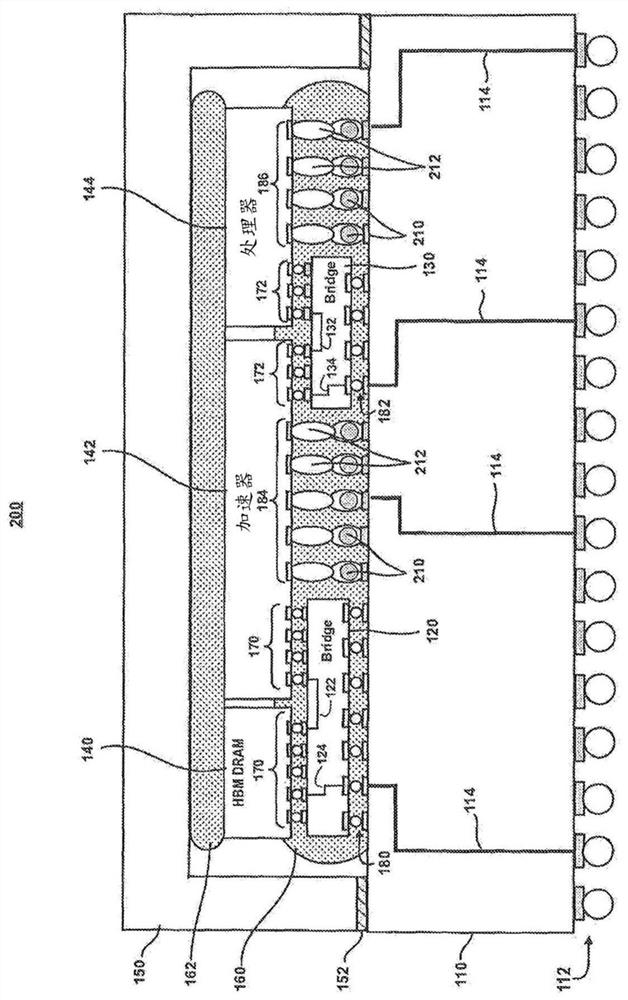

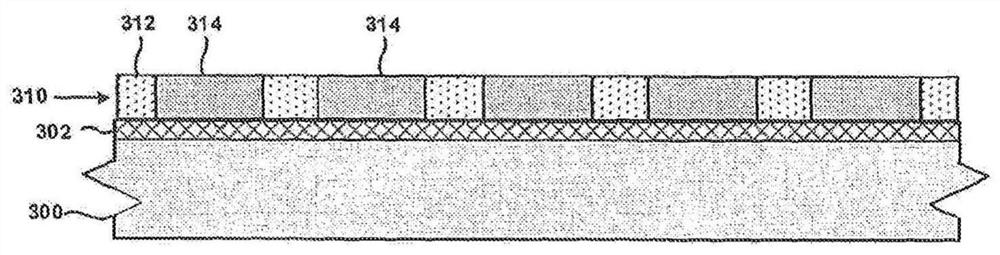

[0027] An embodiment of the present invention will now be discussed in more detail with respect to the multi-chip package structure, which includes a chip interconnect device, which is designed to be used between adjacent chips in the package structure. High I / O interconnect density is provided, and a vertical power distribution trace is provided by the chip's interconnect device to supply a power source (and ground) from the package substrate to the chip to the chip interconnect device. It should be understood that the individual layers, structures, and regions shown in the drawings are illustrative diagrams that are not drawn. Furthermore, in order to facilitate explanation, one or more layers, structures, and regions that are typically used to form a type of semiconductor device or structure may not be explicitly shown in the given drawings. This does not mean any layers, structures, and regions that are not explicitly shown from the actual semiconductor structure.

[0028]Fu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More