IP core for satellite-borne SRAM type FPGA configuration and refresh control

A spaceborne and configuration file technology, applied in the integration of aerospace electronics and aviation, can solve the problems of poor scalability and achieve the effect of simple implementation, strong portability and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] The technical solutions of the present invention will be described in detail below in conjunction with the drawings and embodiments.

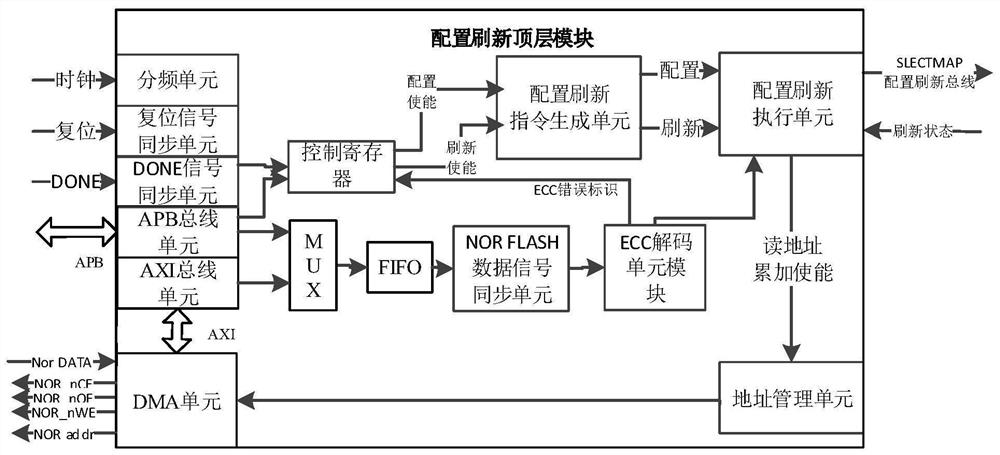

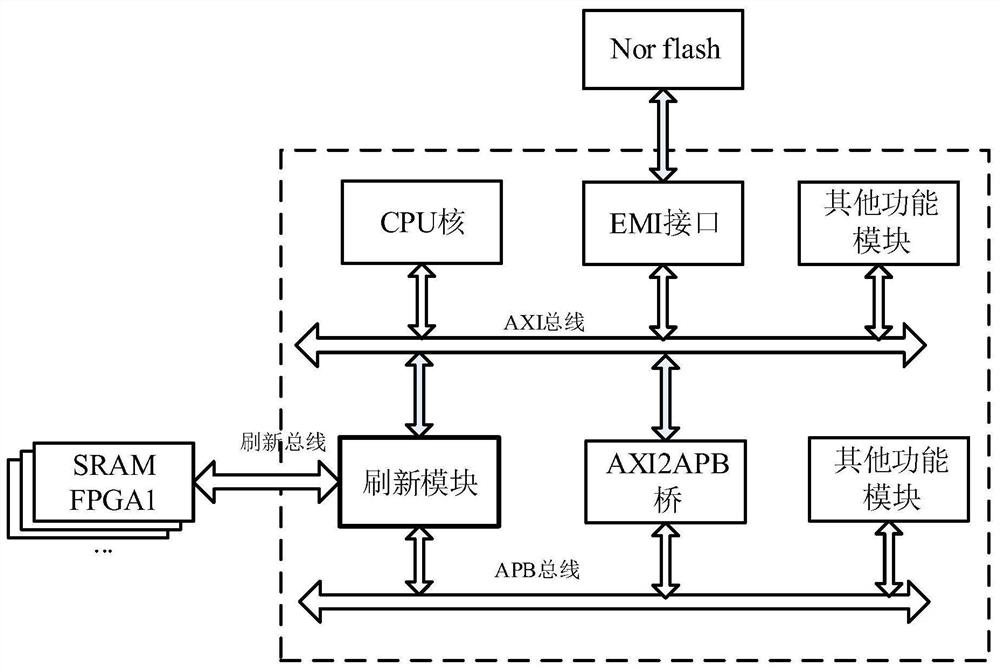

[0054] Such as figure 2 As shown, this application proposes an IP core for on-board SRAM FPGA configuration and refresh control, which is used to read FPGA configuration files under the control of an external processor, and perform on-orbit configuration and update of single or multiple SRAM FPGAs. refresh control,

[0055] 1) The IP core is connected to the external processor through the APB bus to realize the control of the internal registers of the IP core;

[0056] 2) The IP core accesses the external memory through the AXI bus and DMA or through the APB bus to read the configuration file;

[0057] 3) The IP core implements the configuration and refresh of multiple external SRAM FPGAs through the selectMAP bus interface;

[0058] 4) The software can be configured, the hardware can be expanded, and the portability is strong, and i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com