Large-scale complex layout resistance extraction acceleration method

A large-scale and complex technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of time overhead, long pattern matching time, long extraction time of parasitic resistance, etc. The effect of extracting accuracy and improving computational efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

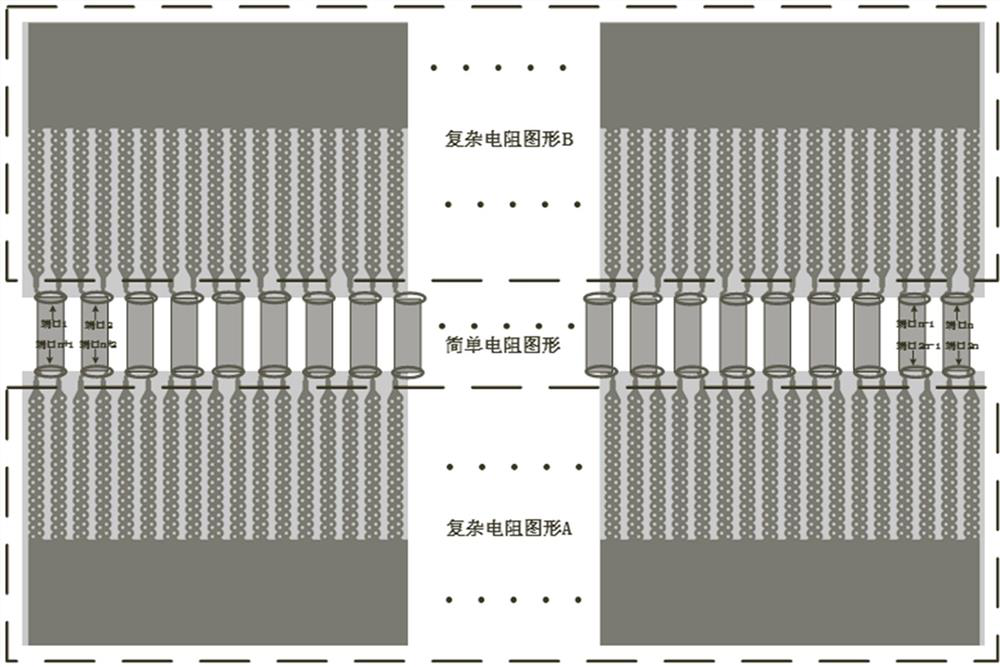

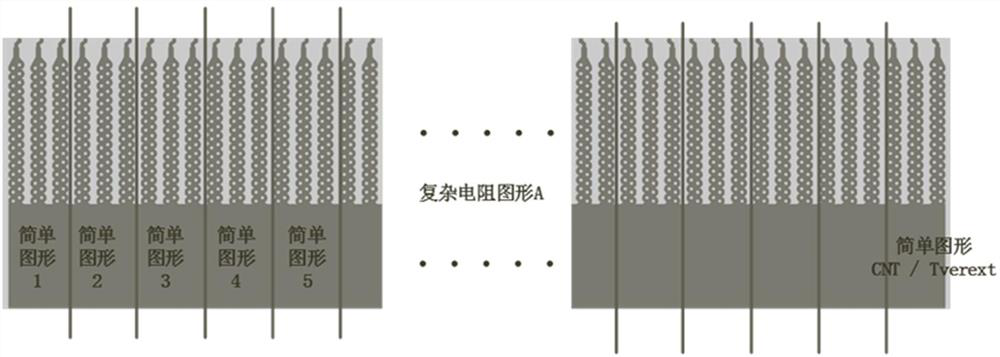

[0035] In the embodiment of the present invention, figure 2 Connect schematics for complex resistor layouts, such as figure 2 As shown, in the complex graphics that need to extract resistance, there are 2n port graphics or blocking graphics that need to be extracted. Complex graphics A and complex graphics B are polygons with a large number of vertices. There are few simple polygonal graphics, complex graphics and simple graphics are connected through port graphics (or blocking graphics), and the port graphics (or blocking graphics) can be rectangles or line segments with port attributes.

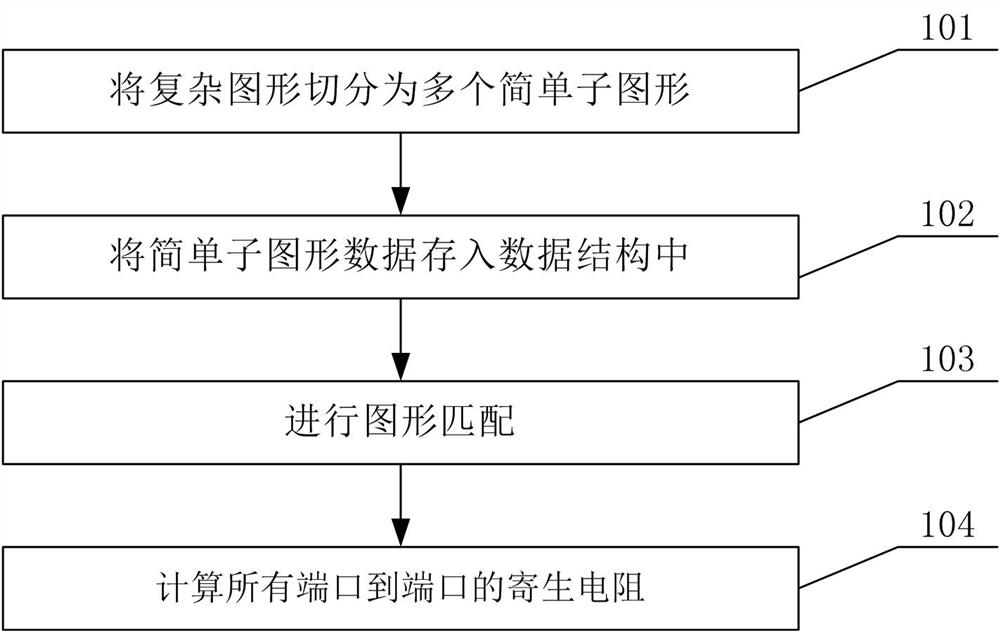

[0036] figure 1 It is a flow chart of the method for accelerating the ex...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More