Three-dimensional memory structure and preparation method thereof

A memory, three-dimensional technology, applied in the direction of electric solid devices, semiconductor devices, electrical components, etc., can solve the problems of contact, affecting the reliability of the device, and the problem of step support in the step area, and achieve the effect of strengthening the structure and improving the collapse phenomenon.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

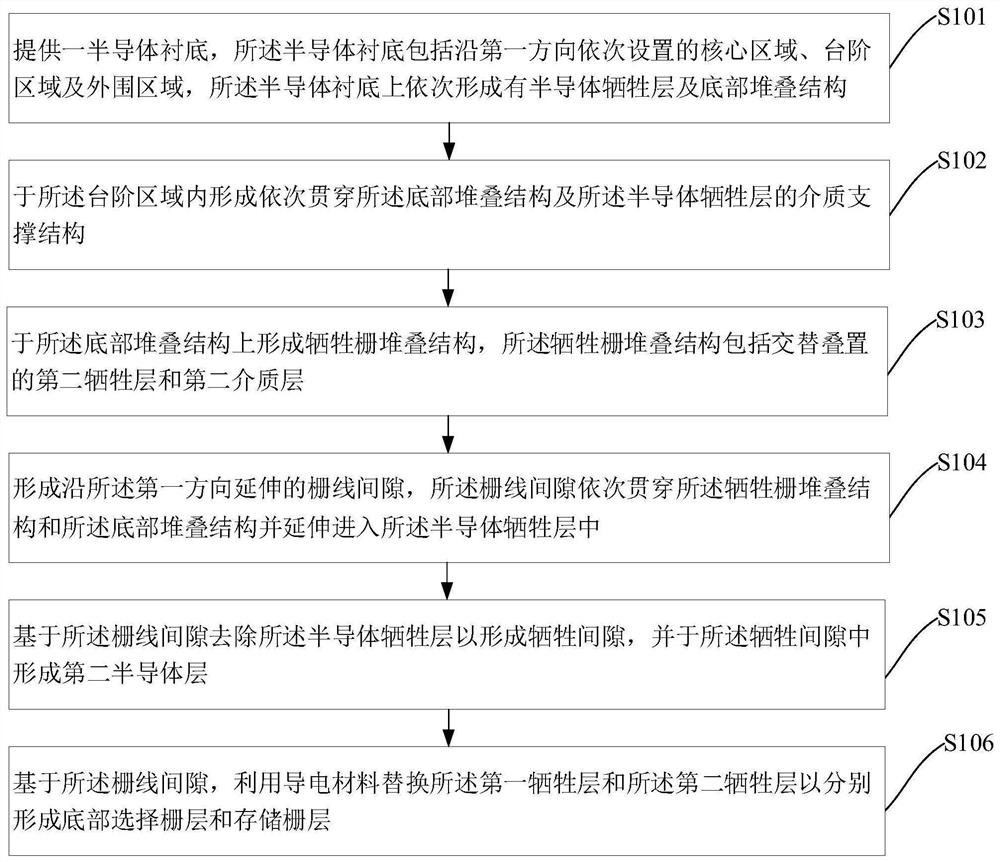

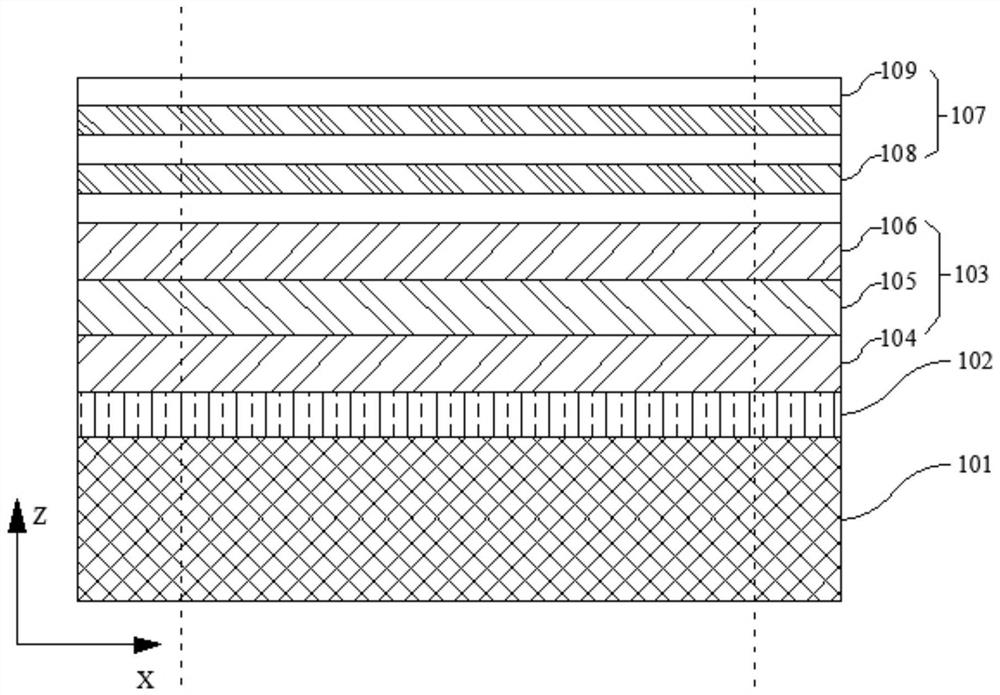

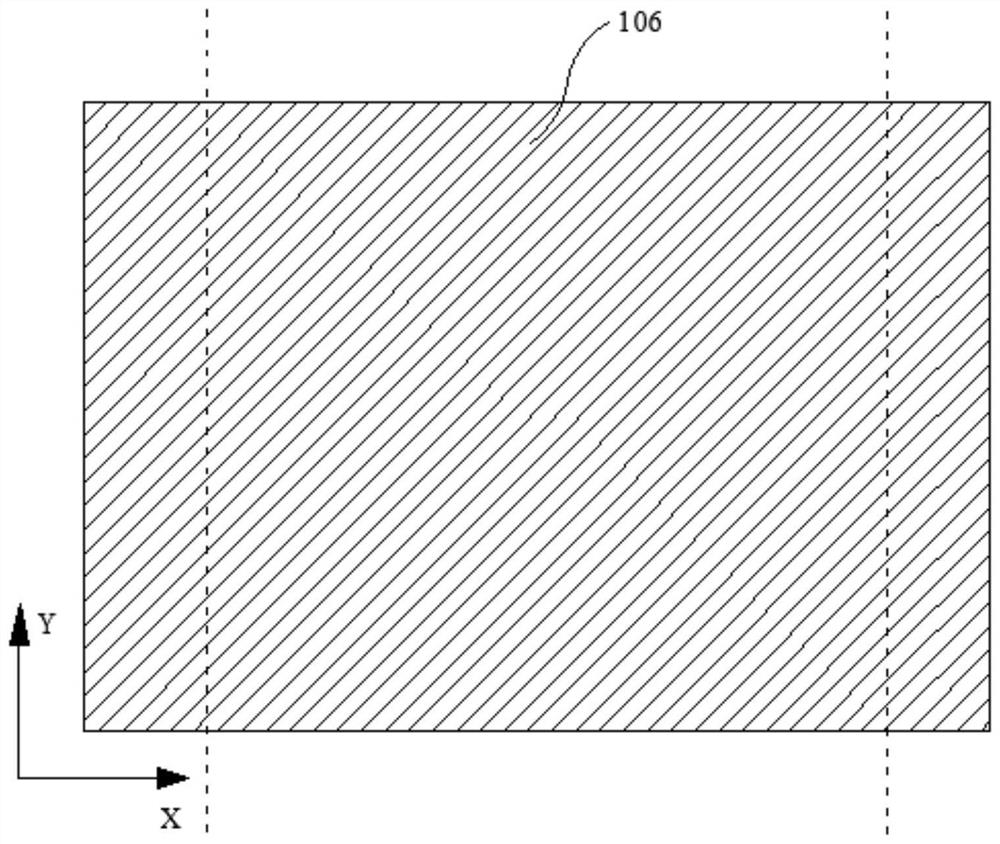

[0115] This embodiment introduces a method for preparing a three-dimensional memory structure, wherein, figure 1 A schematic flow chart showing a method for preparing a three-dimensional memory structure in this embodiment, figure 2 , 4 , 6 and 8 respectively show the cross-sectional schematic diagrams corresponding to different process steps in the preparation process of the three-dimensional memory structure, image 3 , 5 , 7 and 9 show the corresponding figure 2 , 4 The top view along the top surface of the third semiconductor layer 106 in the devices in the structures of , 6 and 8 .

[0116] The method for preparing the three-dimensional memory structure of this embodiment will be described in detail below in conjunction with the schematic diagrams corresponding to each step.

[0117] First, see Figure 1-3 , execute step S101: provide a semiconductor substrate 101, the semiconductor substrate 101 includes a core area, a step area and a peripheral area (correspondi...

Embodiment 2

[0134] This embodiment introduces another method for preparing a three-dimensional memory structure, wherein, figure 1 A schematic flow chart showing a method for preparing a three-dimensional memory structure in this embodiment, Figure 10 , 12 , 14 and 16 respectively show cross-sectional schematic diagrams corresponding to different process steps in the preparation process of the three-dimensional memory structure, Figure 11 , 13 , 15 and 17 respectively show the corresponding Figure 10 , 12 , 14 and 16 are top views along the top surface of the third semiconductor layer 106 .

[0135] The difference between this embodiment and Embodiment 1 is that the shape of the dielectric support structure 111 in step S102 is different. In this embodiment, the dielectric support structure 111 is an annular dielectric support structure, while in the first embodiment It is a solid dielectric support structure 111, and other structures are basically the same, so they will not be des...

Embodiment 3

[0139] This embodiment introduces the preparation method of the third three-dimensional memory structure. The difference between this embodiment and the first embodiment lies in that the shape of the peripheral filling structure 113 in step S102 is different, and other structures are basically the same, so details are not repeated here.

[0140] Specifically, see Figure 18 , in this embodiment, the peripheral groove is an annular groove, the peripheral filling structure 113 formed in the peripheral groove is an annular peripheral filling structure, and the annular peripheral filling structure is a rectangular annular structure , of course it can also be a circular ring, an elliptical ring or other closed ring structures. Since the first semiconductor layer 104 , the semiconductor sacrificial layer 105 , and the third semiconductor layer 106 inside the annular peripheral groove are retained during etching of the peripheral groove, this can effectively reduce the internal stre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com