Method for monitoring wafer in semiconductor manufacturing, and mask

A technology of semiconductor and mask plate, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device testing/measurement, photo-plate making process of patterned surface, etc. It can solve the problems of inconsistent data specifications, low efficiency, and low work efficiency, etc. problems, achieve data standardization, high analysis efficiency, and low workload

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

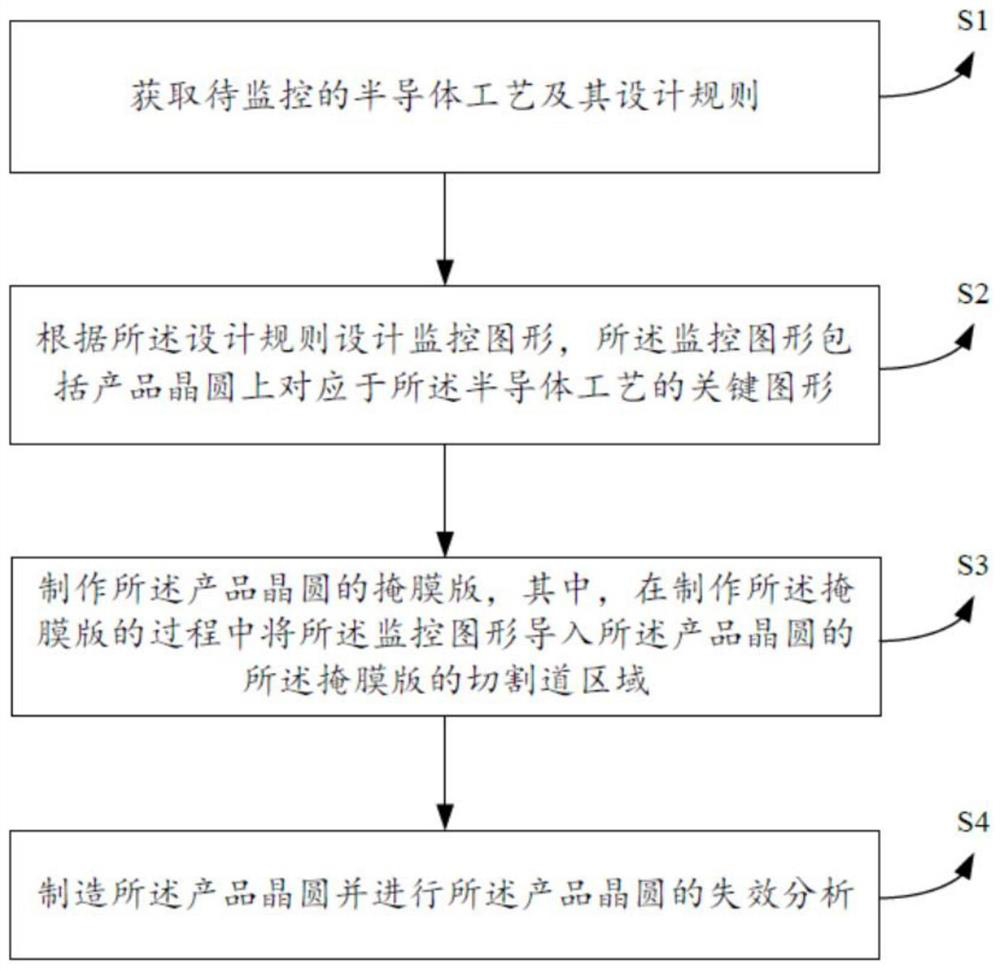

[0035] In order to solve the problems in the prior art, the invention provides a method for monitoring wafers in semiconductor manufacturing, including:

[0036] Obtain the semiconductor process to be monitored and its design rules;

[0037] Designing monitoring graphics according to the design rules, the monitoring graphics include key graphics corresponding to the semiconductor process on the product wafer;

[0038] Making a reticle of the product wafer, wherein, during the process of making the reticle, introducing the monitoring pattern into the dicing lane area of the reticle of the product wafer;

[0039] Fabricating the product wafer and performing a failure analysis of the product wafer.

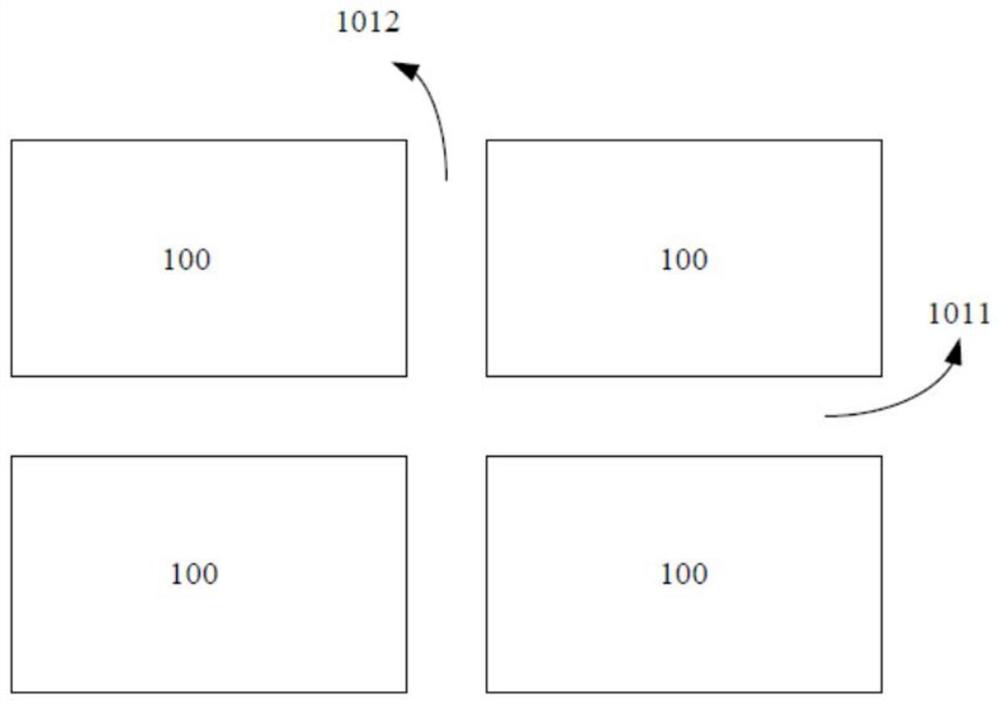

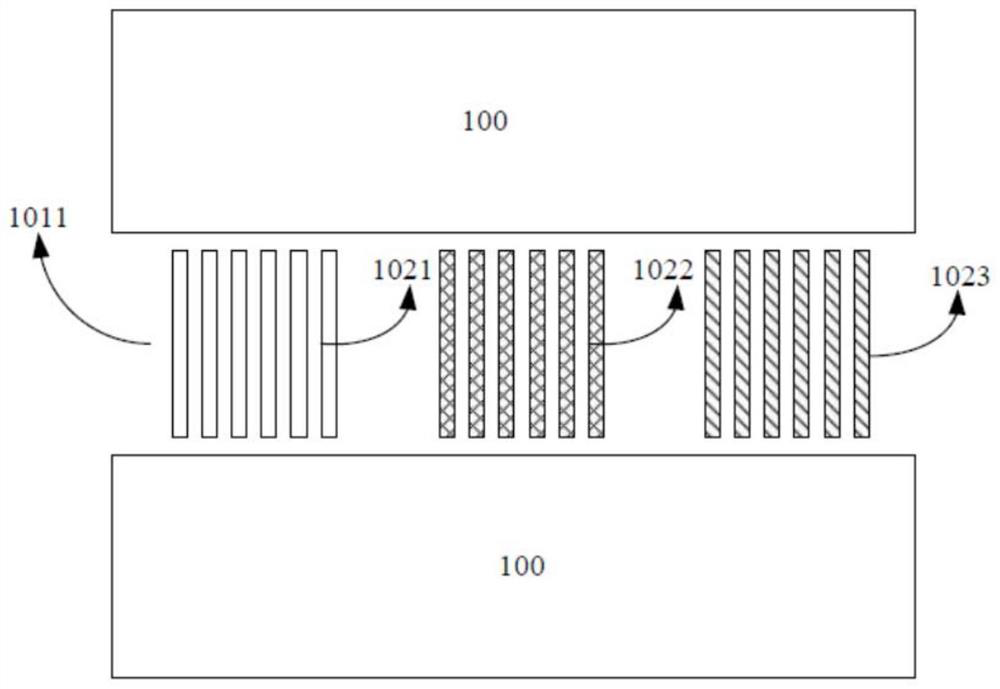

[0040] Refer below Figure 1-Figure 4 A method for monitoring wafers in semiconductor manufacturing according to the present invention is exemplified, wherein figure 1 It is a flowchart of a method for monitoring wafers in semiconductor manufacturing according to an embodiment o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More