Chip peripheral anti-fuse pre-trimming circuit and trimming method thereof

An anti-fuse and pre-repair technology, applied in logic circuits, adjusting electrical variables, electrical components, etc., can solve the problems of long production test time and low efficiency, achieve improved repair efficiency, good process compatibility, and reduce production The effect of testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] The present invention will be described in further detail below in conjunction with accompanying drawing:

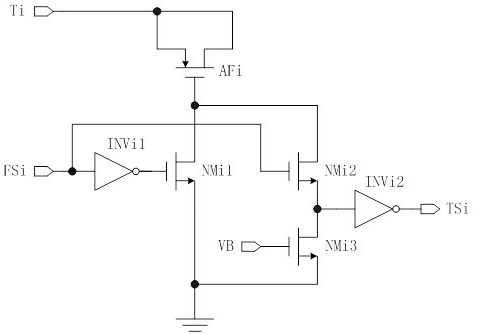

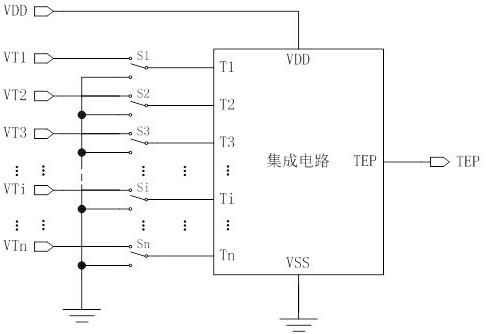

[0056] image 3 An embodiment of the chip peripheral pre-trimming circuit of the present invention is shown.

[0057] see image 3 As shown, the anti-fuse pre-trimming circuit on the periphery of the chip includes an integrated circuit, and the integrated circuit has an n-bit anti-fuse trimming circuit and a first melting voltage Ti (i=1,2,3,... ,n) one-to-one correspondence, the switches Si (i=1,2,3,…,n) are respectively connected to the pins of the first fusing voltage Ti (i=1,2,3,…,n) of the integrated circuit above; among them, VDD is the power supply voltage pin of the integrated circuit; VSS is the ground pin of the integrated circuit; TEP is the output pin of the modified electric parameter. The switch Si (i=1, 2, 3,..., n) can be a MOSFET switch tube, a BJT switch tube, or a switching device such as a relay, or a combination of these switching devices. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More