A one-to-many transmission method based on mipi DSI bus

A multi-transmission, one-to-one technology, applied in the direction of cathode ray tube indicators, static indicators, instruments, etc., to achieve the effect of optimizing layout and avoiding crossover

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

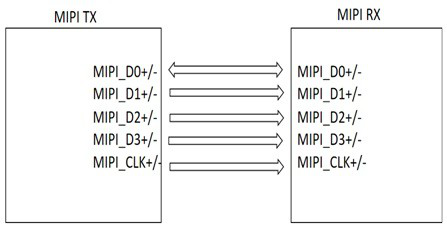

[0029] The present invention provides an architecture-many transmission method MIPI DSI bus, such as attachment image 3 Indicated. By the sender Mobile Industry Processor Interface MIPI i.e., the TX transmits a control end-to-many active alignment control, the Controller transmitting end is located in the TX MIPI, the TX transmitting side MIPI DSWAP [1: 0] and the first receiving terminal and MIPI MIPI RXl DSWAP second receiving terminal RX2 [1: 0] is connected to the terminal while controlling transmission MIPI TX MIPI RX1 receiving a first end and a second level status DSWAP end MIPI RX2 received by the controller may be sent by the selected terminal MIPI TX when a certain time point and the first receiving terminal MIPIRX1 MIPI RX2 or the second end of the communication receiver, selecting a first receiving terminal or the MIPI RX1 MIPI RX2 second receiving terminal in communication, the remaining unselected communication MIPI RX to the receiving end a failed state.

[0030] Wh...

Embodiment 2

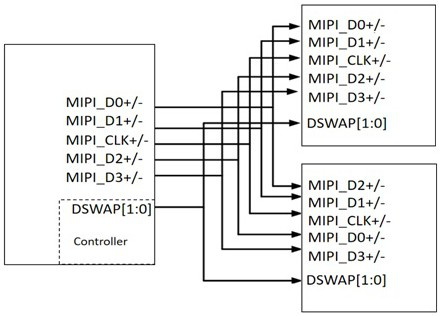

[0034] Further, the present invention also proposes a multi-transmission method of architecture in the MIPI DSI bus, Figure 4 As shown, the RX side actively controls a pair of multi-line lines.

[0035] In the present embodiment, the controller controller is located at the MIPI Rx receiver, which can be implemented in the technical solution of the present invention on the MIPI RXN (N Nature). Figure 4 Only two MIPI RX receiving ends are shown for understanding the present invention.

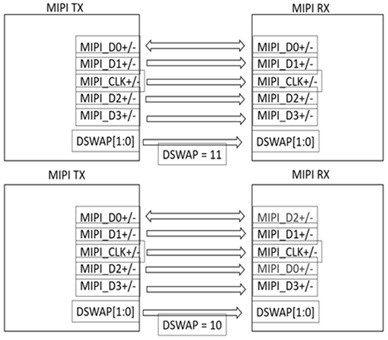

[0036] Append Figure 4 As shown, the controller Controller is located at the MIPI Rx2 second receiving end, and the DSWAP [1: 0] of the MIPI Rx2 second receiving end is connected to DSWAP [1: 0] of the MIPI Rx1 first receiving end, when MIPI RX2 second receiving end When the MIPI RX1 first receiving end is required, the controller controller sets DSWAP [1: 0] = 11 of the MIPI RX1 first receiving end, at which point the MIPI Rx1 first receiving end is at the same time in the working state.

[0037] Wh...

Embodiment 3

[0040] Further, the present invention also proposes a multi-transmission method of architecture in the MIPI DSI bus, Figure 5 As shown, the external controller actively controls a pair of multi-circular lines.

[0041] The MIPI RX1 first receiving end, the MIPI Rx2 second receiving end is connected by an external controller, and the DSWAP foot bit signal is switched, determine the control of the MIPI RX1 first receiving end, the MIPI Rx2 second receiving end BUS.

[0042] When the MIPI Rx1 first receiving end and the MIPI RX2 second receiving end are required to operate at the same time, the controller sets the MIPI Rx1 first receiving end DSWAP [1: 0] = 11, MIPI RX2 second receiving end DSWAP [ 1: 0] = 11.

[0043] When the MIPI RX1 first receiving end is required, the MIPI Rx2 second receiving end is felt, the controller sets the MIPI Rx1 first receiving end DSWAP [1: 0] = 11, MIPI RX2 second receiving end DSWAP [ 1: 0] = 10.

[0044] When the MIPI RX1 first receiving end is inv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More