A structure and production method of reducing heterogeneous knot dual-crystal tube B-C knotted capacitance

A technology of heterojunction bipolar and manufacturing method, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of the current gain cut-off frequency, the highest oscillation frequency, the increase of the base resistance Rb, etc. The effect of the highest oscillation frequency and strong size controllability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

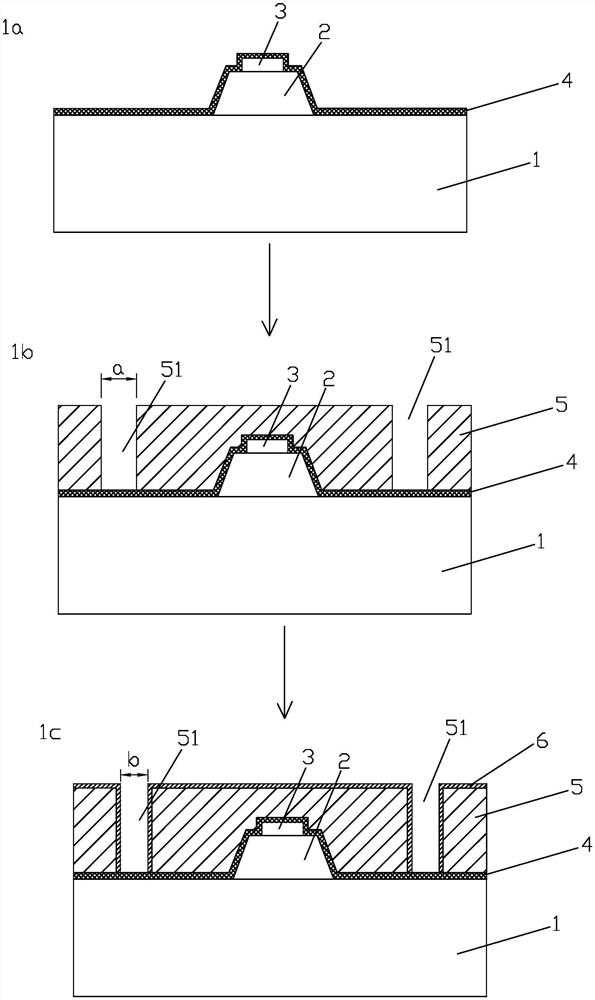

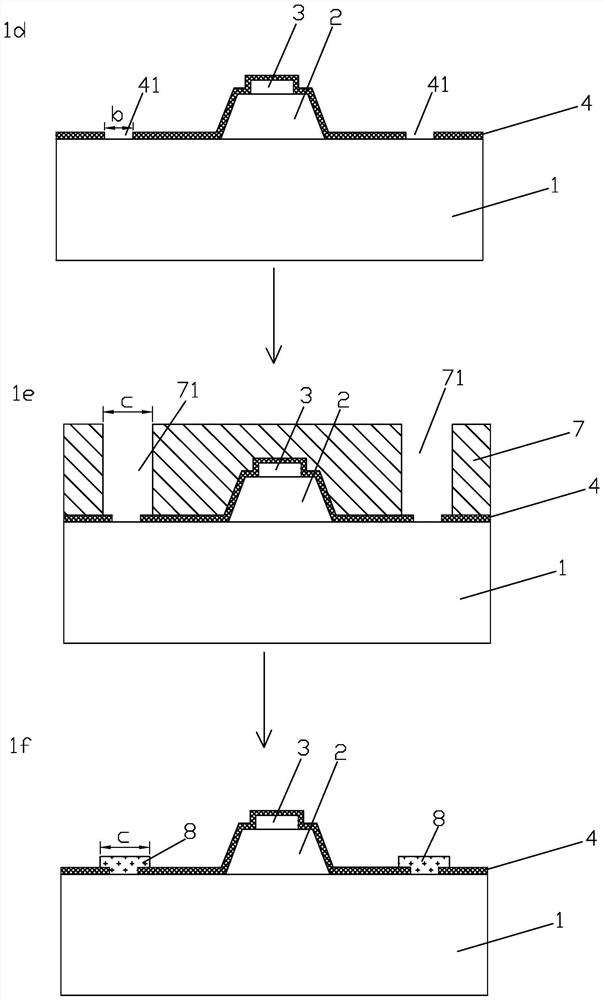

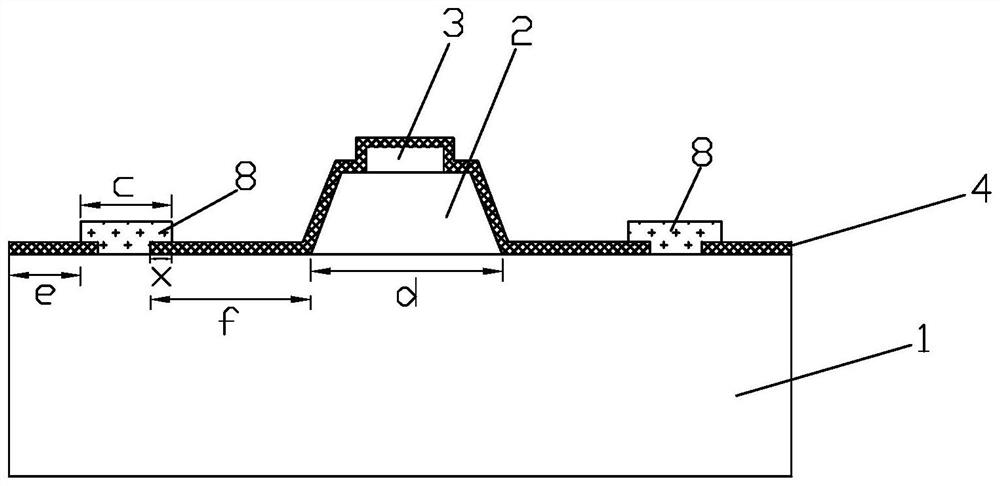

[0029] refer to figure 1 The process flow chart of , taking the formation of a base metal with a bottom line width of about 0.25μm as an example, a manufacturing method for reducing the b-c junction capacitance of a heterojunction bipolar transistor is specifically described:

[0030] First, a chip structure that has been partially fabricated is provided, including an epitaxial layer 1 , an emitter structure (emitter mesa 2 and an emitter metal 3 ) and a passivation layer 4 . The process of the above structure refers to the known process, wherein after the emitter metal 3 is fabricated, a layer of 20-80 nm SiN or SO is deposited by PVCVD 2 As the passivation layer 4, the obtained structure is as figure 1 as shown in a;

[0031] Then, a first photoresist 5 with a thickness of 0.5-1.0 μm is coated on the chip structure, and the first photoresist 5 is a positive photoresist AR80 (from Tokyo Yinghua), which is exposed by an I-line lithography machine. TMAH (concentration 2.38%)...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More