A high-performance high-speed input buffer circuit

An input buffer circuit, high-speed technology, applied in the direction of logic circuit connection/interface layout, etc., can solve the problem that the input buffer circuit is difficult to meet, and achieve the effects of increasing bandwidth, increasing gain, and increasing flipping speed.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The specific embodiments of the present invention will be further described below in conjunction with the accompanying drawings.

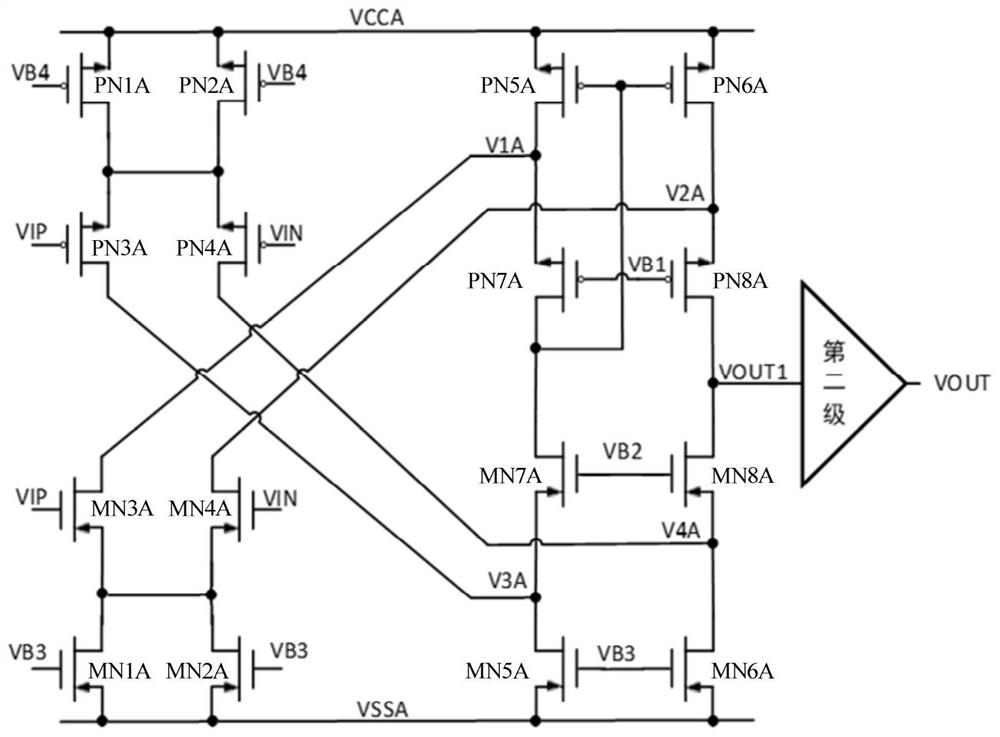

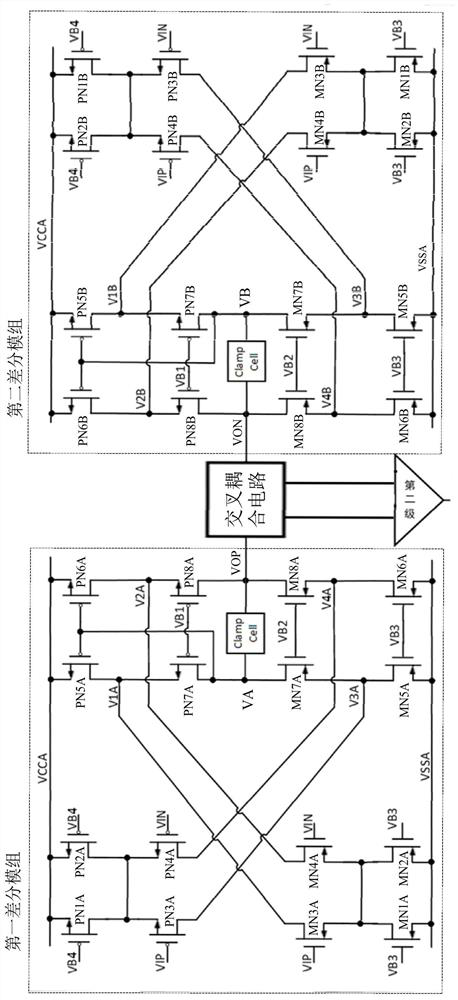

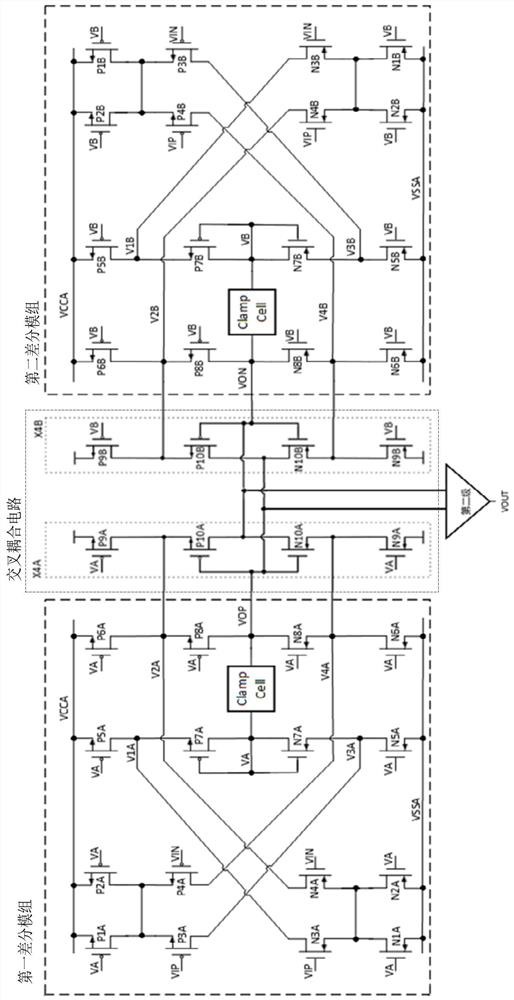

[0042] This application discloses a high-performance high-speed input buffer circuit, please refer to figure 2 , the high-speed input buffer circuit includes a first differential module, a second differential module and a cross-coupling circuit, the first differential module and the second differential module have the same structure, and each differential module includes a first differential amplifier circuit , the second differential amplifier circuit and the output module, wherein the first differential amplifier circuit is connected to the analog power supply VCCA and the two output terminals V1A and V2A are connected to the output module, the second differential amplifier circuit is connected to the analog ground VSSA and the two output terminals V3A and V4A Connect to output module. A pair of differential input signals VIN and VIP wit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More