FPGA (Field Programmable Gate Array)-based configurable CNN (Convolutional Neural Network) multiplication accumulator supporting 8-bit and 16-bit data

A multiplication and accumulation, data technology, applied in the field of image recognition, can solve the problems of high cost, high design threshold, and large resource consumption, so as to reduce the pressure of storage, reduce complexity, and speed up deployment.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

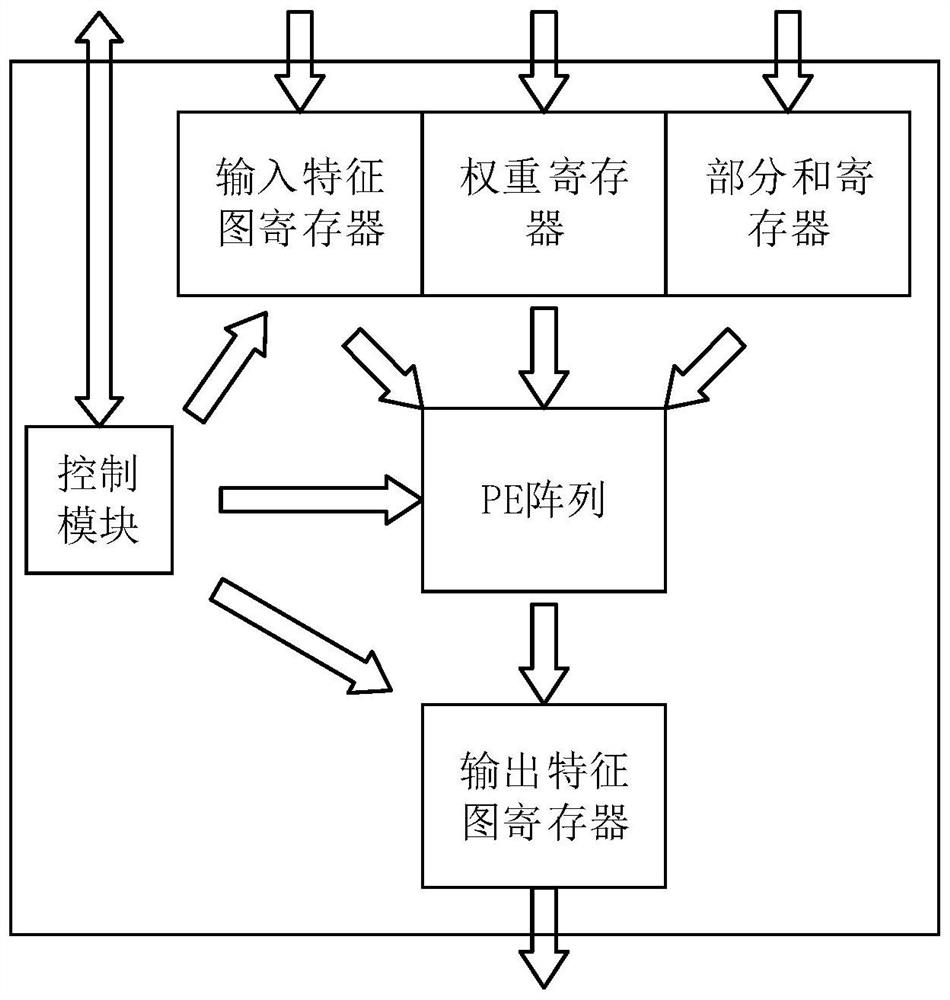

[0033] Such as figure 1As shown, the present invention provides a configurable CNN multiplication accumulator based on FPGA to support 8bit and 16bit data bit width, including control module, input feature map register, weight register, partial sum register, PE array and output feature map register, where:

[0034] The control module is used to control the timing of the entire convolution calculation; after receiving the start signal, the control module first generates the enable signal and the address of the data from the external storage according to the convolution configuration signal, and inputs the feature map, weight And part of the sum is read in parallel, so three read enable signals and corresponding three address signals are generated; when the input feature map is read, the convolution calculation starts, and the control module controls the PE array to start calculating the volume In the process of convolution calculation, the control module generates a moving sig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com