Clock generation circuit and semiconductor apparatus using the clock generation circuit

一种时钟生成电路、时钟的技术,应用在电气元件、功率的自动控制、电数字数据处理等方向,能够解决时钟生成电路需要大量功率、不符合半导体装置低功率等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] Hereinafter, the embodiments are described with reference to the drawings.

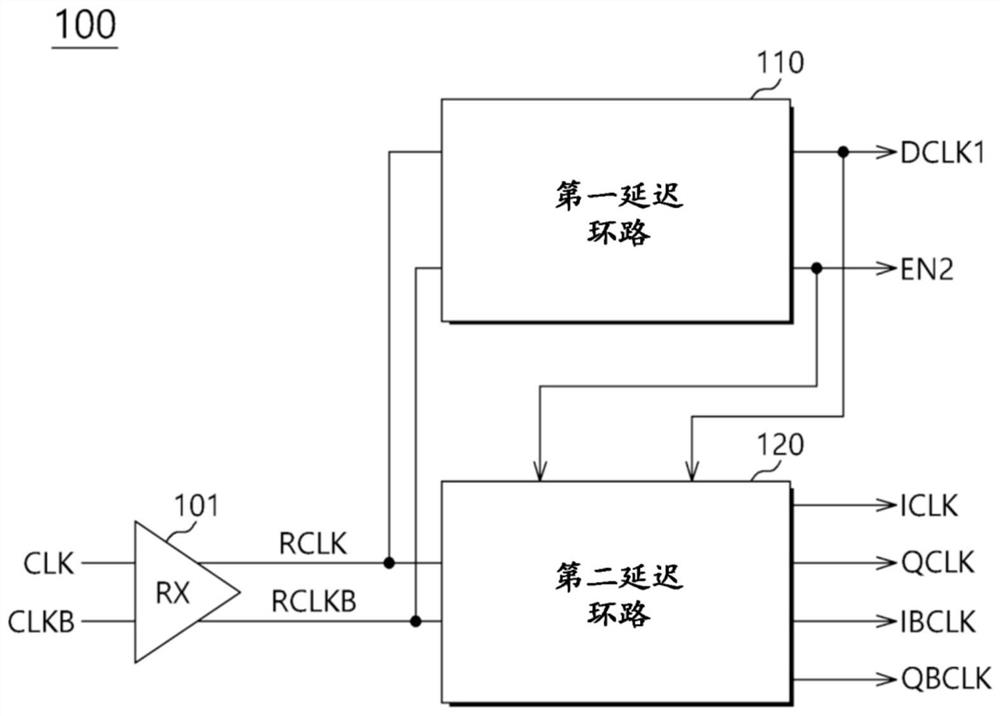

[0027] figure 1 is a diagram illustrating the configuration of the clock generation circuit 100 according to the embodiment. refer to figure 1 , the clock generating circuit 100 can generate a plurality of output clock signals by receiving the clock signals CLK and CLKB. The clock generation circuit 100 may include at least two delay loops. At least two delay loops may have different characteristics. At least two delay loops can generate output signals with different characteristics by respectively delaying the received clock signal. One delay loop may consume less power than another delay loop in order to delay the clock signal. Another delay loop may consume more power than one delay loop in order to delay the clock signal. However, another delay loop may generate an output clock signal with higher performance than one delay loop, and that output clock signal has an accurate phase and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More