Method for reconstructing parallel substructure of circuit

A technology of parallel sub-structures and circuits, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve problems such as limiting the degree of circuit reduction, and achieve the effect of simple process and favorable realization.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

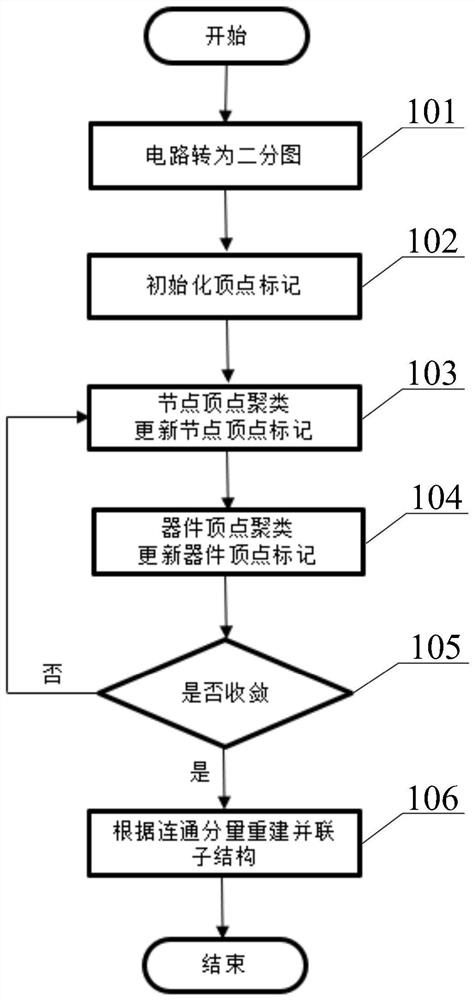

[0036] figure 1 It is a flow chart of the method for reconstructing the circuit parallel substructure according to the present invention, which will be referred to below figure 1 , to describe in detail the method for reconstructing the circuit parallel substructure of the present invention.

[0037] First, in step 101, the circuit is converted into a bipartite graph.

[0038] At step 102, vertex labels are initialized.

[0039] Preferably, for the device vertices, the graph vertices corresponding to the two devices have the same label, if and only if the two devices are of the same type (such as belonging to linear resistors, or mosfets belonging to the same mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More