Packaging mechanism and packaging method for semiconductor substrate

A packaging method and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of relaxation, the substrate cannot be adjusted, the semiconductor substrate is loose, etc., and achieves high assembly convenience. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

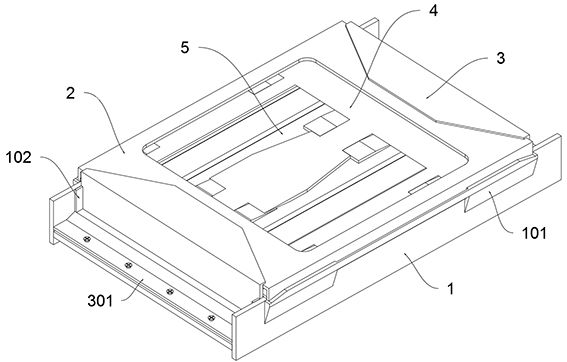

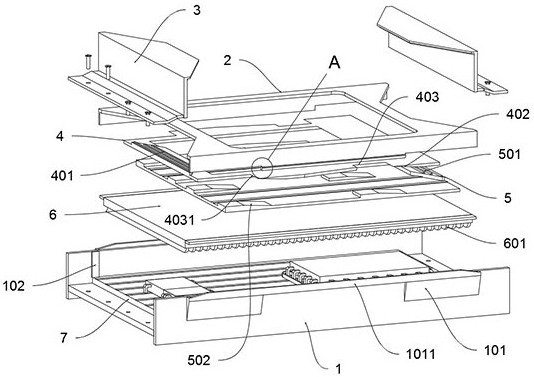

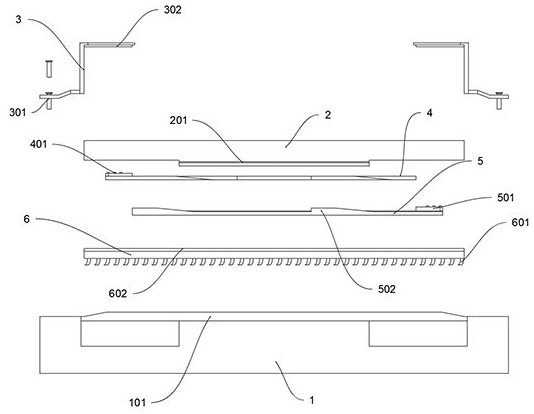

[0034] as attached figure 1 to attach Figure 10 Shown:

[0035]The present invention provides a packaging mechanism and packaging method for semiconductor substrates, including a packaging base 1; a semiconductor electrical substrate 7 is fixedly connected in the middle of the packaging base 1; above the body; the side packaging module 3 is provided with two groups, and the two groups are respectively located on the left side and the right side of the upper cover plate 2, and the bottom of the side packaging module 3 is fixedly connected to the upper surface of the bottom plate of the packaging seat 1 by screws; the upper clamping interlayer 4 It is located on the lower surface of the upper cover plate 2, and there is also a lower tightening interlayer 5 below the upper tightening interlayer 4, and the upper tightening interlayer 4 and the lower tightening interlayer 5 are all movably connected inside the upper cover plate 2; Both ends are connected to the two side walls of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More