Memory operation capability prediction method

A technology of operation ability and prediction method, applied in static memory, instrument, etc., can solve problems such as weakening price competitiveness, insufficient voltage accuracy, and inability to meet demand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

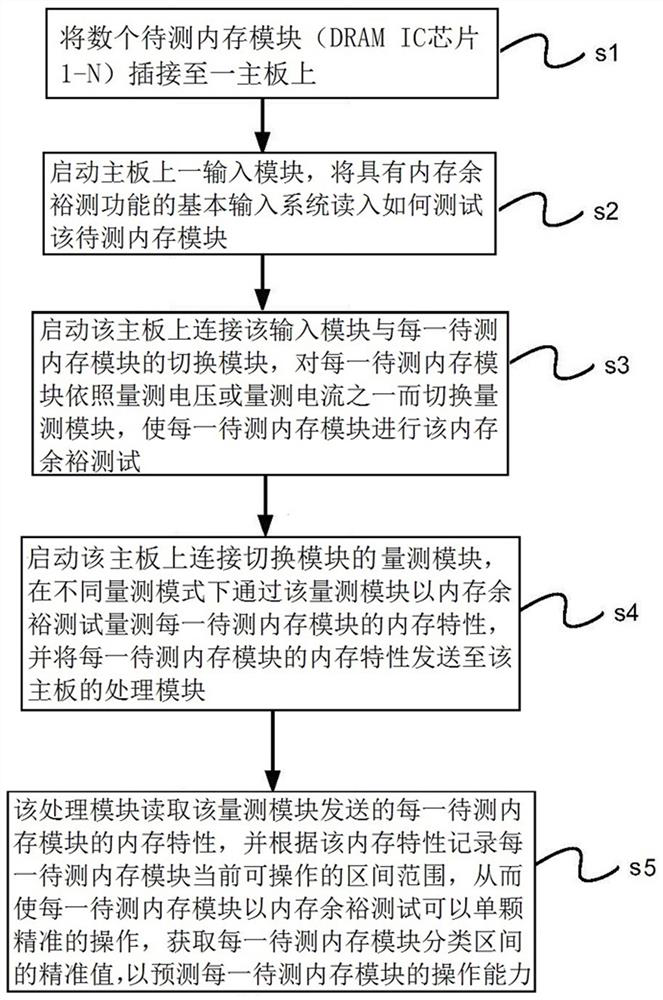

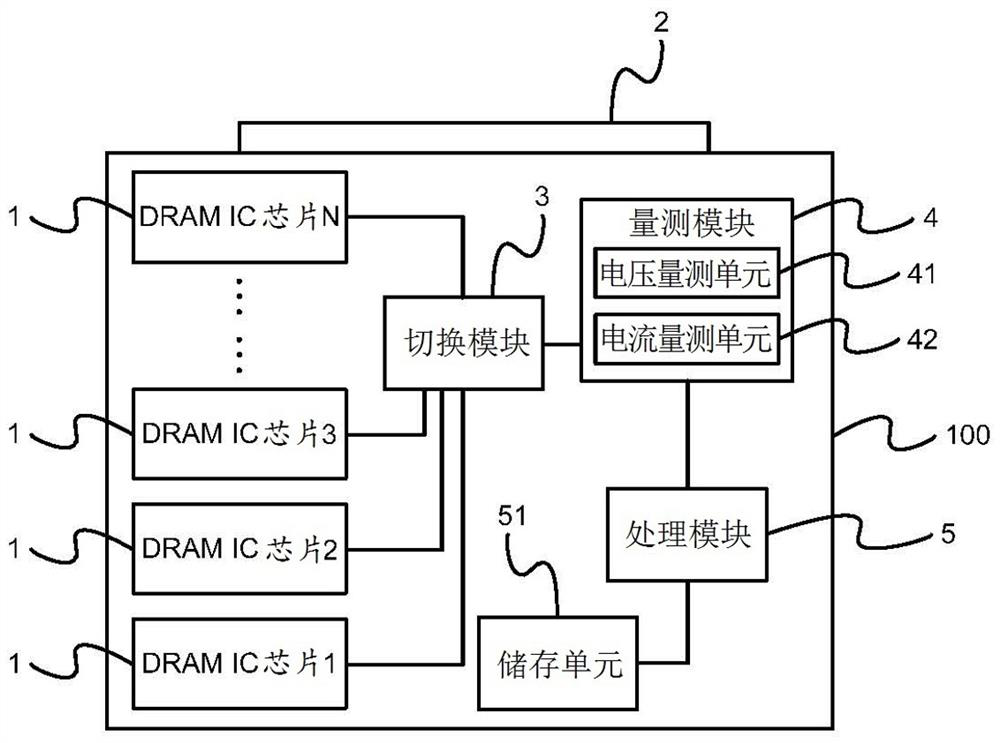

[0029] see figure 1 and figure 2 Shown are respectively a schematic flow chart of the present invention and a schematic block diagram of the present invention. As shown in the figure: the present invention is a memory operation ability prediction method, which is implemented by a memory operation ability prediction structure, which includes several memory modules under test (device under test, DUT) 1, input module 2, switching module 3, The measurement module 4 and the processing module 5 are formed. The memory operation capability prediction method of the present invention comprises the following steps:

[0030] Step 1 s1: Plug several memory modules under test (device under test, DUT) 1 onto a motherboard 100, each memory module 1 under test can be integrated with dynamic random access memory (DRAM) Circuit (integrated circuit, IC) chips are DRAM IC chip 1 to DRAM IC chip N.

[0031] Step 2 s2: start the input module 2 on the motherboard 100, and read the Basic Input / Ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More