Method for forming chip packaging structure

A chip packaging structure and bare chip technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of low yield rate of packaged products, improve product yield, prevent dielectric layer breakage, Avoid the effect of height gap

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0073] In order to make the above objects, features and advantages of the present invention more comprehensible, specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

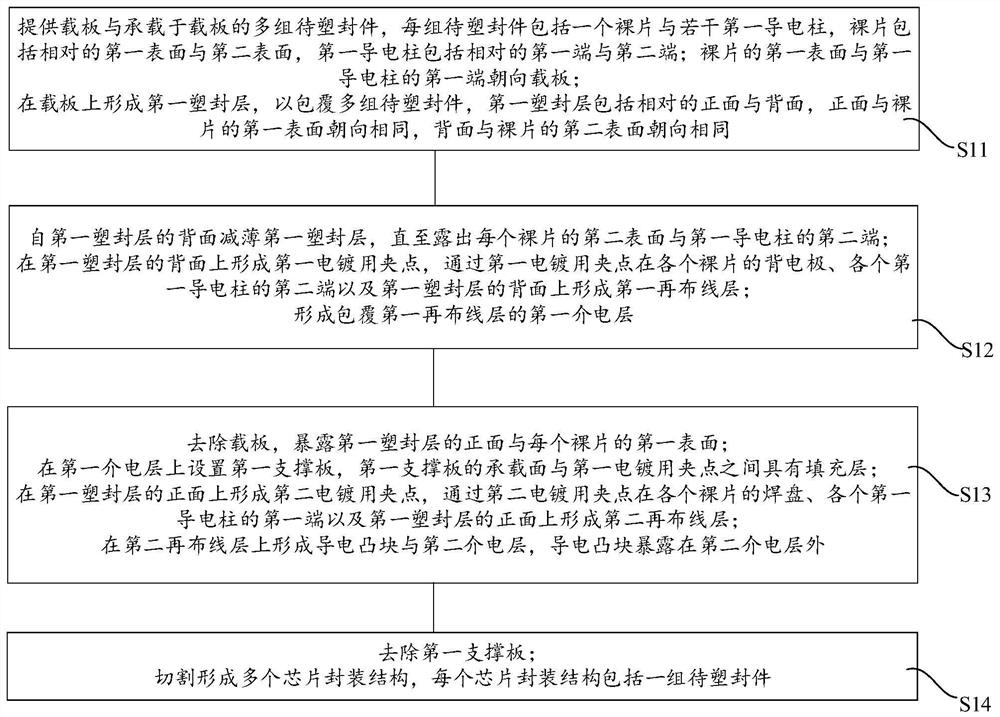

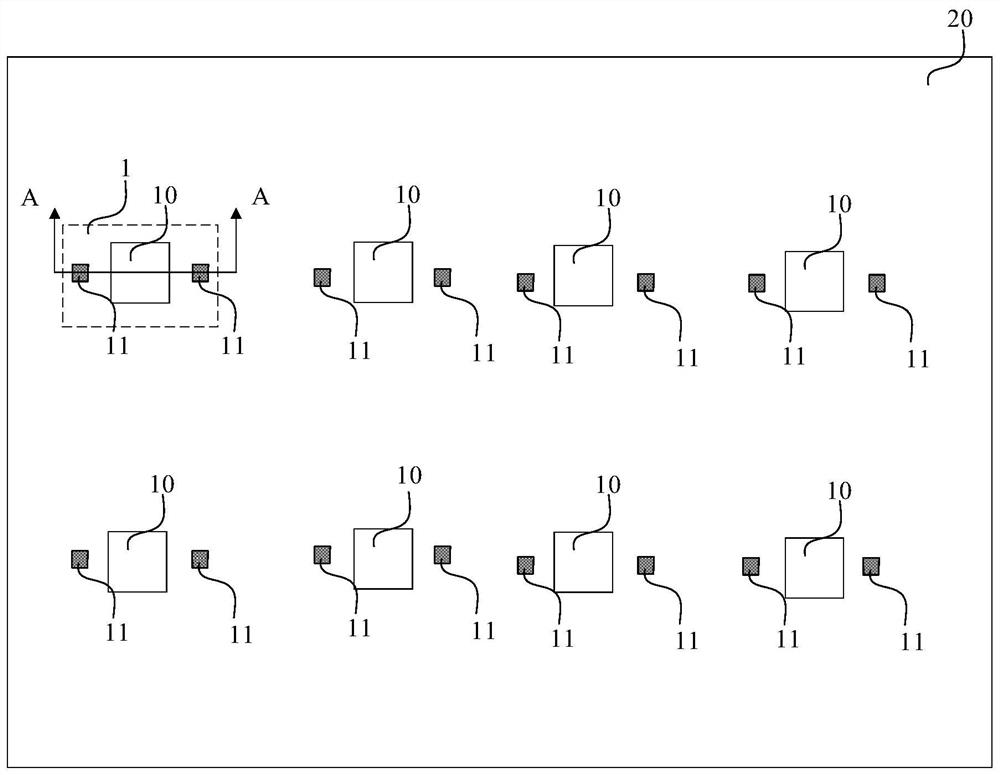

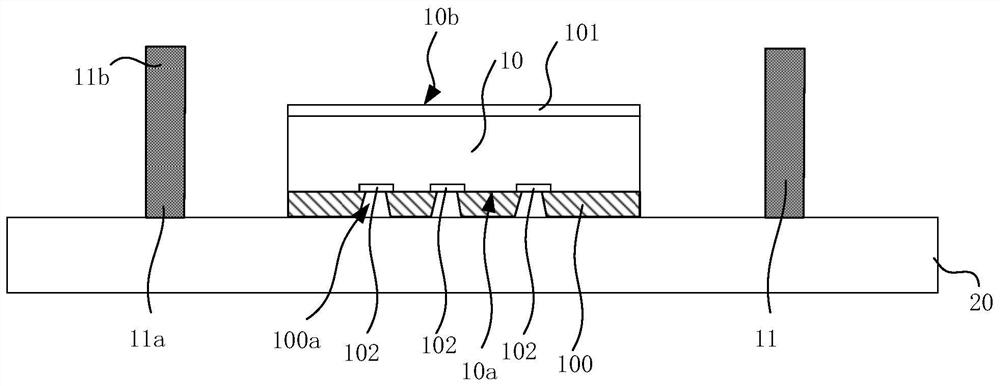

[0074] figure 1 is a flow chart of the method for forming the chip package structure according to the first embodiment of the present invention; Figure 2 to Figure 7 , Figure 9 yes figure 1 The schematic diagram of the intermediate structure corresponding to the process in . Figure 8 is a schematic diagram of the control structure.

[0075] First, refer to figure 1 Step S11 in, figure 2 and image 3 As shown, a carrier board 20 and multiple groups of parts to be molded 1 carried on the carrier board 20 are provided, each group of parts to be molded 1 includes a die 10 and a plurality of first conductive pillars 11, and the die 10 includes an opposite first surface 10a With the second surface 10b, the first conductive pillar 11 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com