Plesiochronous digital hierarchy low speed signal switching system digital phase-locked loop

A quasi-synchronous digital, hierarchical structure technology, applied in the direction of synchronous signal speed/phase control, digital transmission system, time division multiplexing system, etc., can solve the problems of incompatibility and increased cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

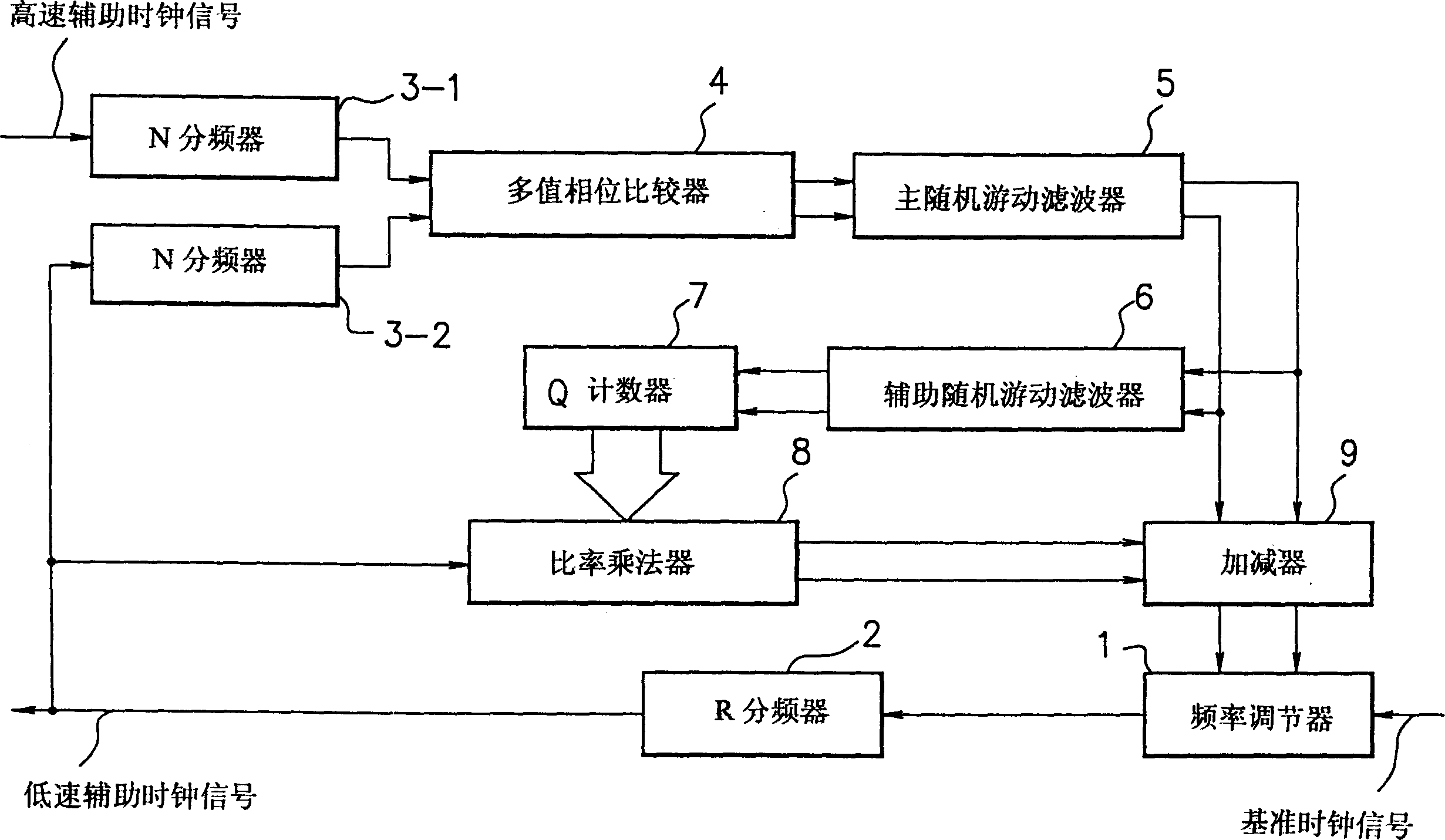

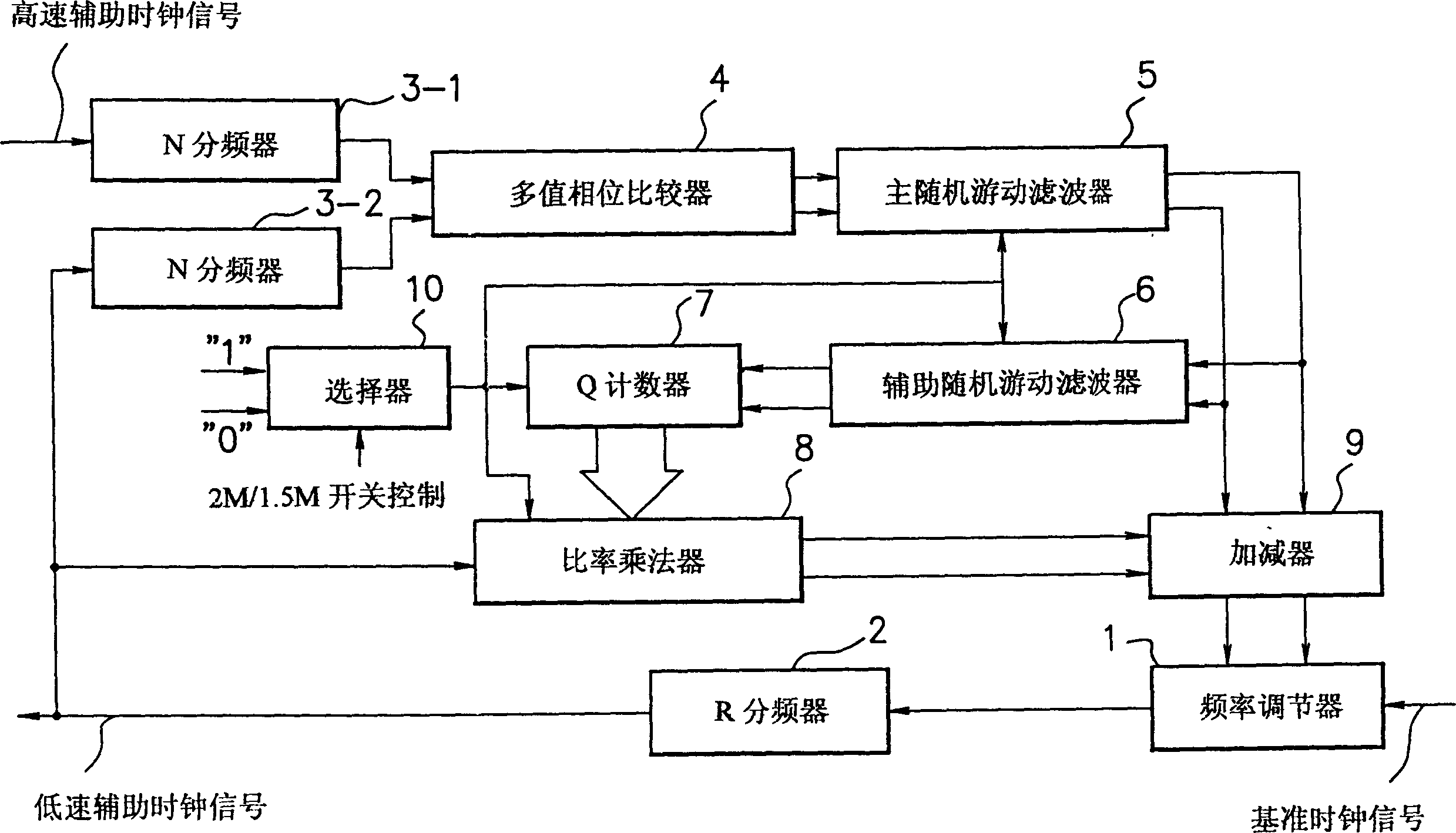

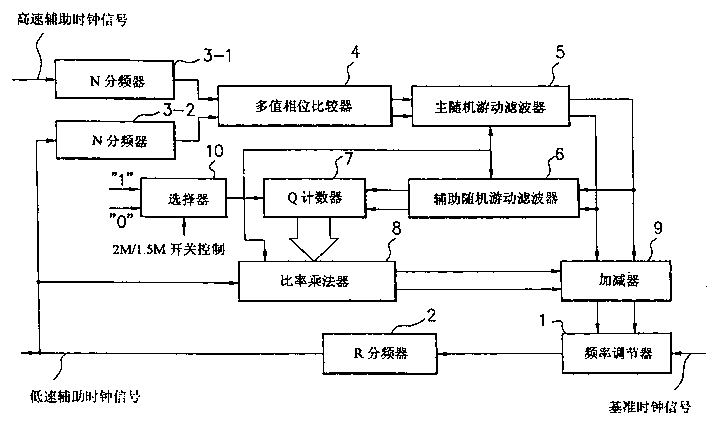

[0017] The following are the preferred embodiments of the present invention. The preferred embodiment of the present invention is a cleanup circuit using a full auxiliary system DPLL, which enables the main random walk filter ( figure 2 5 in ), the auxiliary random walk filter ( figure 2 6 in), a Q counter ( figure 2 7) of counting stages and ratio multipliers ( figure 2 8) in the ratio length will be based on the selector ( figure 2 In 10) the conversion signal changes, so that a required DPLL (digital phase-locked loop) circuit for various PDH low-speed signal interfaces can be obtained.

[0018] According to the embodiment of the present invention, the counter value for determining the system parameters of the DPLL (Digital Phase Locked Loop) can be set to the respective parameters of the 2M interface and the 1.5M interface by switching through the selector. It is not necessary to separately design DPLL circuits suitable for 2M cards and 1.5M cards. The operation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More