Parallel pipelined decompression device for FPGA configuration code stream

A pipelined, decompression technology, applied in the field of communication, to achieve the effect of improving device parallelism, simplifying implementation complexity, and decompressing efficiently

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

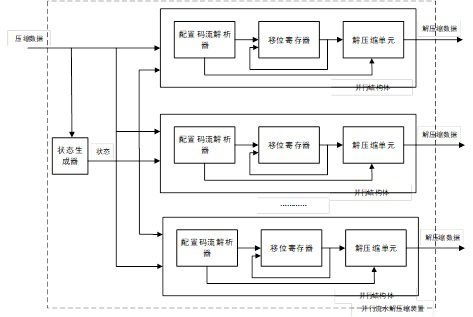

[0019] This embodiment is a parallel pipeline decompression device for FPGA configuration code stream, such as figure 1 , as shown, including a state generator and some parallel structures; the state generator is connected with each parallel structure, and the parallel structure receives the compressed data for configuring the FPGA;

[0020] The state generator is used to control the configuration code stream data through the chip selection enabling control mode for the compressed data; send state information, including idle state, receiving packet header state, decompression state, and completion state; The controller of the device sends system information, and the system information includes counting information in the state of receiving the packet header, counting information in the decompressed state, and chip selection control information for configuring the compressed code stream;

[0021] The parallel structure includes a configuration code stream parser, a shift regist...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More