USB OTG test method

A test method and technology of a chip to be tested, which are applied in the field of USBOTG testing, can solve problems such as untested USBhost function and incomplete USBOTG function test, and achieve the effect of meeting the requirements of automatic chip testing, simple method, and convenient operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

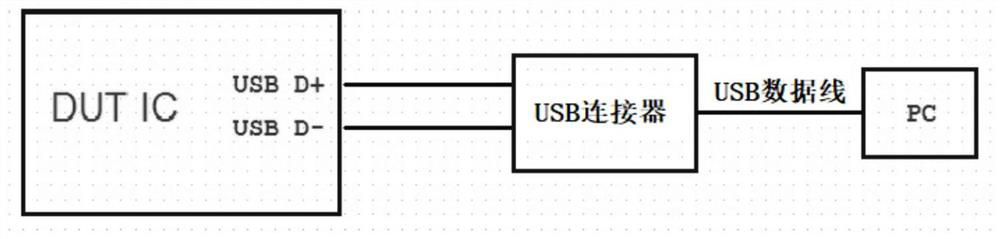

Image

Examples

Embodiment Construction

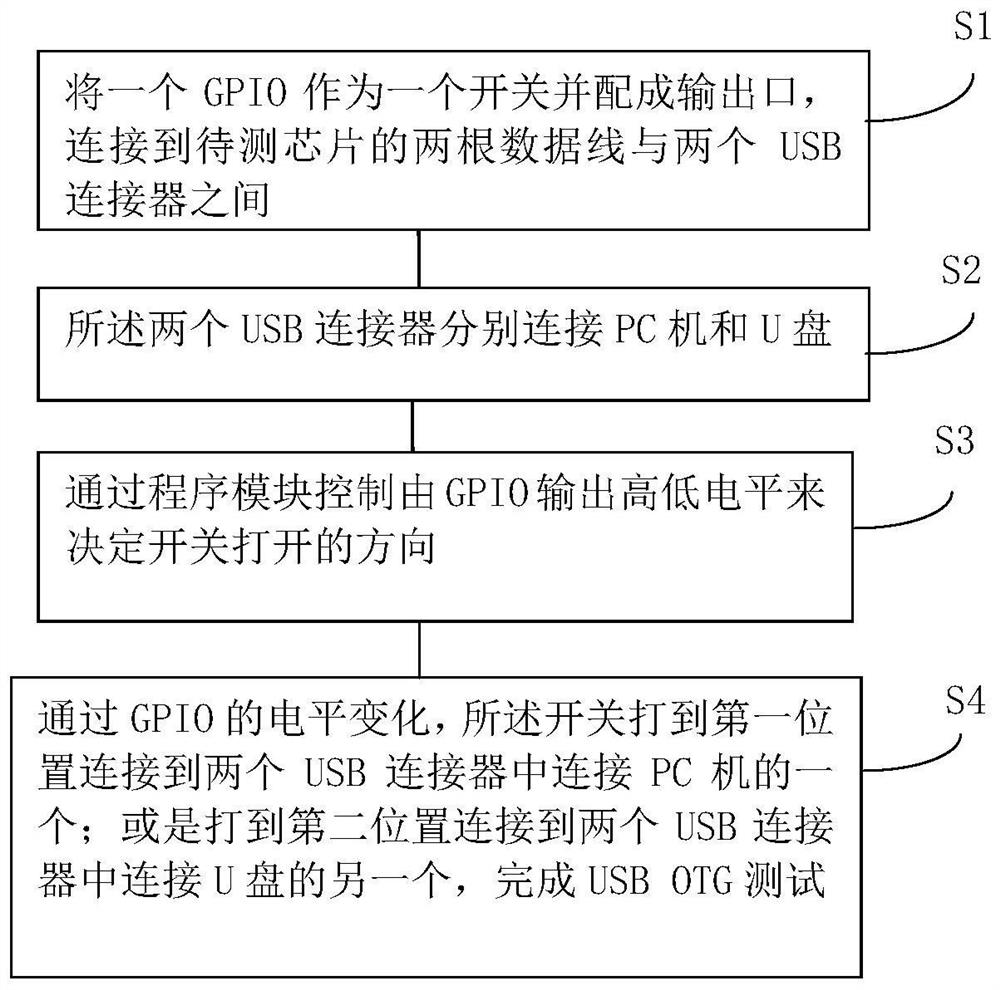

[0032] In order to understand the technical content and advantages of the present invention more clearly, the present invention will be further described in detail in conjunction with the accompanying drawings.

[0033] Such as figure 2 Shown, the present invention relates to a kind of USB OTG test method, described method comprises the following steps:

[0034] S1, use a GPIO as a switch and configure it as an output port, and connect it between the two data lines of the chip under test and the two USB connectors;

[0035] S2, the two USB connectors are respectively connected to the PC and the U disk;

[0036] S3, through the program module to control the high and low level output by GPIO to determine the direction of the switch opening;

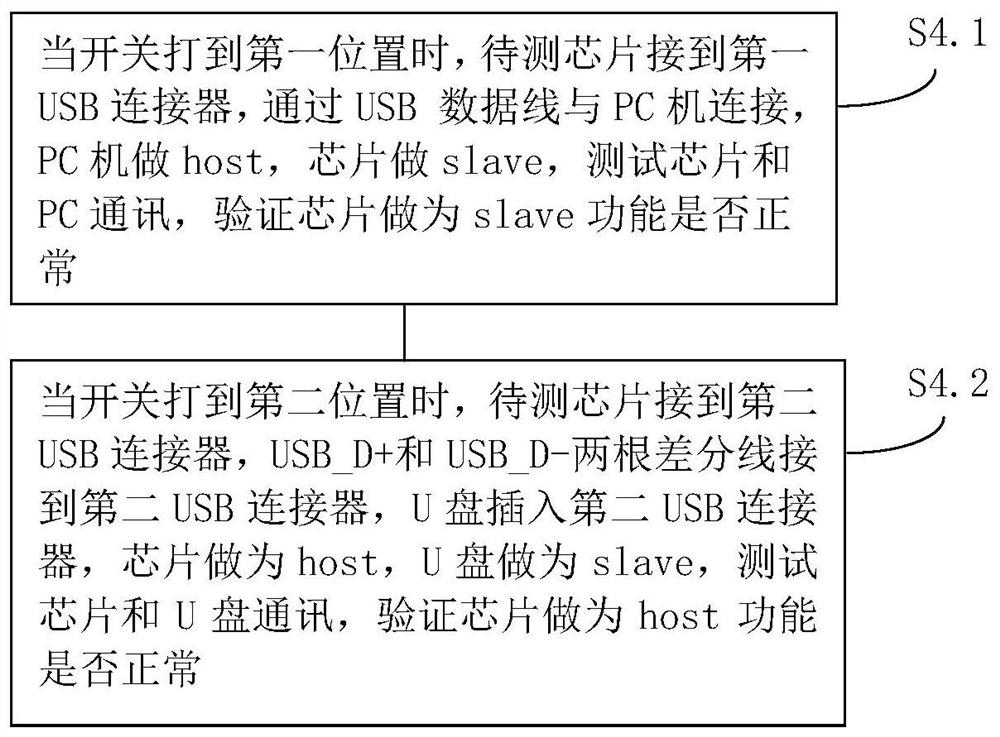

[0037] S4, through the level change of GPIO, the switch is connected to the first position to connect to one of the two USB connectors connected to the PC; or to the second position to connect to the one connected to the U disk in the tw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More