Automatic chip alignment device and alignment method

An automatic alignment and chip technology, which is applied in the direction of measuring devices, instruments, electronic circuit testing, etc., can solve the problems of poor surface flatness of the test bench, the influence of chip test results, and the impact of chip conductivity and thermal conductivity, etc., to achieve electrical conductivity It has the effect of stabilizing thermal conductivity, improving test accuracy and ensuring accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

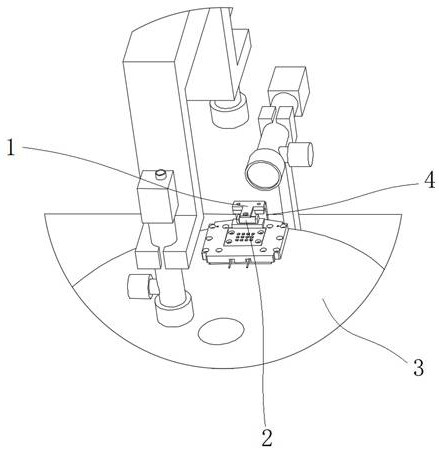

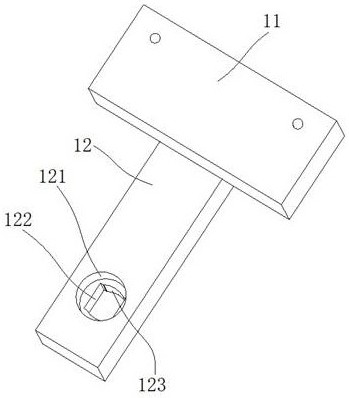

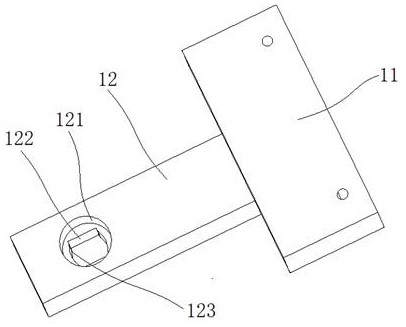

[0040] This embodiment provides a specific implementation of the chip automatic alignment device, such as figure 1 , figure 2 , image 3 and Figure 4 As shown, the alignment member 1 is installed on the moving mechanism 4, and the moving mechanism 4 can drive the alignment member 1 to move in the first direction and / or the second direction above the plane where the slide table 2 is located. The second directions are perpendicular to each other, wherein the plane where the slide table 2 is located is the plane where chips are placed on the slide table 2 , and the plane where the alignment member 1 moves is parallel to the plane where the slide table 2 is located. The alignment member 1 has a correction plate 12, which is set correspondingly to the slide table 2. The correction plate 12 is set above the slide table 2. A first hole 122 is opened on the correction plate 12, and the chip can pass through the first hole 122. The holes 122 drop onto the slide table 2; a group of...

Embodiment 2

[0055] This embodiment provides a specific implementation of the alignment method, which is implemented by using the chip automatic alignment device in Example 1, including the following steps: placing the chip on the loading table 2, and the calibration plate 12 pushes the chip on the loading table. The chip stage 2 is moved along the first direction and / or the second direction until it reaches a predetermined position, and the luminous point of the chip corresponds to and does not touch the escape groove 123 on the calibration plate 12 during the movement; wherein, the first direction and The second directions are perpendicular to each other.

[0056] The calibration plate 12 is controlled by the moving mechanism 4 to push the chip to move along the first direction and the second direction on the slide table 2. During the movement, the light-emitting point on the chip is in the avoidance groove 123; during the movement, it passes through the first hole. Body 122 adjusts the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More