Wallace tree compressor based on Xilinx FPGA primitive

A wallace tree and compressor technology, applied in the field of programmable logic chip applications, can solve problems such as different implementation methods, and achieve the effect of reducing overall delay and hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments to facilitate a clear understanding of the present invention, but they do not limit the present invention.

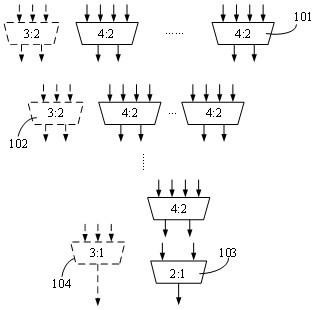

[0046] like image 3 Shown, a kind of Wallace tree compressor based on Xilinx FPGA primitive language of the present invention comprises the tree type compression structure and the summation unit that are formed according to the hierarchical distribution by a plurality of compression units, and the tree type compression structure compresses a plurality of binary number input to Two or three outputs, the summation module adds the compression results and outputs the final result; after multiple binary numbers are compressed by multiple compression units of the tree compression structure, the underlying compression unit outputs the compression results; the summation module compares the compression results Add to get the final result....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More