FPGA time sequence simulation verification method and device based on MATLAB

A simulation verification and timing technology, applied in the field of FPGA simulation verification, can solve problems such as unfavorable airworthiness compliance review, complicated workload, reduced efficiency and accuracy, etc., to reduce the workload of verification personnel, reduce the risk of manual errors, and guarantee Effects of Airworthiness Compliance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] Embodiments of the technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings. The following examples are only used to illustrate the technical solution of the present invention more clearly, so they are only examples, and should not be used to limit the protection scope of the present invention.

[0044] It should be noted that, unless otherwise specified, the technical terms or scientific terms used in this application shall have the usual meanings understood by those skilled in the art to which the present invention belongs.

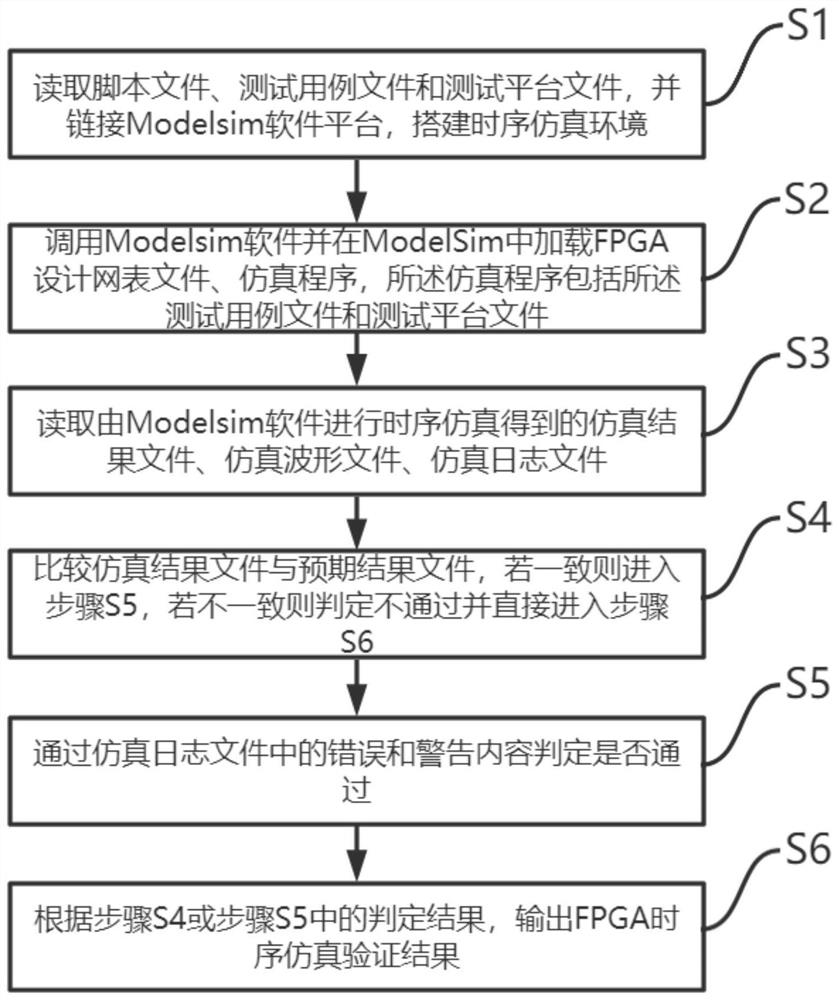

[0045] figure 1 A kind of step flow chart of the FPGA timing simulation verifier based on MATLAB provided by the embodiment of the present invention, see figure 1 , the method includes the following steps:

[0046]S1: Read the script file, test case file and test platform file, and link the Modelsim software platform to build a timing simulation environment.

[0047] After the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com