Super junction semiconductor device and forming method thereof

A super-junction semiconductor and device technology, applied in the field of super-junction semiconductor devices and their formation, can solve the problems of N-column and P-column charge balance shift, unstable process conditions, poor stability, etc., to improve the withstand voltage performance and finished products efficiency, improving process instability, and improving the effect of poor stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

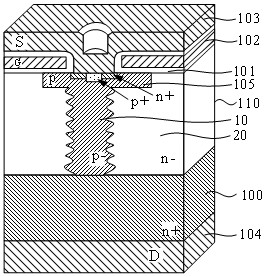

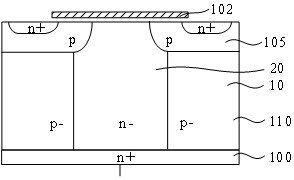

[0027] The super junction semiconductor device and its forming method of the present invention will be further described in detail below with reference to the drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be understood that the drawings in the description are all in very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention. It will be understood that the spatially relative terms are intended to encompass different orientations of the device in use or operation in addition to the orientation depicted in the figures. For example, if a structure in the figures is inverted or otherwise positioned differently (eg, rotated), the exemplary term "on" could also include "below" and other orientational relationships.

[0028] The method for forming a super-junction semiconduct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More