Formation method of semiconductor structure

A semiconductor and gate structure technology, which is applied in the field of semiconductor structure formation, can solve problems such as poor performance, and achieve the effects of avoiding etching loss, reducing etching loss, and improving quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] It can be seen from the background art that the performance of the existing semiconductor structure needs to be improved.

[0034] see Figure 1 to Figure 4 , a method for forming a semiconductor structure, comprising:

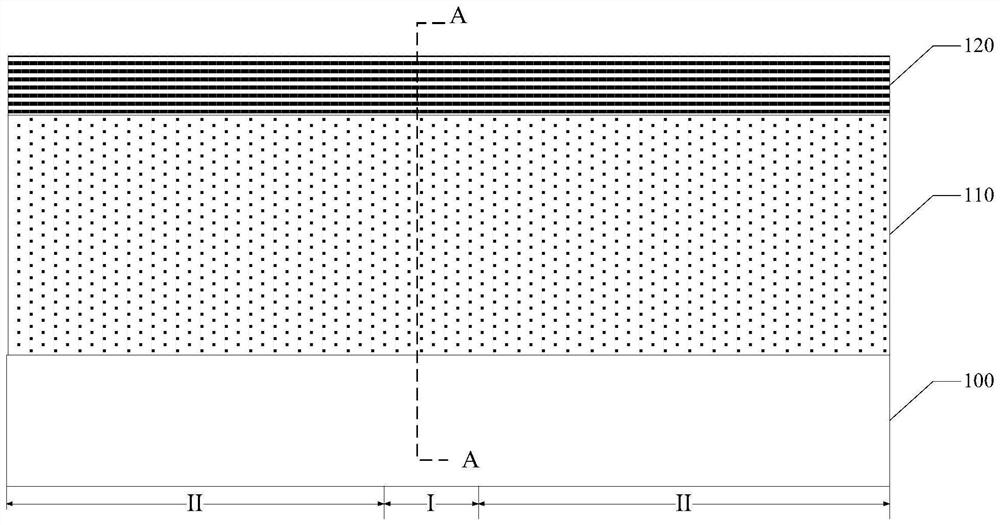

[0035] refer to figure 1 , provide a substrate 100, the substrate includes a gate cutting region I and a device region II located on both sides of the gate cutting region I; a gate material layer 110 is formed on the gate cutting region I and the device region II and is located on the gate a patterned etched hard mask layer 120 on the pole material layer 110;

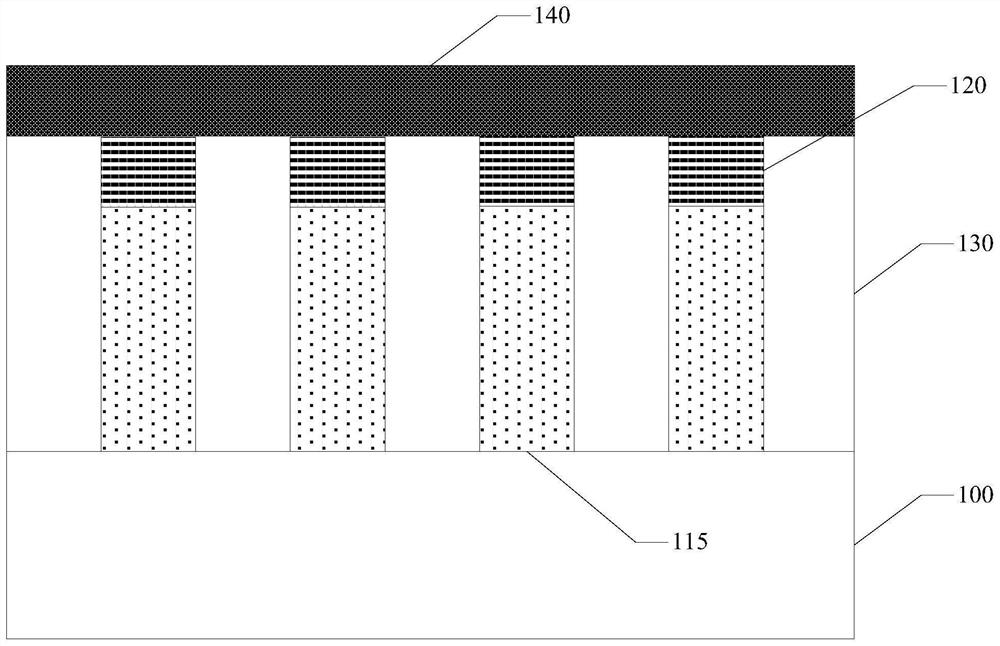

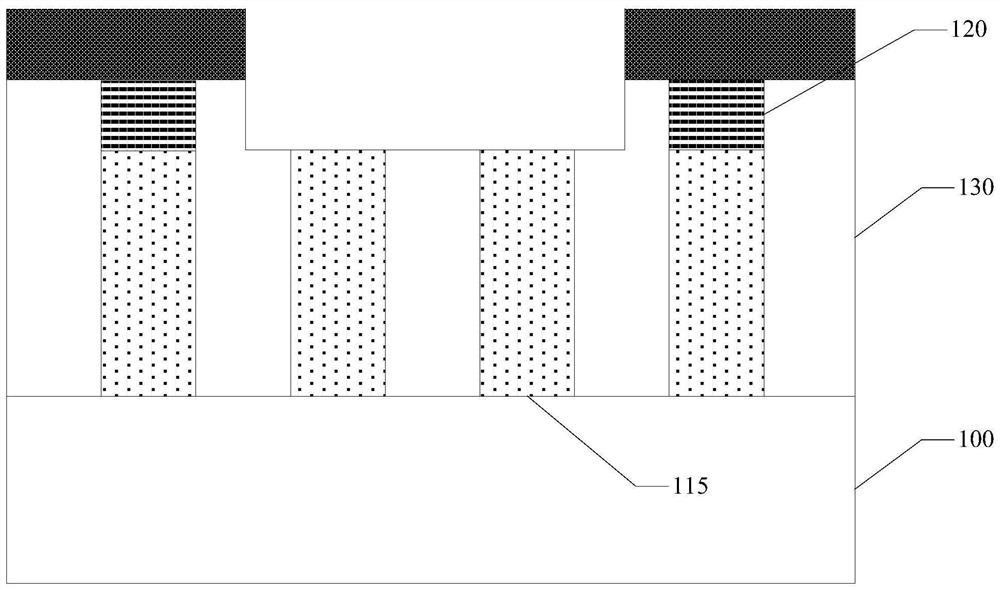

[0036] figure 2 yes figure 1 Schematic diagram of the section along the AA line. see figure 2 , using the patterned etched hard mask layer 120 as a mask to etch the gate material layer 110 to form a plurality of discrete gate structures 115; after forming the gate structures 115, a covering The sidewall of the gate structure 115 and the dielectric layer 130 for etching the sidewall of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More