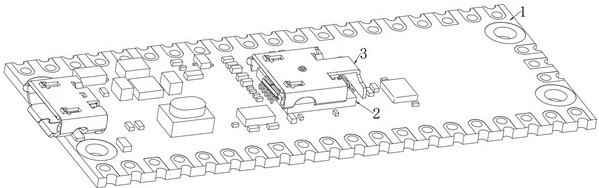

A packaging structure for power management chips

A power management chip and chip packaging technology, which is applied in the direction of circuits, electrical components, electric solid devices, etc., can solve problems such as poor heat dissipation, package damage, maintenance and disassembly troubles, and achieve the effect of maintaining stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

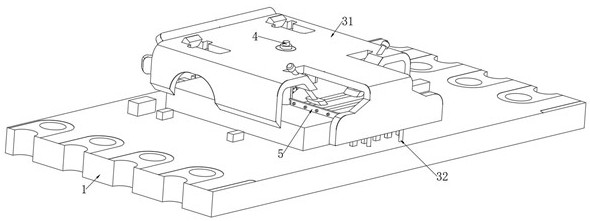

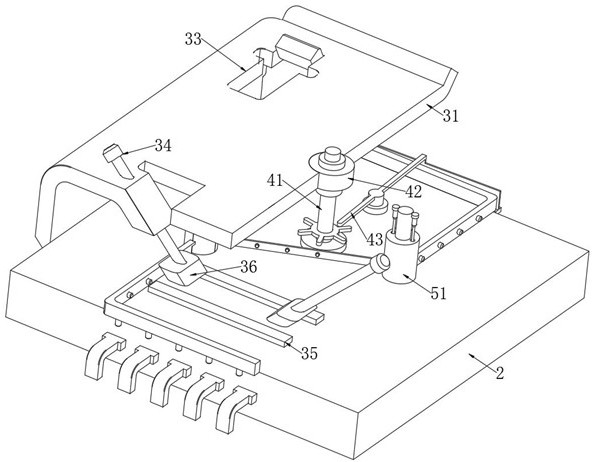

Embodiment Construction

[0027] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. The detailed description of the embodiments of the present invention provided in the present invention is not intended to limit the scope of the claimed invention, but only represents selected embodiments of the present invention, based on the embodiments of the present invention, those of ordinary skill in the art without All other embodiments obtained under the premise of creative work belong to the protection scope of the present invention.

[0028] In the description of the present invention, it should be noted that the orientation or positional relationship indicated by the terms "center", "upper", "lower", "vertical", "horizontal", "inner" and "ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More