Device and method for realizing burning of multiple FPGAs based on CPLD chip

A chip and connector technology, applied in the field of FPGA chip programming, can solve the problems of limited driving capability of the drive source, affecting the programming speed, and programming failure, etc., to avoid damage to the FPGA chip, avoid stability degradation, and avoid PCB wiring. simple effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The technical solutions of the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings of the present invention.

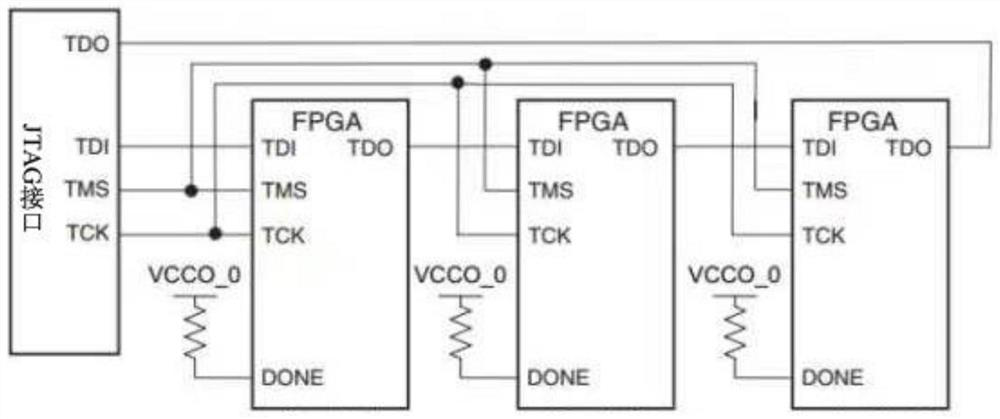

[0024] In the prior art, a plurality of FPGA chips are connected in a daisy chain (Dasiy Chain) form during programming, and this connection method not only easily affects the signal integrity, but also easily causes problems such as misoperation and damage to the FPGA chip. The present invention realizes the programming of multiple FPGA (Field-Programmable Gate Array, Field Programmable Gate Array) chips by adopting CPLD (Complex Programmable Logic Device) chips. Signal integrity, at the same time, can avoid damage and misoperation of the FPGA chip, and improve the stability of programming.

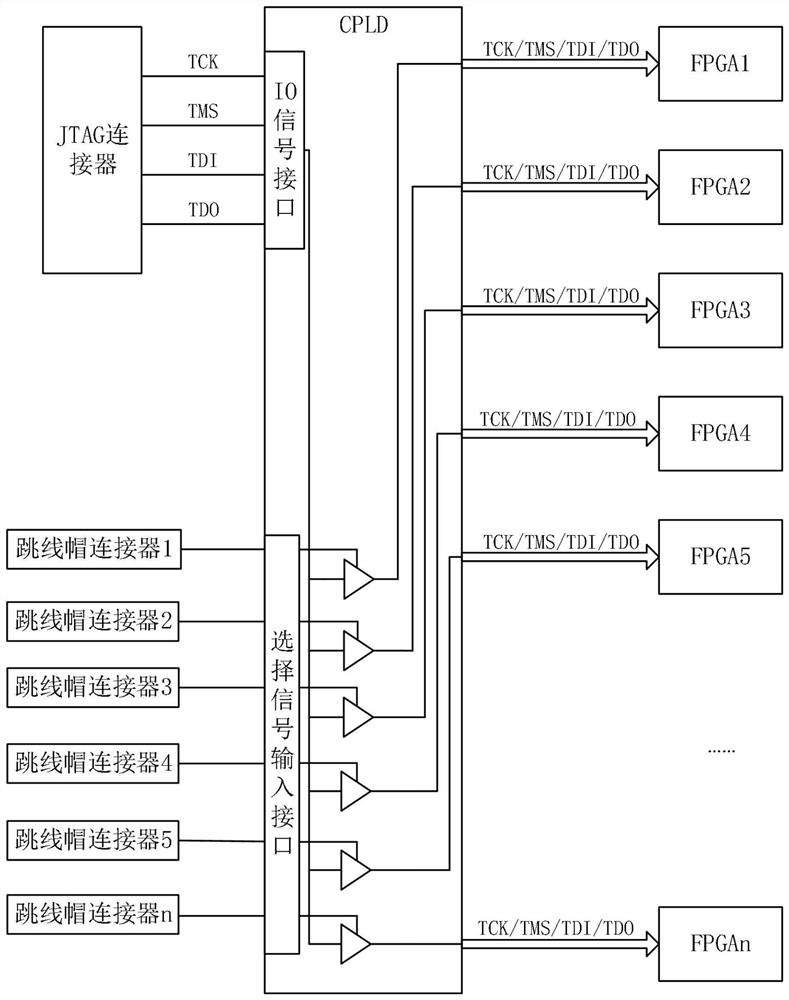

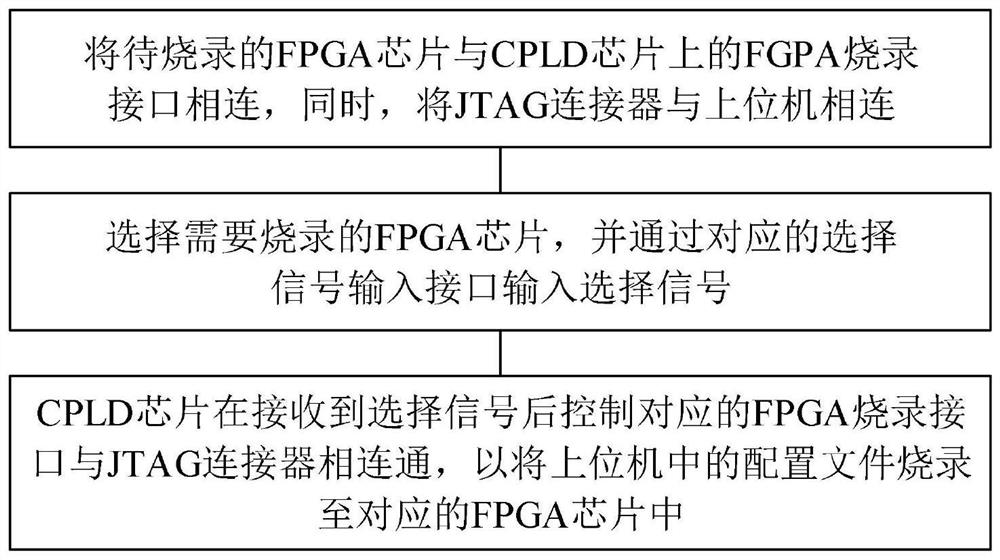

[0025] like figure 2 As shown, it is an apparatus for realizing programming of multiple FPGAs based on a CPLD chip disclosed in the present invention, including a JTAG (Joint Test Action Group, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More