PCIE equipment fault processing method and device

A technology of equipment faults and processing methods, which is applied in the server field, can solve the problems of unable to interrupt the propagation of PCIE fault information, and achieve the effects of meeting fault processing requirements, enhancing stability, and reducing downtime

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

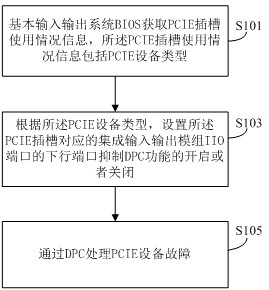

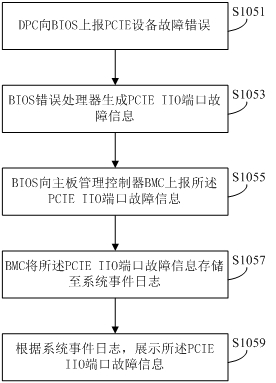

[0063] Please refer to figure 1 , which is a flow chart of the PCIE device fault handling method of the present application. In this embodiment, the method may include the following steps:

[0064] Step S101: The basic input and output system BIOS obtains the usage information of the PCIE slot, and the usage information of the PCIE slot includes the type of the PCIE device.

[0065] The Basic Input Output System (BIOS) is an industry-standard firmware interface. It is the first software loaded when the computer is started. It can read and write the specific information of the system settings from the CMOS.

[0066] PCIE (peripheral component interconnect express) is a high-speed serial computer expansion bus standard. It belongs to high-speed serial point-to-point dual-channel high-bandwidth transmission. The connected devices allocate exclusive channel bandwidth and do not share bus bandwidth. It supports hot plug and error Reporting and other functions.

[0067] PCIE devi...

no. 2 example

[0102] In the foregoing embodiments, a PCIE device fault handling method is provided, and correspondingly, the present application also provides a PCIE device fault handling device. The device corresponds to the embodiment of the above-mentioned method. Since the device embodiment is basically similar to the method embodiment, the description is relatively simple, and for relevant parts, refer to the part of the description of the method embodiment. The device embodiments described below are illustrative only.

[0103] The present application further provides a PCIE device fault processing device, including: a PCIE information acquisition unit, a dynamic enabling DPC unit, and a DPC processing unit. Wherein, the PCIE information acquisition unit is used to obtain the PCIE slot usage information when the basic input and output system BIOS is initialized, and the PCIE slot usage information includes the PCIE device type; the dynamic enabling DPC unit is used for according to th...

no. 3 example

[0113]In the above embodiments, a PCIE device fault handling method is provided, and correspondingly, the present application also provides a basic input and output system. The device corresponds to the embodiment of the above-mentioned method. Since the device embodiment is basically similar to the method embodiment, the description is relatively simple, and for relevant parts, refer to the part of the description of the method embodiment. The device embodiments described below are illustrative only.

[0114] A kind of basic input output system of the present embodiment, comprises: initialization module, is used to obtain PCIE slot usage information, and described PCIE slot usage information includes PCIE device type; According to described PCIE device type, set described PCIE The downlink port of the IIO port of the integrated input and output module corresponding to the slot suppresses the opening or closing of the DPC function, so that the PCIE device failure can be handl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More