Formation method of semiconductor structure

A semiconductor and isolation structure technology, applied in the field of semiconductor structure formation, can solve problems such as poor performance of semiconductor structures, and achieve the effects of performance improvement, reduction of dummy gate structure residues, and performance improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] As described in the background art, the semiconductor structures formed by the gate cut-off process in the prior art have poor performance. The following will be described in detail with reference to the accompanying drawings.

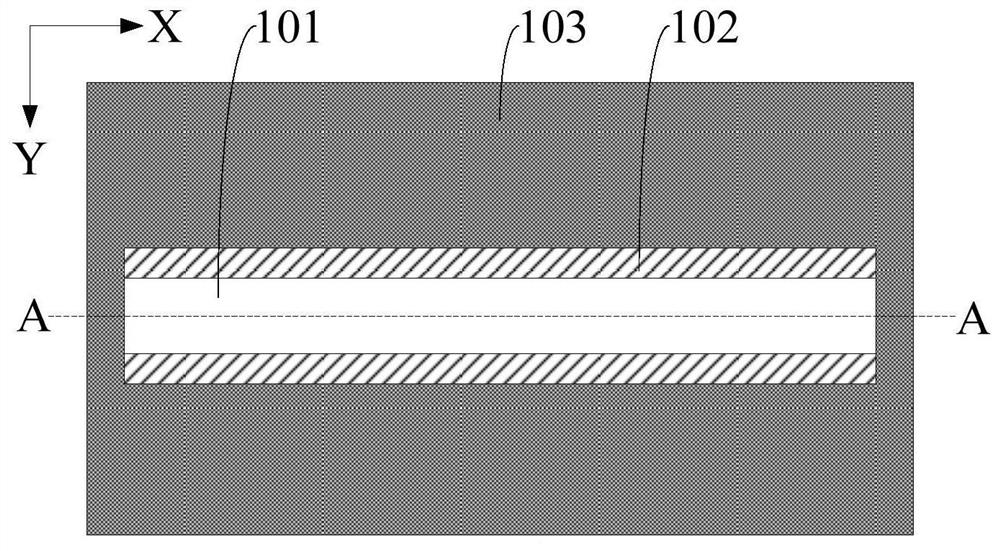

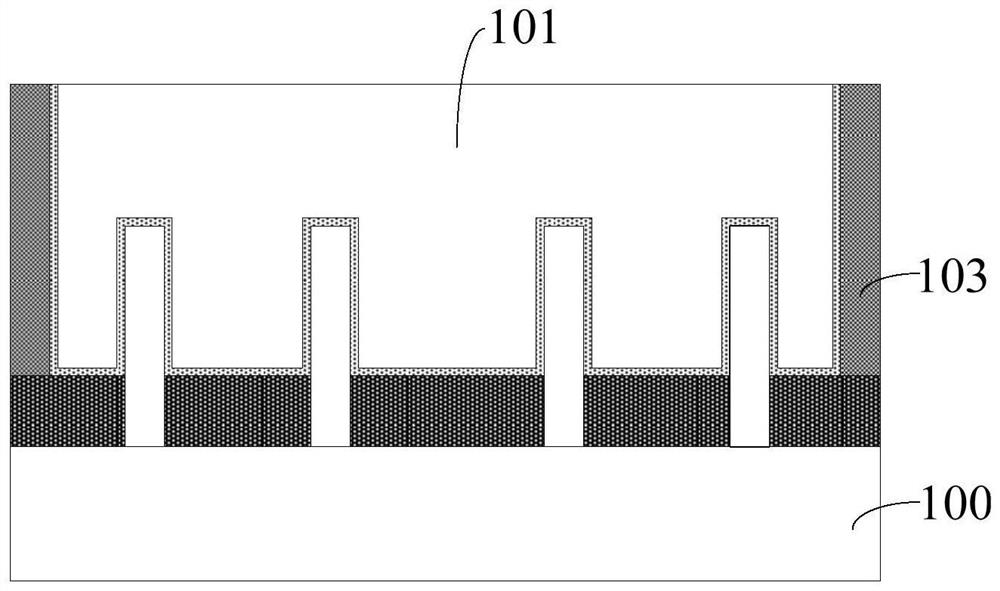

[0031] Please refer to figure 1 and figure 2 , figure 2 Yes figure 1 A schematic cross-sectional view along the line A-A in the middle, a substrate 100 is provided; an initial dummy gate structure 101 is formed on the substrate 100 , and the initial dummy gate structure 101 extends along the first direction X; on the side of the initial dummy gate structure 101 forming a spacer 102 on the wall; forming a dielectric layer 103 on the substrate 100, the dielectric layer 103 covering the initial dummy gate structure 101 and the spacer 102, and the dielectric layer 103 exposing the initial The top surface of the dummy gate structure 102 and the spacers 103 .

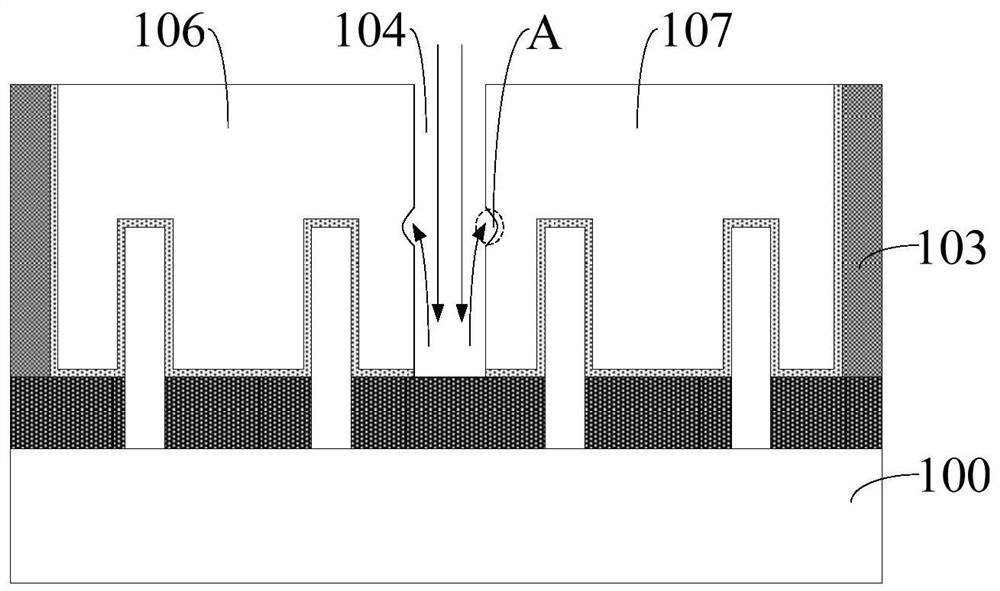

[0032] Please refer to image 3 , image 3 and figure 2 The view direction is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More